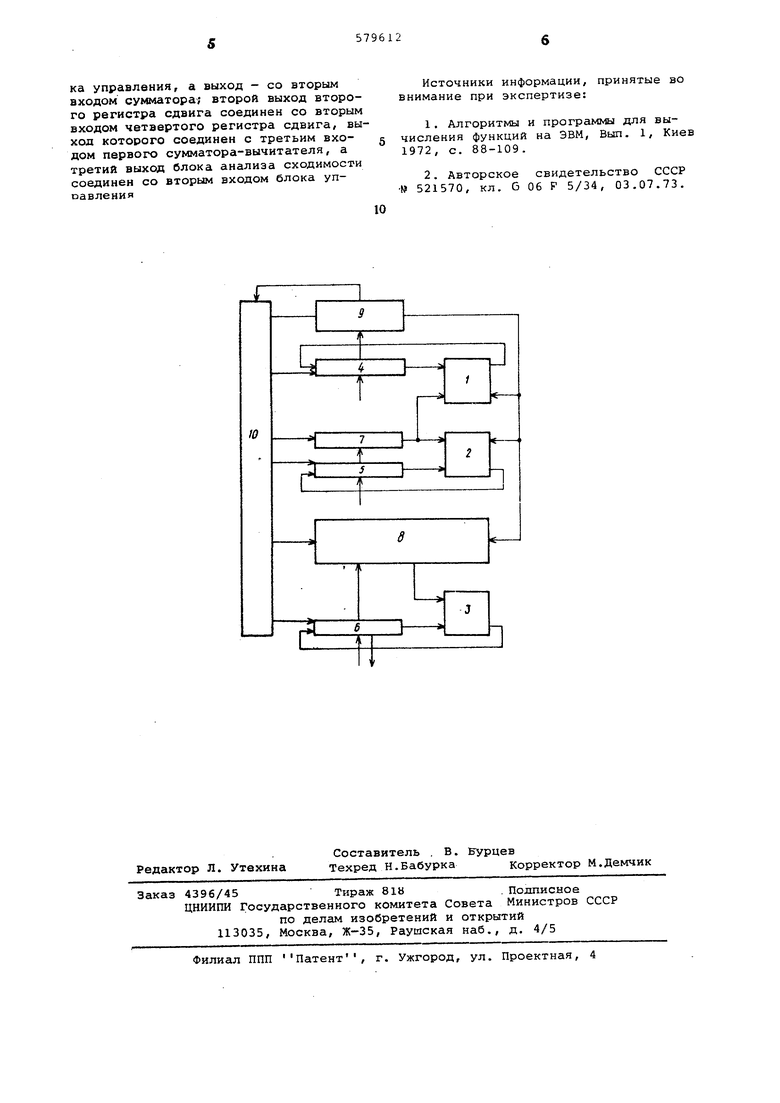

Оно содержит первый 1 и второй сумматоры-вычитатели, сумматор 3, тыре регистра сдвига 4-7, блок 8 з дания показателя степени, блок ана аа сходимости 9 и блок управления Процесс вычисления функции вид УХ основан на одновременном решен итерационном процессе системы разн ных рекуррентных соотношений, напр мер, для двоичной системы счислени V«-X , V,,,i.) -H Xji2 V - О r-t-l при Vj.; 0 0,l,...,n J,ji SlgnVjj npw Vj,i.0 ,Ui Xji + 4iiXii2- X -1 o-Y YjM.in jifAiiZ, где Aj{ равно ; для К «2 Aii«2iiUj{2-2 -b2 j; АляК 3 Aj,() + для Ai,-Zi,,(2-2 2 -2 K2-2 -2 2 2- iJ Aii Ziitvjj(2-2 Z -2 +2-2 + .,+2-2 2H2 -2 +-2-2 b2 -2 j;

Цикл вычисления функции состоит из П + 1 основных итераций, где п - число разрядов одного из аргументов. Каждая итерация выполняется последователь но за n-t-тп тактов, где m - число дополнительных разрядов для компенсации погрешности окружения чисел при рдвиге.

Устройство работает следующим образом.

Первоначально в регистр сдвига 4 заносится дополнительный код аргумента X, в регистр сдвига 5(и соответственно в регистр сдвига 7) - код ар- .. гумента X, а в регистр сдвига б - код аргумента У. Включается генератор тактовых (сдвигающих) импульсов в блоке управления 10. В любой -и итерации с выхода блока управления 10 вы; ается серия (последовательность) тактовых импульсов для сдвига содержимого регистра сдвига 7 и значенийZjt в блоке 8 задания показателя степени, а также продвижения содержимого регистров сдвига 4-7 на входы сумматоров-вычита- телей 1, 2 и сумматора 3. Результаты каждой итерации записываются с выходов сумматоров-вычитателей 1, 2 и сумматора 3 младшими разрядами вперед в освобождающиеся при сдвиге старшие раз- вОряды регистров сдвига 4-6 и продвигаются в сторону младших разрядов. В конце каждой итерации в блоке анализа сходимости 9 определяется цифра псевдочастного , которая выдается gg

Формула изобретения

Устройство для вычисления функции вида УХ ,содержащее регистры сдвига, блок управления, четыре выхода которого соединены соответственно с первыми входами регистров сдвига, два сумматора-вычитателя и сумматор, выходы которых соединены соответственно со вторыми входами первого, второго и третьего регистров сдвига, первые выхды которых соединены соответственно с первыми входами первого и второго сумматоров-вычитателей и сумматора, блок анализа сходимости, вход которого соединен со вторым выходом первого регистра сдвига, первый выход - с первым входом блока управления, а второй выход - со вторыми входами первого и второго сумматоров-вычитателей, при этом выход четвертого регистра . сдвига соединен с третьим входом второго сумматора-вычитателя, о т л и ч ающе ее я тем, что, с целью расширения функциональных возможностей устройства благодаря обеспечению возможности возведения в любую целую степень, оно содержит блок задания показателя степени, первый вход которог соединен со вторым выходом третьего регистра сдвига, второй вход - со вторым выходом блока анализа сходимости, третий вход - с пятым выходом блосо второго выхода этого блока на вторые входы сумматоров-вычитателей 1,2 и блока 8 задания показателя степени. ,-г+1 сумматор-вычитатель 1 работает в режиме вычитания, а сумматорвычитатель 2 - в режиме сложения. При cjjj -1 их режим работы изменяется на обратный. Блок анализа сходимости 9 определяет изменение знака величины tj:, и при перемене знака выдает со своего третьего выхода на второй вход блока управления 10 сигнал перехода к следующему значению величины J . Когда содержимое регистра сдвига 4 становится равным нулю, с первого выхода блока анализа сходимости 9 выдается сигнал останова в блок управления 10 и последний прекращает выдавать тактовые импульсы на следующей итерации, так как процесс вычисления закончен и в регистре сдвига 6 содержится значение искомой функции. Максимальное время вычисления указанной функции в тактах равноТ д п(я + №) +W . Однако для большинства значений аргумента X время вычисления Т Т макс Изобретение позволяет расширить класс вычисляемых функций с помощью одного устройства, что повышает эффективность его применения.

ка управления, а выход - со вторым входом сумматора; второй выход второго регистра сдвига соединен со вторым входом четвертого регистра сдвига, выход которого соединен с третьим входом первого сумматора-вычитателя, а третий выход блока анализа сходимости соединен со вторым входом блока упоавления

Источники информации, принятые во внимание при экспертизе:

1.Алгоритмы и программы для вычисления функций на ЭВМ, Вып. 1, Киев 1972, с. 88-109.

2.Авторское свидетельство СССР И 521570, кл. G 06 F 5/34, 03.07.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1975 |

|

SU586458A1 |

| Устройство для возведения в степень | 1975 |

|

SU616628A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

Авторы

Даты

1977-11-05—Публикация

1975-12-01—Подача