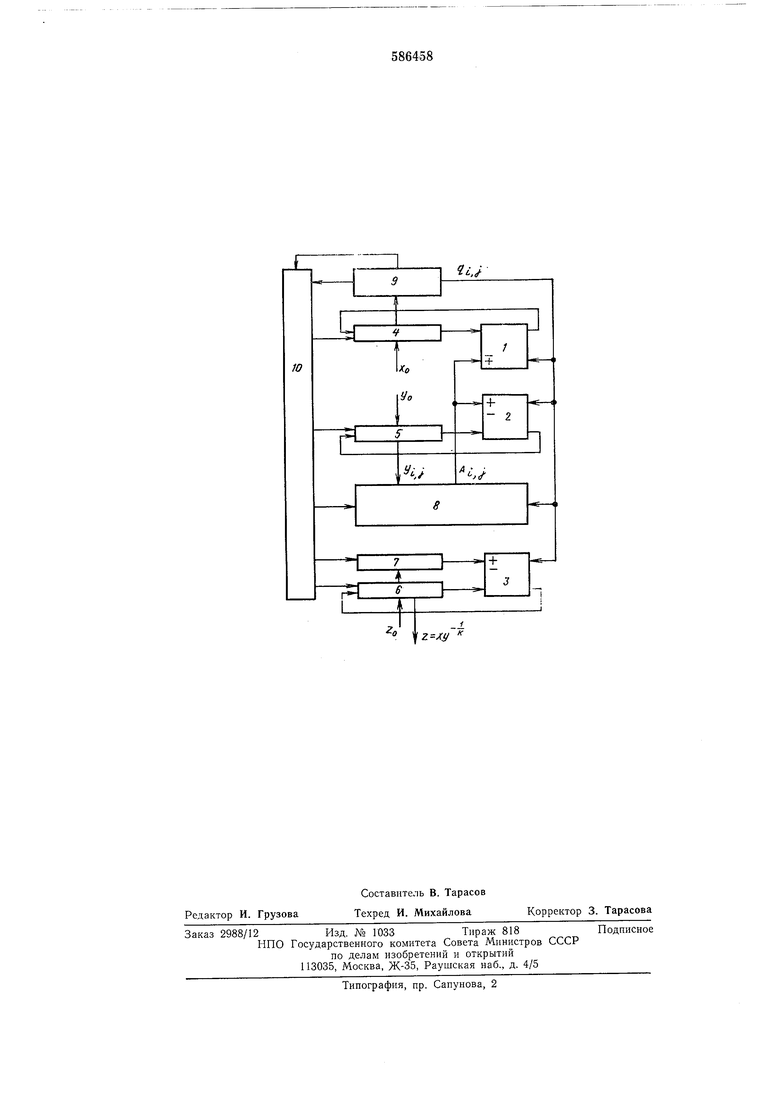

га, блок 8 задания показателя корня, блок 9 анализа сходимости и блок 10 управления.

Работает преобразователь следующим образом.

Первоначально в первый регистр 4 сдвига заносится дополнительный код аргумента у, в третий регистр 6 сдвига - ирямой код аргумента X, а во второй регистр 5 сдвига - прямой код второго аргумента у. Включается генератор импульсов в блоке 10 управления, В любой i, /-Й итерации с выхода блока 10 выдается серия (последовательность) сдвигающих тактовых импульсов для сдвига содержания четвертого регистра 7 сдвига на / разрядов вправо и значений Xj.j в блоке 8, а также продвижения значений содержаний сдвигающих регистров 4-7 и значения Ai,j из блока 8 на входы сумматоров-вычитателей 1-3. Результаты каждой итерации записываются с выходов сумматоров-вычитателей 1-3 младщими разрядами вперед в освобождающиеся при сдвиге старщие разряды регистров 4-6 и продвигаются в сторону младщих разрядов этих регистров. В конце каждой итерации в блоке 9 определяется очередная цифра qi,j (по зиаку содержания регистра 4 сдвига), которая выдается с второго выхода блока 9 на управляющие входы сумматоров-вычитателей 1-3. При 9i,j + l сумматор-вычитатель 1 работает в режиме вычитания, сумматоры-вычитатели 3, 2 - в режиме сложения. При qi,j - 1 их режим работы заменяется на обратный. Блок 9 анализа сходимости определяет изменение знака цифры и при перемене знака подает со своего третьего выхода на второй вход блока 10 управления сигнал перехода к следующему значению i. Когда содержание первого регистра сдвига равно нулю, от блока 9 поступает на первый вход блока 10 сигнал останова. Блок 10 перестает выдавать тактовые импульсы, процесс вычисления закончен и в третьем регистре 6 находится значение искомой функции.

Максимальное время вычисления функции в тактах равно Т 1акс п(п-{-т). Однако благодаря асинхронному режиму работы для больщинства значений аргумента у время вычисления Г.Тмакс, что значительно меньще времени вычисления известными способами при сравнимых затратах аппаратуры.

Предлагаемый цифровой функциональный преобразователь с унифицированной параллельно-последовательной структурой обладает простотой схемных решений из стандартных цифровых элементов и относительно высокой однородностью и регулярностью, что позволяет

полностью использовать возможности современной интегральной технологии для реализации в виде одной больщой интегральной схемы. Предлагаемый цифровой функциональный преобразователь совмещает противоречивые требования повыщения надежности, быстродействия, унификации и технологичности структуры, снижения аппаратурных затрат и обеспечивает оптимальное использование аппаратуры.

Формула изобретения

Цифровой функциональный преобразователь, содержащий четыре регистра сдвига, три сумматора-вычитателя, блок анализа сходимости и блок управления, причем первые выходы первого, второго и третьего регистров сдвига соответственно соединены с первыми входами первого, второго и третьего сумматоров-вычитателей, выходы которых подключены к входам соответствующих регистров сдвига, второй выход первого регистра сдвига соединен с входом блока анализа сходимости, первый выход которого соединен с первым входом блока управления, второй выход блока анализа сходимости - с управляющими входами сумматоров-вычитателей, выход четвертого регистра сдвига соединен с вторым входом третьего сумматора-вычитателя, шравляющие входы всех регистров сдвига подключены соответственно к первому, второму, третьему и четвертому выходам блока управления, отличающийся тем, что, с целью расширения функциональных возможностей за счет вычисления частного от деления одного аргумента на корень /fe-й степени из другого аргумента, в него дополнительно введен блок задания показателя корня, причем первый вход блока задания показателя корня соединен с вторым выходом второго регистра сдвига, второй вход - с вторым выходом блока анализа сходимости, управляющий вход - с пятым выходом блока управления, выход блока задания показателя корня соединен с вторыми входами первого и второго сумматоров-вычитателей, второй выход третьего регистра сдвига соединен с входом четвертого регистра сдвига, а третий выход блока анализа сходимости соединен с вторым входом блока управления.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №517021, кл. G 06F 7/38, 1974.

2.Авторское свидетельство СССР №491129, кл.О 06F 15/32, 1971.

e

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Двоичное устройство деления | 1975 |

|

SU541171A2 |

| Устройство для вычисления функции вида ух | 1975 |

|

SU579612A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для возведения в степень | 1975 |

|

SU616628A1 |

| Двоичное устройство деления | 1974 |

|

SU497585A1 |

Авторы

Даты

1977-12-30—Публикация

1975-12-15—Подача