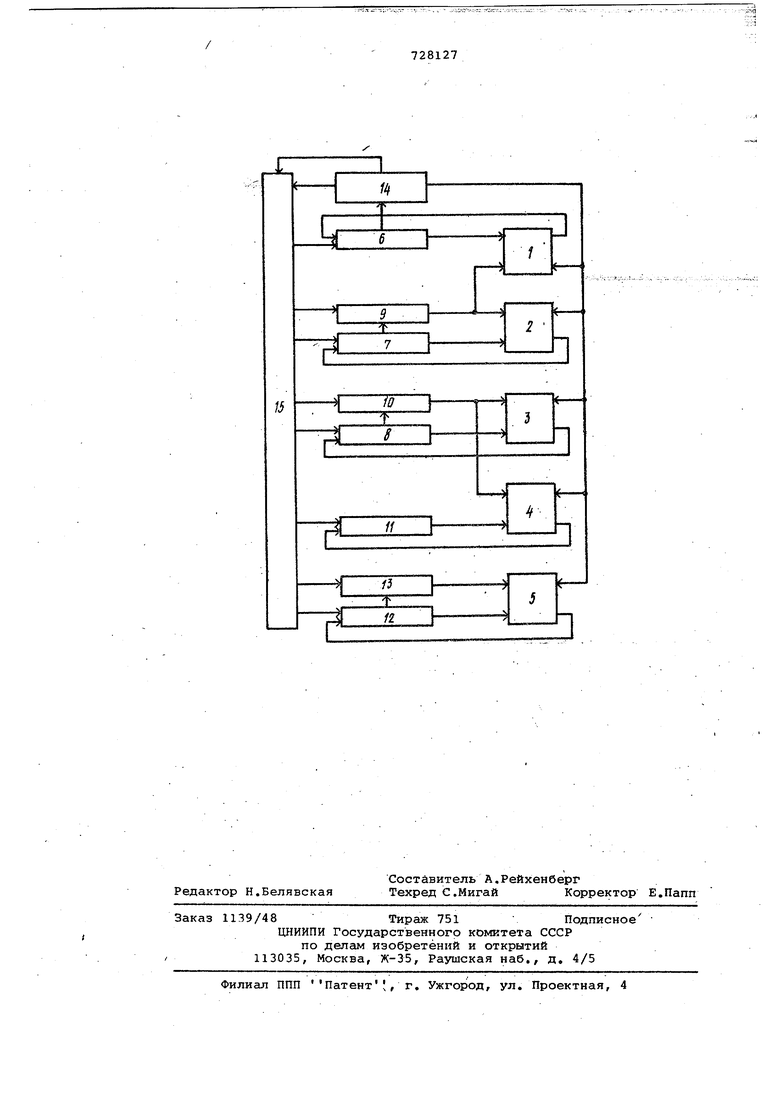

; 1 .-. Изобретение отн юится к области цифровой вычислительной техники, может быть использовано для Аппарат ной реализации вычисления функций, В основном изобретении (авт.ей . №633016) описано арифметическое уст ройство, содержащее три суммаТоравычитателя, пять регистров сдвига, блок Анализа сходимости вычисления и блок управления. Выходы блока управления соединены с управляющими входами регистров сдвига. Первые выходы первого, второго и третьего регистров сдвига соединены соответственно с первыми вхбдами. первого, второго и,третьего сумматоров-вычитателей, выходы которых соединены с первыми входами соответ ствующих регистров сдвига, вторые выходы второго и третьего регистров сдвига соединены соответственно с первыми входами четвертого и пятого регистров сдвига, выход четвер того регистра сдвига соединен с.вто рыми входами первого и второго сумм торов-вычитателей, выход пятого рег стра сдвига соединен с вторым входо третьего сумматора-вьпитателя. Вход блока анализа сходимости вычисления соединен с вторым выходом первого регистра сдвига, первый и второй выходы - С соответстйующими -входами блока управления, а третий выход с управляющими входами сумматороввычитателей 1. Блок анализа сходимости вычисления содержит две. цифровые схемы сравненияу выходы которых подключены соответственно к входам триггеров, вы-г ходы которых подключены соответственно к первым входам элементов И,втрры,е. входы которых подключены к такто-. вой шине, выходы элементов :и подключены соответственно к первому и второму выходам блока анализа сходимости вычисления. Входы схем сравнения и первый вход третьего элемента И . являются входами блока анализа сход 1имости вычисления, второй вход третьего элемента И подключенк тактовой шине,,выход третьего элемента И соединен через третий триггер к третьему выходу блока анализа сходимости вычисления. Недостатке этого устройства является его узкая специализация, так как оно предназначенотолько для вычисления частного от деления произведения двух аргументов на третий. Целью дополнительного изобретения является расширение функциональ ных возможностей путем вычисления одновременно с частным от деления произведения двух аргументов на третий, дополнительно частного от деления алгебраической суммы парных произведений из трех аргументов на третий и частного от деления квадра первого аргумента на третий. Поставленная цель достигается тем что в арифметическое устройство по авт.св, №633016 введены два сумматора-вычитателя и три регистра сдви га, управляющие входы которых соеди нены с соответствующими выходами бло ка управления, управляющие входы сумматоров-вЕлчитателей соединены с третьим выходом блока анализа сходи мости вычисления, выходы дополнительных шестого и седьмого регистров сдвига соединены соответственно с первыми входами четвертого и пятого сумматоров-вычитателей, выходы которых соединены со входами соответственно шестого и седьмого регистров сдвига, выход пятого регистра сдвига соединен со вторым входом четвертого сумматора-вычитателя, второй выход седьмого регистра сдвига соединен с входом восьмого регистра сдвига, выход которого соединен со вторым входом пятого сумматоравычитателя. Такое устройство за счет введения новых узлов и связей позволяет расши рить функциональные возможности. На чертеже представлена структур«ая схема арифметического устройстна. - - - . Арифметическое устройство содерЯЙ1Т одноразрядные сумматоры-вычитатели 1-5 комбинационного типа, регистры сдвига 6-13, блок 14 ангшйза сходимости вычисления и блок 15 упра ления. Первые выходы регистров сдвига 6-8 и 11-12 соединены с первыми входами соответственно сумматороввычйтателей 1-5, выходы которых ёрбтвётЬтвённо соединены с первыми входами регистров сдвига 6-8 и 11-12 Второй выход первого регистра сдвига 6 соединен с входом блока 14 ана- . лиза сходимости, первый и второй выходы которого соединены с входами блока 15 управления, а третий выход соединен с управляющими входами сумматоров-вычитателей 1-5, Вторые выходы второго и третьего регистров сдвига 7 и 8 соотйетственно соединены с первыми входами четвертого и пятого регистров сдвига 9 и 10. рехйстра сдвига 9 соединен с вто рыми входами сумматоров-вычитателей 1 и 2. Выход регистра сдвига 10 соединён с вторыми вкодами сумматороввычйтателей 3 и 4. Выходы блока 15 управления соответственно соединены с управляющими входами регистров сдвига-.6-10, шестого и седьмого регистров сдвига 11 и 12 и восьмого i регистра сдвига 13, Первый вход последнего соединен с вторым выходом регистра сдвига 12. Выход регистра сдвига 13 соединен с вторым входом сумматора-вычитателя 5. Входами устройства являются: входы регистра сдвига 6 для первого аргумента X, входы регистра сдвига 8 для второго аргумента У, входы регистра сдвига 7 для третьего аргумента Z. Входами ..устройства являются выходы: выходы регистра сдвига 8 - для функции ХУ/Z, выхбды регистра сдвига 11 - для функции (XZ + XY - YZ)/Z, ВЫХОДЫ регистра сдвига 12 - дляфункции X Vz. Первый выход регистров сдвига 6-13 является выходом от младшего разряда; второй выход - выхоДом от всех разрядов первый вход входом старшего разряда, управляющий вход входом сдвига. Второй вход сумматоров-вычитателей 1-5 является управляемым вхо- . дом, по которому может выполняться сложение или вычитание, в завйси- . мости от сигнала, .подаваемого на управляющий вход. . Блок .14 анализа сходимости вычисления предназначен для определения очередной цифры оператора ;, и ее изменения, а также определения момента равенства, нули содержания в регистре -сдвига 6. Блок 14 состоит, например, из схем сравнения кодов, триггеров и логических элементов. . Блок 15 управления содержит, например, генератор тактовых импульсов, распределитель, счетчик и логические элементы. Блок 14 предназначен для синхронизации работы устройства и вырабатывает серии тактовых импульdoB для сдвига и продвижения содержаний регистров сдвига 6-13 на соответствующие входы сумматоров-вычитателей 1-5. В устройстве реализован итерационный процесс вычисления, основанный на одновременном ретиении систеьи разностных рекуррентных соотношений, например, для двоичной системы счисления с фиксированной запятой; XO-K-Z. x,,x - Vi i2-:. cVr-sig- Hftjbu х.о. . iM-i.J.ii. V 7.V V. -V. 4а.у 9 п- X о nt-t-i V-.o,,,-u,.v,.,.,-.-M. i. ,

где i- показатель порядкового

номера итерации, J- показатель веса итерации п- число разрядов аргумента.

Все рекуррентные соотношения вычисляются одновременно за n+m так7 тов, где m - число дополнительных защитных разрядов для компенсации сечения чисел при сдвиге.

Вычисления указанных функций в арифметическом устройстве осуществляется следующим образом.

Первоначально в регистр сдвига и 11-12 заносится значение аргуента Х,в регистр сдвига 7 - значение ргумента Z, в регистр сдвига 8,начение аргумента У.Регистры сдвиге; -10 и 13 устанавливаются в нулевые состояния.

Регистры сдвига 9-10 и 13 уста- / навливаютсяв нулевые состояния.

В начальной (нулевой) итерации тактовые импульсы с выхода блока 15 управления поступают только в регистры сдвига 6 и 9, содержания которых, равные X и Z соответственно, вычитаются в сумматоре-вычитателе I езультат начальной итерации записывается с выхода сумматора-вычитатея 1 в освобождающиеся при сдвиге старшие разряды регистра сдвига 6 и продвиггиотся к его началу. В кон- це начальной итерации в регистре сдвига 6 находится значение X-Z.

В любой i-й итерации со- всех выходов блока 15 управления выдаются последовательности (серии) тактоых импульсов для сдвига на -разядов вправо от запятой содержаний егистров сдвига 9. 10 и 13 и продвижения содержаний регистров сдвига 6-13 на соответствующие входы сумматоров-вычитателей 1-5.

На первый выход сумматора-вычитателя I подается значение Х , на вторые входы сумматоров-вычитателей 1 и 2 подается значение на первый вход сумматоравычитателя 2 подается значение Z, На первый.вход сумматора-ййчитателя 3 подается значение Y , на вторые входы сумматоров-вычитателей 3 и 4 подается значение Y- 2 , на первый вход сумматора--вычи.тателя 4 подается значение Uf, На первый вход сумматора-вычитателя 5 подается значение V , на второй вход - значение 21. На управляющие входы сумматороввычитателей 1-5 подается оператор q-. На вход блока 14 подается значение . На первый вход регистра сдвига 9 подается значение 2.- . На первый вход регистра сдвига 1о подается значение . На управляющие входы регистров сдвига 6-13 подаются тактовые импульсы. ПереJ дача значений в регистры сдвига 9-10 производится только в конце каждой итерации. Результаты алгебраического суммирования в каждой итерации с выходов сумматоров-выQ читателей 1-5 записываются младшими разрядами вперед в освбождаюгциеся при сдбиге,Старшие разряды регистров сдвига;6-8, 11-12 соответственно и продвигаются к началу этих регистров сдвига. В конце

каждой итерации ( начальной) в блоке 14 анализа сходимости формируется очередная (для следующей итерации) цифра оператора по знаку содержания регистра сдвига 6

0 путем установки триггера в блоке 14 в соответствующее состояние.При значении q. +1 в сумматоре-вычитателе 1 выполняется вычитание,в сумма орах-вычитателях 2-5 выполняется

5 сложе(1}иё7

При значении q,- -1 режим работы сумматоров-вычитателей заменяется на обратный, В блоке 14 определяется момент изменения знака срдерQ жания регистра сдвига 6 (т.е. изменение значения оператора ) , и при его изменении на блок 15 управления выдается сигнал перехода к следующему весу итерации j, увеличенному

г.на единицу (т.е. к величине сдвига значений в регистрах сдвига 9, 10 и 13). Определение изменения знака производится путемсравнения значений q и .(. При неизменном , знаке сдвиг в; регистрах сдвига 9,

0 10 и 13 осуществляется на прежнее число разрядов. В блоке 14 анализа сходимости проверяется также усло о, и при его выполнении

вие X

1-И

в блок 15 управления выдается сиг5 :кал останова, так как процесс вычис|.ления закончен, и тактовые импульсы . на следуюцей итерации не выдаются. При этом в регистре сдвига 7 содержится значение первого аргумента X, . Q в регистре сдвига 8 содержится значёние функции XY/Z.,B регистре сдвига 11 содержится значение функций TXY + + XZ.- YZ)/Z, в регистре сдвига 12 содержится значение функции X /Z.

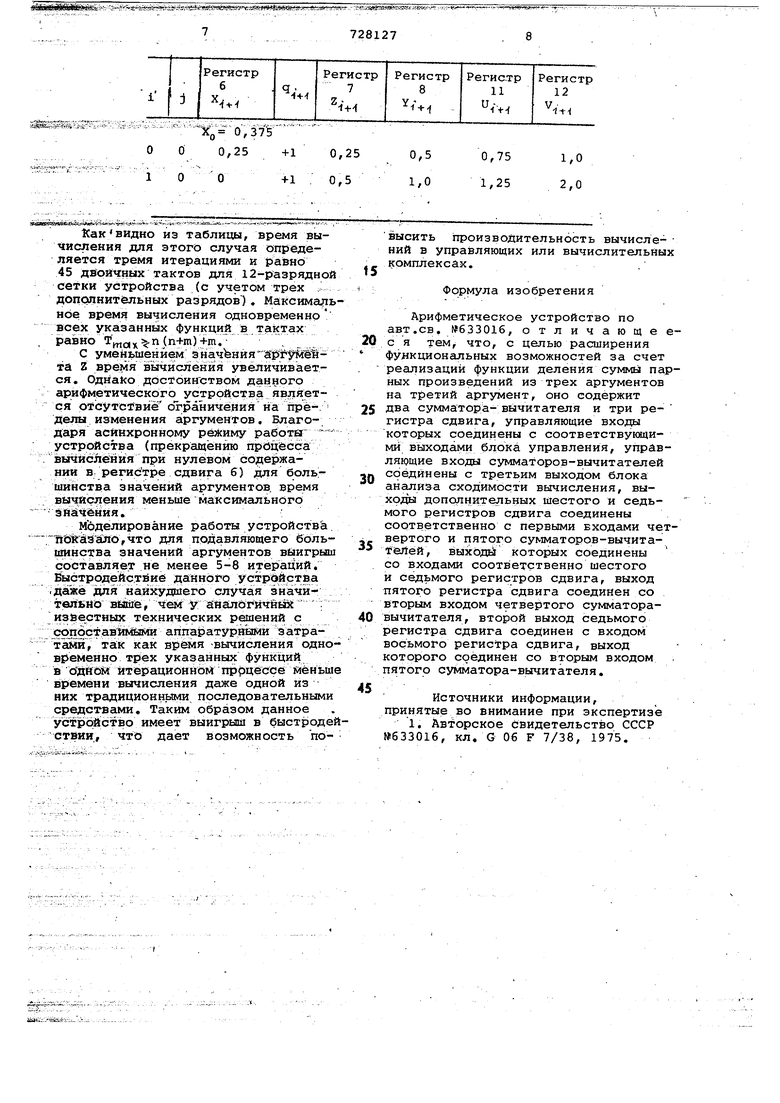

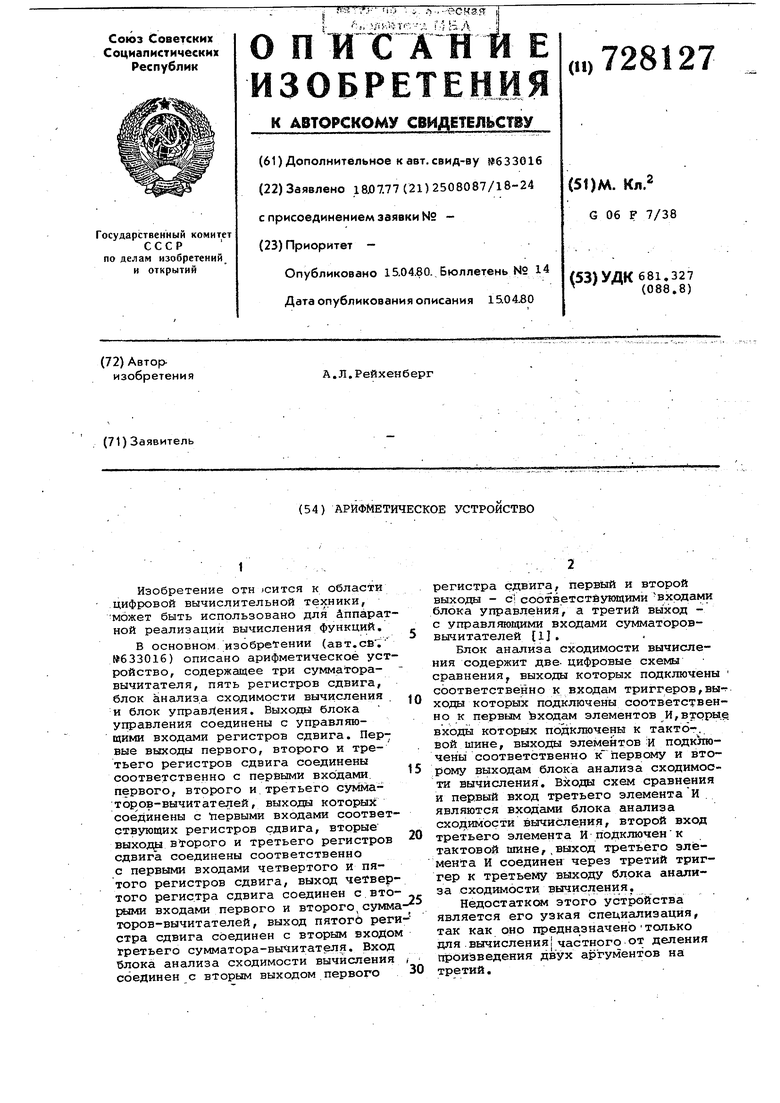

В таблице приведен пример вычисления указанныхфункций в даннсэм арифметическом устройстве для значений аргументов; X 0,5, Y 0,25, Z 0,125.

.1.:а;..йДЦа;,а|у-,У|-р--- -- - - ----- -- .---:----:- :-.-....ap Sg lfegi

gaupM-BSftji ь ц ц.j I - - -- --,.-.,..- . -- ..... ,.,.-,...,. . -. - 7728127

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Устройство для вычисления корня пятой степени | 1976 |

|

SU691848A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

-o;3YS

0,25

0 0

0,25

+1 0,5 0 +1

Каквидно из таблицы, время вычисления для этого случая определяется тремя итерациями и равно 45 ДВОИЧНЫХ тактов для 12-разрядной сетки устройства (с учетом трех дополнительных разрядов), Максимальное время вычисления одновременно всех у;казанных функций в .тактах paisHO T a n{n+m)+m.- - уменьшением значЪнйя а рг У:йёйта Z время iBH4ricJieHHя увеличивается. Однако достоинством дан.ного арифметического устройства язвляется отсутствие отграничения на пределы изменения аргументов. Благодаря асинхронному режиму работы устройства (прекращению процесса вычисления при нулевом содержании в регистре сдвига б) для большинства значений аргументов, время вычисления меньше максимального значения.

Моделирование работы устройства.

йб«йЭаЛо,что для подавляющего большинства значений аргументов выигрыш составляет не менее 5-8 итераций. Быстродействие данного устройства

;дажё для наихудшего случая значительно вШЮ, чем у айалбгйчнШ ; из |ертных технических реиений с сспбстав о ™ аппаратурннми эатра- .

тами, так как время -вычисления одновременно трех указанных функций в йдйсял итерационном пррцёссе меньше времени вычисления даже одной из них традиционньпли последовательными средствами. Таким образом данное устр(эйство имеет выигрыш в быст эрдействии, что дает возможность по0,75

1,0 1,25 2,0

высить производительность вычислеНИИ в управляющих или вычислительны комплексах.

Формула изобретения

Арифметическое устройство по авт.св. №633016, отличающеся тем что, с целью расширения функциональных возможностей за счет реализаций функции деления суммы паных произведений из трех аргументов на третий аргумент, оно содержит два сумматора- вычитателя и три регистра сдвига, управляющие входы которых соединены с соответствукидими выходами блока управления, управляющие входы сумматоров-вычитателей соединены с третьим выходом блока анализа сходимости вычисления, выхода дополнительных шестого и седьмого регистров сдвига соединены соответственно с первыми входами чевертого и пятого сумматоров-вычита ёЛей, йыходй которых соединены со входами соответственно шестого и седьмого регистров сдвига, выход пятого регистра сдвига соединен со вторым входом четвертого сумматоравычитателя, второй выход седьмого регистра сдвига соединен с входом восьмого регистра сдвига, выход которого соединен со вторым входом пятого сумматора-вычитателя.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1980-04-15—Публикация

1977-07-18—Подача