I

Изобретение относится к области запоминающих устройств (ЗУ).

Известно ЗУ с самоконтролем содержащее накопитель с контрольными разрядами, блок обнаружения неисправностей, элементы И и ИЛИ. Недостатком данного устройства является невысокая Нсщежность.

Наиболее близким техническим |решением к изобретению является ЗУ с само:контролем, содержащее накопитель, подключенный к блокам приема и вьщачи чйсел, датчику кода адреса и блоку кон -роля, элементы задержки, элементы И и ИЛИ и блок переключения . Однако в этом устройстве отсутствует адаптация к характеру отказа. Это снижаер эффективную емкость устройства, а та|сже вызывает отказы всего устройства при,групповых отказах элементов дамяти в числовых ячейках накопителя,что снижает надежность устройства.

Целью изобретения является повышение надежности и эффективной емкости устройства.

Поставленная цель достигается тем, что в предложенном устройстве первый контрольный выход накопителя подключен через первый элемент задержки ко входу блока выдачи чисел и непосредственно к управляющему входу блока) переключения, установочный вход которого соединен со входом датчика ко« да адреса. Выходы блока переключения соединены с одними входами элементов И, другие входы которых подключены к выходу блока контроля. Выход рдного из элементов И подключен через первьй элемент ИЛИ к инверсному входу блока; приема чисел и к первому контрольнок у входу накопителя. Выход другого эле-v мента И соединен через второй элемент задержки и второй элемент ИЛИ со входом кода адреса и непосредственно со ВТОР1Л4 контрольным входом накопителя, второй контрольный выход которого через третий элемент вадержки подключен к одному из входов второго элемента ИЛИ.

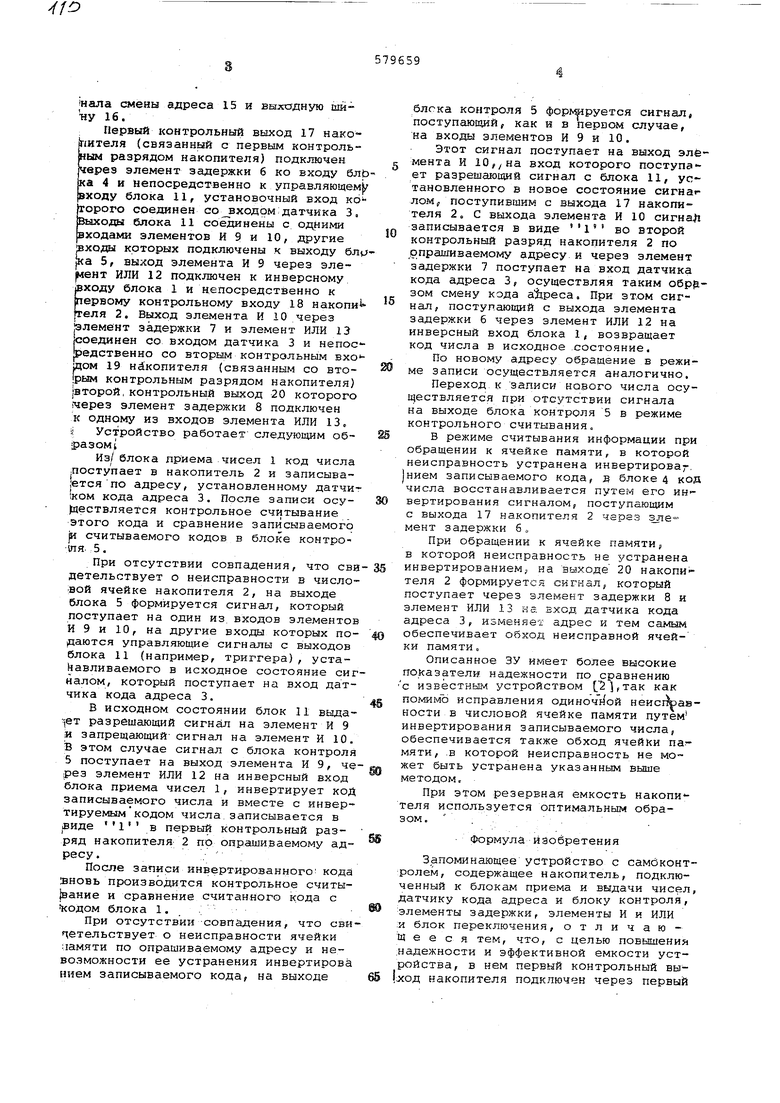

На чертеже изображена структурнач схема предложенного ЗУ.

Устройство содержит блок приема чисел 1, накопитель 2, в в-остав которого входят два рсонтрольных разряда, датчик кода адреса 3, блок выдачи чисел 4, блок контроля 5, первый 6, второй 7 и третий 8 элементы задержки, элементы И 9 и 10, блок переключения 11, первый 12 и второй 13 элементы ИЛИ, входную вшну 14, шину смены адреса 15 и внходную шину 16.

Первый контрольный выход 17 накопителя (связанный с первым контрольным разрядом накопителя) подключен через элемент задержки б ко входу блька 4 и непосредственно к управляющем входу блока 11, установочный вход к6 горого соединен со входом:датчика 3. Выходы блока 11 соединены с одними входами элементов И 9 и 10, другие входы которых подключены к выходу бл0|ка 5, выход элемента И 9 через ИЛИ 12 подключен к инверсному .входу блока 1 и непосредственно к первому контрюльному входу 18 накопи реля 2, Выход элемента И 10 через элемент задержки 7 и элемент ИЛИ 13 соединен со, входом датчика 3 и непосредственно со вторым контрольным 19 накопителя (связанным со вторым контрольным разрядом накопителя) |второй,контрольный выход 20 которого через элемент задержки 8 подключен к одному из входов элемента ИЛИ 13. i Устройство работает следующим образом/

Из/блока приема чисел 1 код числа поступает в накопитель 2 и записывается по адресу, установленному датчи ком кода адреса 3. После записи осу дествляеТся контрольное считывание этого кода и сравнение записываемого |И считываемого кодов в блоке контроотя. 5.

При отсутствии совпадения, что свидетельствует о неисправности в числовой ячейке накопителя 2, на выходе блока 5 формируется сигнал, который поступает на один из. входов элементов И 9 и 10, на другие входы которых подаются управляюцще сигналы с выходов блока 11 (например, триггера), устайавливаемого в исходное состояние сигналом, который поступает на вход датчика кода адреса 3.

В исходном состоянии блок II выда ieT разрешающий сигнал на элемент И 9 и запрещающий- сигнал на элемент И 10. В этом случае сигнал с блока контроля 5 поступает на выход элемента И 9, через элемент ИЛИ 12 на инверсный вход блока приема чисел 1, инвертирует коД записываемого числа и вместе с инвертируемым кодом числа.записывается в

в первый контрольный развиде

ряд накопителя- 2 по опраши.ваемому адресу.

После записи инвертированного: кода вновь производится контрольное считы|вание и сравнение считанного кода с кодом блока 1. ;

При отсутствии -совпадения, что сви етельствует о неисправности ячейки памяти по опрашиваемому адресу и невозможности ее устранения инвертирова нием записываемого кода, на выходе

блока контроля 5 форьетруется сигнал, поступающий, как и в первом случае, на входы элементов И 9 и 10.

Этот сигнал поступает на выход элемента И 10,/на вход которого поступает разрешающий сигнал с блока 11, установленного в новое состояние сигнаглом, поступившим с выхода 17 накопителя 2, С выхода элемента И 10 сигна г записывается в виде во второй контрольный разряд накопителя 2 по упрашиваемому адресу и через элемент задержки 7 поступает на вход датчика кода адреса 3, осуществляя таким смену кода адреса. При этом сигнал, поступающий с выхода элемента задержки 6 через элемент ИЛИ 12 на инверсный вход блока 1, возвращает код числа в исходное .состояние.

По новому адресу обращение в режиме записи осуществляется аналогично.

Переход, к записи нового числа осуществляется при отсутствии сигнала на выходе блока контроля 5 в режиме контрольного считывания.

В режиме считывания информации при обращении к ячейке памяти, в которой неисправность устранена инвертироваг. |нием записываемого кода, s блоке 4 код числа восстанавливается путем его ИНвертирования сигналом, поступающим с выхода 17 накопителя 2 через зле™ мент задержки 6

При обращении к ячейке памяти, в которой неисправность не устранена инвертированием, на выходе 20 накопителя 2 формируется сигнал, который поступает через элемент задержки 8 и элемент ИЛИ 13 на вход датчика кода адреса 3, изменяет адрес и тем самым обеспечивает обход неисправной ячейки памяти с

Описанное ЗУ имеет более высокие показатели надежности по сравнению с известным устройством (,так как помимо исправления одиноч1 ой неисг авности в числовой ячейке памяти путем инвертирования записываемого числа, обеспечивается также обход ячейки па мяти, ,в которой неисправность не мо жет быть устранена указанным выше методом.

При этом резервная емкость накопителя используется оптимальным образом. . .

S - Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к блокам приема и выдачи чисел, датчику кода адреса и блоку контроля,

-элементы задержки, элементы И и ИЛИ :и блок переключения, отличающееся тем, что, с целью повышения .надежности и эффективной емкости устройства, в нем первый контрольный выS х:од накопителя подключен через первый

влемент задержки ко входу блока вьада |ЧИ чисел и непосредственно к управля зощему входу блокапереключения, установочный вход которого соединен со входом датчика кода адреса; выходы яблокапереключения соединены с одни1ми входами элементов И, другие входы которых подключены к выходу блока контроля, выход одного из элементов И подключен через первый элемент ИЛИ ,к инверсному входу блока приема чисе |и непосредственно к первому контроль«ому входу накопителя; выход другого элемента И соединен через второй элемент задержки и второй элемент ИЛИ входом датчика кода адреса и непосред( ствеыно со вторым контрольным входом накопителя, второй контрольный выход которого через третий элемент задерж ки подключен ко одному из входов вто+роге элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР ) 367460, М.кл, 6 11 С 29/00,1971.

2.Авторское свидетельство СССР 497639, М. кл. G 11 С 29/00,1973

| название | год | авторы | номер документа |

|---|---|---|---|

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С БЛОКОМ КОНТРОЛЯ | 1966 |

|

SU189621A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU875471A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Устройство для автоматического контроля блоков памяти | 1976 |

|

SU610180A1 |

| Оперативное запоминающее устройство | 1987 |

|

SU1425782A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1363312A1 |

| Устройство для задержки цифровой информации | 1986 |

|

SU1383325A1 |

| Запоминающее устройство | 1978 |

|

SU743031A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1368923A1 |

Авторы

Даты

1977-11-05—Публикация

1976-07-19—Подача