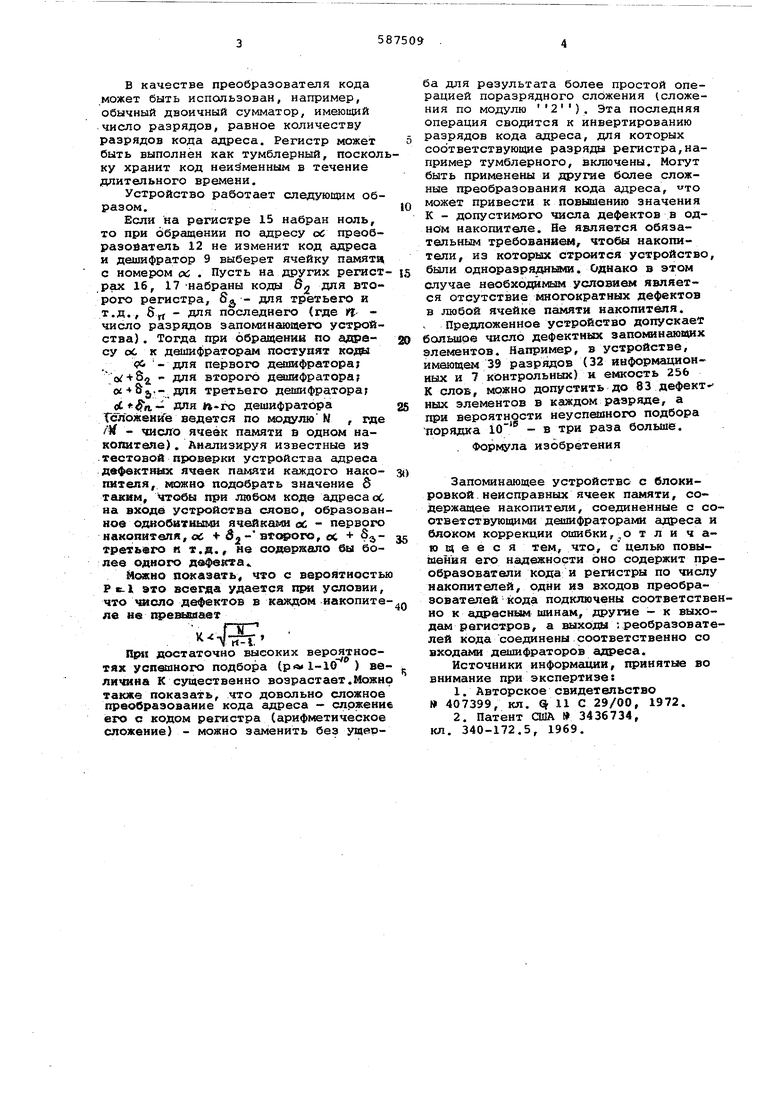

В качестве преобразователя кода может быть использован, например, обычный двоичный сумматор, имеюнсий число разрядов, равное количеству разрядов кода адреса. Регистр может быть выполнен как тумблерный, поскол ку хранит код неизменным в течение длительного времени. Устройство работает следующим образом. Если на регистре 15 набран ноль, то при обращении по адресу оС преобразователь 12 не изменит код адреса и дешифратор 9 выберет ячейку памяти с номером «; . Пусть на других регист pax 16, 17 -набраны коды ба для второго регистра, S - для третьего и т.д., Sft - для последнего (где П число разрядов запоминающего устройства) . Тогда при обращении по адресу ос к дешифраторам поступят коды б -для первого дешифратора; oif-tS для второго двнифратора; (x-vSj,.- для третьего дешифратора для «го дешифратора Тсложение ведется по модулю Ы , где /}( - число ячеек памяти в одном накопителе). Анализируя известные иэ .тестовой ироверки устройства адреса дефвкт1нлх ячеек памяти каждого накопителя, июжно подобрать значение S таким, чтобы при любом коде адресаоС на входе устройства слово, образован ное однобитными ячейками ос - первого накопителя, се t , ос S третьего и т.д., не содер}всало бы более одного дофекта.. Можно показать, что с вероятность Р с. I это всегда удается при условии, что толо дефектов в каждом накопите ле не прешляает При достаточно ылсоких вероятностях успешного подбора (рл«1-10 ) ве личина К существенно возрастает.Можн также показать, что довольно сложное преобразование кода адреса - сложени его с кодом регистра (арифметическое сложение) - можно заменить без ущерба для результата более простой операцией поразрядного сложения (сложения по модулю 2 ) . Эта последняя операция сводится к инвертированию разрядов кода адреса, для которых соответствующие разряды регистра,например тумблерного, включены. Могут быть применеша и другие более сложные преобразования кода адреса, то может привести к повышению значения К - допустимого числа дефектов в одном накопителе. Не является обязательным требованием, чтобы накопители , из которых строится устройство, были одноразряидаьали. Однако в этом случае необходимым условием является отсутствие многократных дефектов в любой ячейке памяти накопителя. Предложенное устройство допускает большое число дефектных запоьшнающих элементов. Например, в устройстве, имеющем 39 разрядов (32 информационных и 7 контрольных) и емкость 256 К слов, можно допустить до 83 дефектных элементов в каждом разряде, а при вероятности неуспешного подбора порядка 10 - в три раза болыле. . Фор11 ла изобретения Запоминающее устройстве с блокировкой неисправных ячеек памяти, содержащее накопители, соединенные с соответствующими да1Шфраторами адреса и блоком коррекции ошибки,,о т л и ч аю щ е е с я тем, что, с целью повышения его надежности оно содержит преобразователи кода и регистры по числу иакопителей, одни из входов преобразователей кода подключены соответственно к адресным шинам, другие - к выходам регистров, а выходы :реобразователей кода соединены соответственно со входами дешифраторов адреса. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство 407399, кл. О, 1 С 29/00, 1972. 2.Патент ОНА 3436734, кл. 340-172.5, 1969.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с обходом дефектных элементов памяти | 1986 |

|

SU1387046A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Логическое запоминающее устройство | 1981 |

|

SU972589A1 |

| Запоминающее устройство с обходом дефектных элементов памяти | 1986 |

|

SU1387047A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Полупроводниковое оперативное запоминающее устройство с коррекцией информации | 1990 |

|

SU1795520A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

Авторы

Даты

1978-01-05—Публикация

1976-06-21—Подача