1

Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализации операций вычисления корней N -и степени из частного и произвецения двух аргументов при работе в реальном масштабе времени или при большой частоте обращения к этим операциям.

Известно устройство для извлечения корнейМ-ой степени, содержащее датчик Холла, дроссели, усилитель, электронную лампу и резистор l .

Однако это устройство позволяет получить результат только в аналоговой форме (в вице напряжения или тока).

Наиболее близким к -предлагаемому по технической сущности и постигаемому результату является устройство для извлечения корня N -ой степени, содержащее блок управления, выходы которотю соединены со входами сдвига соответственно с первого по (М+1)-ый регистров, выходы первого по ( N -1)-ый регистров соединены соответственно с первыми вхопами с

первого по (N-1)-ый сумматоров-выЧ№тателей, выходы которых соединены, соот ветственно, со входами первого по (М-1)-ьгй регистров 121 .

К недостаткам этого устройства относится невозможность одновременно вычиолить корни N -и степени из частотного и произведения степеней двух аргументов.

Цель изобретения - рааиирение класса рещаемых задач за счет возможности из10влечения корня N -и степени одновременно из частного двух аргументов и проиэ ведения их степеней.

Поставленная цель достигается тем, что устройство содержит N-ый по ()-oй

15 сумматоры-вычитатели, N блоков сдви- га, блок фop fиpoвaния констант, блок анализа, первый выход которого соединен с управляющими входами со второго по (N + 2)-и сумматоров-вычитателей, второй

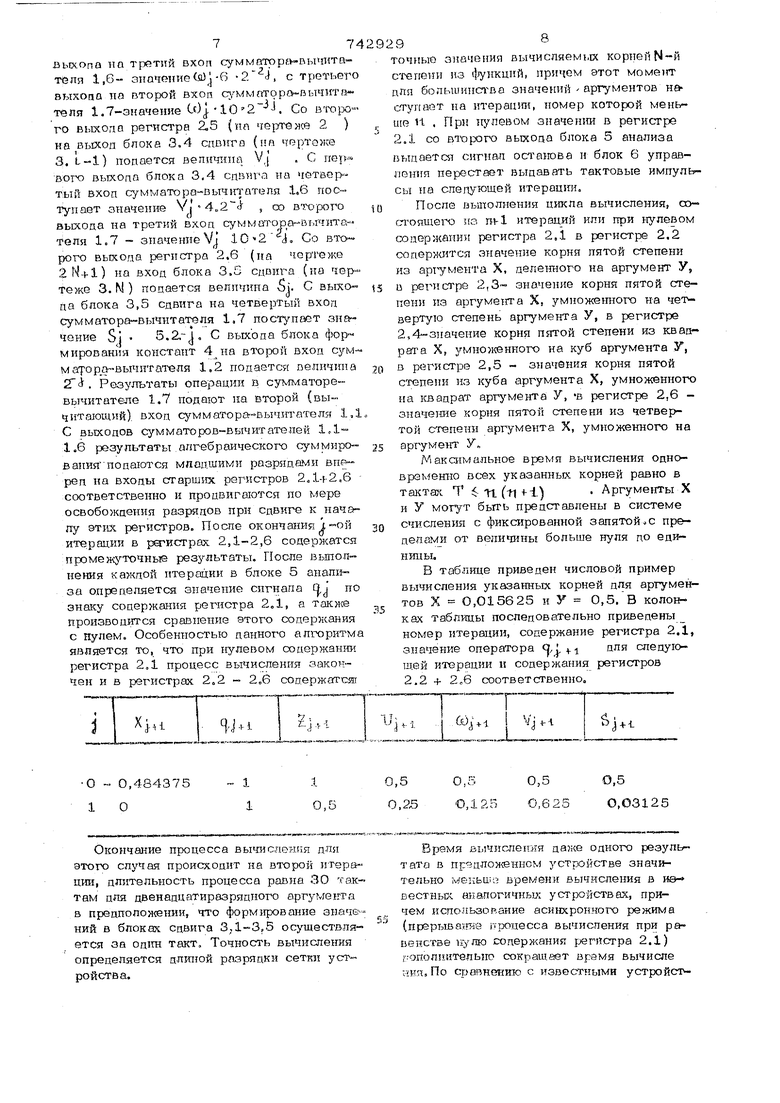

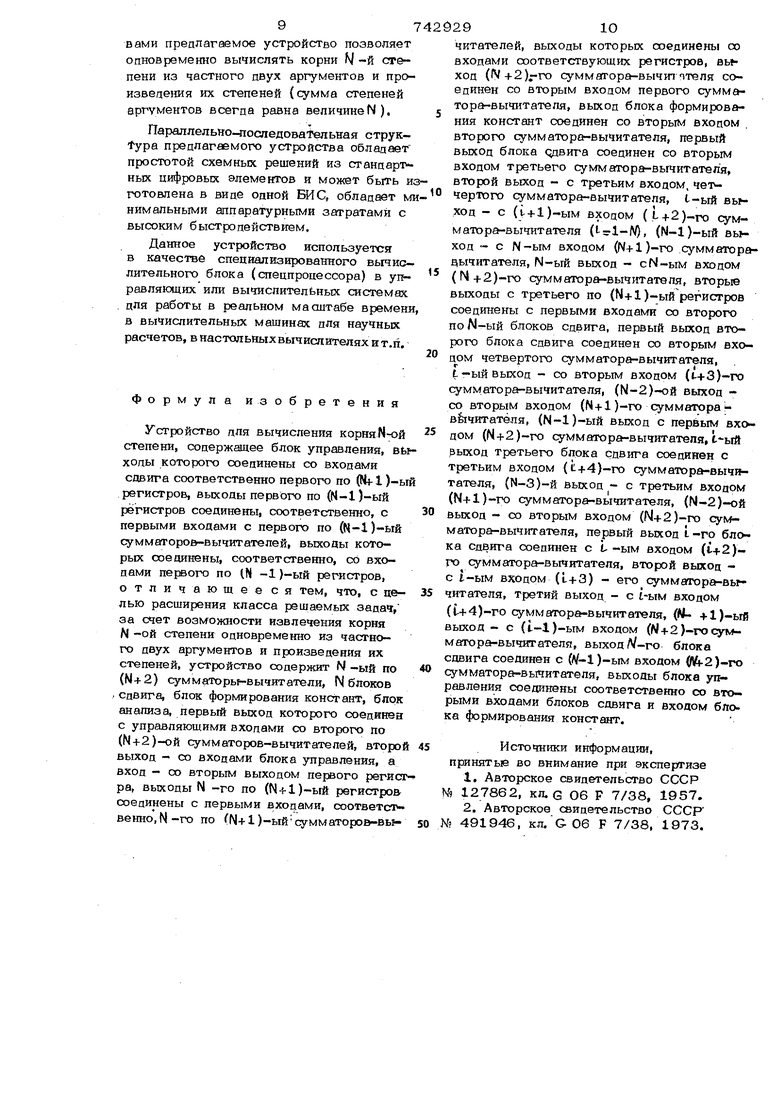

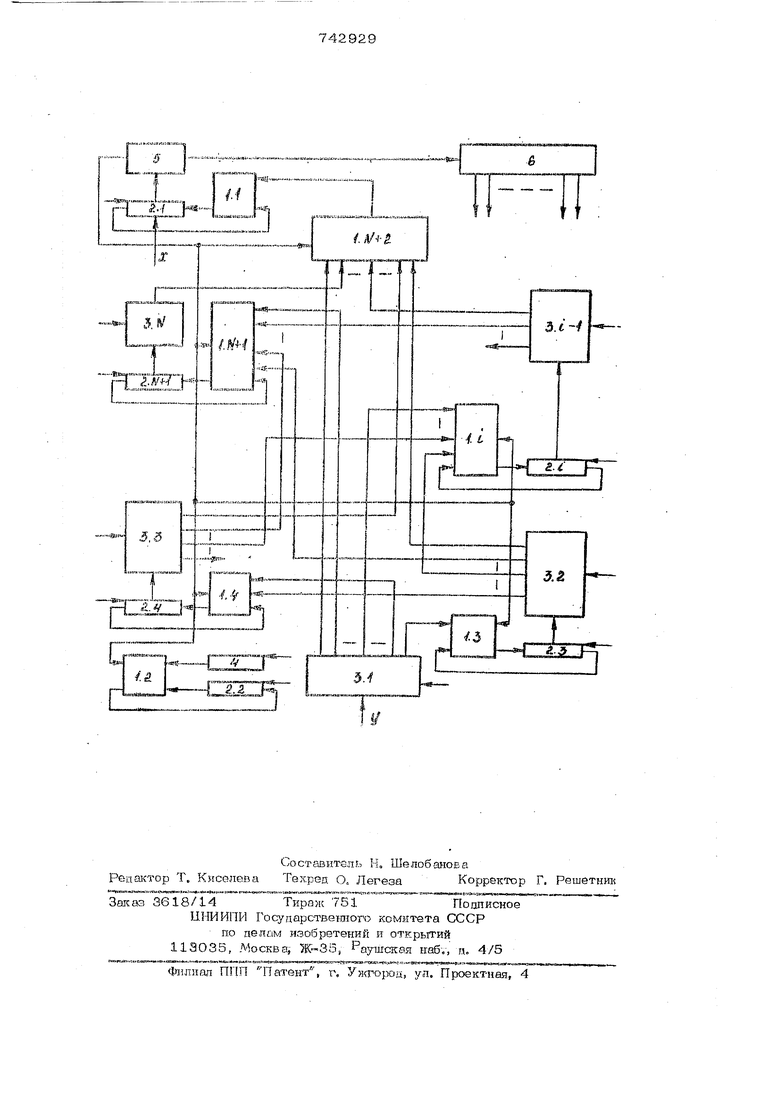

20 вькод - OD входом блока управления, а вход - со вторым выходом первого регистра, выходы N-го по (W + 1 )-й регистров соединены с первыми входами, соответсг37ЗецНО, N -TXD no ()Й CyNSVeaTOpOD-Bb -ЧИГЙгеПОЙр ВЫХОЦЬ ЕЮТОрЫХ COersRHSHbl C:N-. ответственно со входами ссол-а&тстэующих регистров, выхоп {М-г-2 j-ivi .:умматор -i; : .читателя соецинон со tvropb xt дхоло ; пд;:БОГО СуММаТОра- НЫЧИТЛТг 51, о1е;:О 1 бШ: :формирояапия копстаг Т ооег:(уП:ег| со jjiopiiM BJionoi, вгортго суылПТОр;;--&гччпт1:;Тепг;, первый выхоп первого блока савнг;. соепЬ ire ц сх) вторым ажздом третиотч: сумме-тори йычи атепя, второй выход с трет5-,,км вк.о:йом четертогю аторй--вьРн:15Т.атй.пп, ь-ЫЙ выход- с (14-1)ым axoaoKf, (i4-2) сумматор&-вычитатепя (l --1 N) (M-i-l)-bii выхоп cN ым вхоцом (N.fl)ro сумматора-вычктатопя, N -ый выхоц - с Н-ым входом (N-}-2)-ro сумматора-вычптстеля, вторые выходы с третьего по (Ki-fl)brli psrHCTpoB соединены с rfsprvbiMTi входами со BTO}xvro по N -и блоков cnBin a, первый выход гугортго блока савтц-а соэднне со BTopbirv входом четвертого сумматора-в .пя 1-ым выход со вторьгм Bxoaov; (t-{- З}- сумматоро-вычитатепя (/1-2)ой з код™ со вторым входом ()-го сумматор вь|читатеяя, (М--1)--ый выхоп - с первым в хо иoivf (Н - 2) -го сум М ато р а-вычзгт а:ге nsj, t ьв5: вькод третьего блока сдВ-ЧТа соепилен с третьим вхопом {i-f4)-«i43 сул-; атора-выздзтатеия (М-З)-ый вы-хоп - с третьим входом ()-ro сумматора-выч , (N-2)--6ft ЕБКОЦ .-. со вторым влопом (N.-|.2). (;: мма1Х р& ВыЧита1епя, первый выхоп блока соэпинегс ч с t входом (i-j-2)-ro о/-мматора ВЫд татоля, выхоа - с L -BSM вхопом (-.,;. 3) суммат зра-вычнтатепя, третий вьпюп с L -ым вхоцом (i--i-4)-ro суммато;ра Вычитателя, (М-1.-i-1 ).-.ый вьиод -- с (L.l)..biM ВХОДОМ (N-f2)--ro сумматора- вычитатепя, БььчодД|™гх) блока саанга соединен с ( )--ым вхоцом ОМ-г-2)-чо с,умматора-вы -1 ггатолд5 вьо;:окъ; б-Г п::а уп равления соолКчеиы ооответсгне-чо со ::т рьши входами 6jroKOB сдвига н з;:0аом формиравакпя констант, На черте 1се представлена бпок-сжма. чгстройства П:Пп вычиспенпя корня рЬ-г ст пени. Устройство оцноразр.циыа сумматоры-вь1чита:гепи lni- lN-7-2i регист ры 2,l-«,2,N.i-l, блоки 3,,Нс0,вига, блок 4 формировавши констант, блок 5 анапиэа и бпок 6 управления, Входом устройства для йргу;-лента X является вход рйгпстра 2,1., для аргуман та У вход блока 3,1 Сдвкра, Выхоламк 94 i -fpoffCVRs квляются выхопы регистров 2,.N-i-1, крнчек в регистре 2,2 со;;йрХ:ПГлч; : ivOp iib N сгепени из част lOro api7 -ie:iT3 X и У, а в регистрах ::,.N-fl держатся соответс1«зенно vrpoiioae/itiniH озелеией с первой по )--ю артументова сумма по у;)заг&пйй с--х-лбней двух аргументов paEi; ;л аел«чл ш N, Слмматоры-вьтчитатзп 1.1-1. N42 явшнс гсл одЕоразряднымп ком6инaimomiыми oxeNowj :, fjicno входов сумматоров-вычн- ..-™1.S равно двум. Число вхо™ дов сумм ато|юв вычпт ателей 1,4-1 iN+ 1 равно уМчЧньшепьому на единшгу их норядков ому номеру, Чиою входное сумматоровБЫПгтатепе-;; ;L,N-).2 равно вели«пше N, Сумматор-йы:читатель 1.1 работает но второму входу только в ртдшме вычитания. PesoJM работы по соответствующим входам сук коаторов--йычитателей 1.,N + 2 опре целяется сагиалом, подаваемым на их вход управления. Первый вьосод регистров 2.12.N-f-l выполнен от мпадшего разряда, вторые вхопы - от всех разрядов. Блоки . N являются устройствами ц ля сдвига к умно ьвния на пос.гоянные коэффициенты содер :сания соответствующих регистров Эти блоки могут быть выполнены яибо на регистрах сдвига и одноразря-дных сумматорах, либо на матричных схемах., формирования констант 4 вида может быть выполнен либо в виде одностороннего запоминающего устройства, либо в В7-:де редир гу,тяцнотго1Х1 регистра сдвига и тфп. Блок 5 анализа выполнен в виде цифровой схемы , сравнения и триггера с логическими элекгентами. Второй выход блока 5 является выходом схемы сравнения рег-истра 2,1 с логическим нулем, на первый вход которой подаются РЬЕОДЫ разрядов yj9r-CTpa 2 ,, KpGiv55 знакоЕстх)„ Последний Гм;: .:;тгя Ч-г;а;;; логнческие элементы на Trea isp, выход которото является первым вылоцО -; блокй Ь Блок. 6 управления содерЖ1П Напримерf гекератор TaKiOBbrx импупьактапь, счетчш:; логические .:м.лЛ1сл.атг1гя корня М-й степени nptiKuJTO Одновременно- нтерйцкоипом лроцессе систе;: рэкуррентиыл соотношений, jvarrpHMsp дЛй иЭоичной ап т-эмы счи спе ния: -,N-1.. .- ...N-2 л.х. д:. д .x,.,;.Kj( . -.MX;fc« а- , q yгJ-.№Lp:iI.г5J.н,...j) ,,C.tllb±U2-J4,,.(|.. --Г ---- M.,,. П± ПРИ Xj 0 (--Sl§nxj|, при 01,2,.. 2o O.Zj,, Hj Cjja-JZ -VF у-г )(ij . Uj,,-yEj, Wo 0. Wj u3j4.,ji7j .г ( Vo 0. УZ|,j .3- -Mj;-3-Z , ,. (j.y.p-JJ,,. 5o-o. ,, Sj(jУHj гм-г)-.г y2pi i HIiin.,..(NH;(N-)(N..y,,rM.l.i ..). Sa-- /r. в устройстве- эти рекуррентнье COOP ношения вычисляются параппепьно. Макс мальное число итераций равноti+l, где TL- число разрядов аргумента. Первоначально все регистры 2,i-2M+ устанавливаются в нулевое состояние. В регистр 2,1 заносится код аргумента X в блок спвига ЗД код аргумента Y, Вычисления, удобно пояснить, приняв значение показателя корня конкретной в личине, например N-5, В этом случае np веденная на чертеже блок-схема полно стью соответствует необходимой структу ре, причем. 5, в алгоритм вьмиспения описывается следующей системой рекур рентных сооттюшений: . ( + /j-IO-a V (y4-i. XTf Г-и при х; о ,fitgnXj (,l...tt. EO O, 2,-,, Zj-(j-r-. in }fjUo-0. l 4i-y2j i-Uj+« jyE- . u)o--o. 03j,, .a)j fjU-j-a-a- y-z 4 : V,- jWj-3-a Uj 3-l- j .Vj,, y,i: . .y. Первое рекуррентное соотношение реализуется в сумматорах-вычитателях 1.1 и 1.7 (на чертеже 1,N +2). Второе логическое управление - в блоке 5 анализа. Третье рекуррентное соотношение реа лизуется в сумматоре-вычитателе 1,2. Четвертое рекуррентное соотношение - в сумматоре-вычитателе 1.3. Пятое рекур296рентное соотношение реализуется в сумматоре-в ычитателе 1.4, Шестое рекуррент ное соотношение реализуется в сумматоревычитателе 1.5 (на чертеде 1. 1). Седьмое рекуррентное соотношение осуществляется в сумматоре-вычитателе 1.6 (на 1.Мч-1). На первой -итерации j 0 с первого вьнхода блока 5 анализа выдается сигнал |. ( так как содержание регистра 2.1 или значение аргумента X всегда положительное), который определяет ние по вторым входам в мматорах-вычитателях 1.2-1.7 по четвертым входам в сумматорах-вычитателях l,5fl.7 и по пятому входу сумматора-вычитателя 1,7. На спе,аую1цих итерациях значение сигнала о аависит от знака содержания регистра 2,1, при (.1 -1 по указанным входам сумматоров-вычитатепей 1.2- 1.7 выполняется вычитание. В любой J- ой итерации с выходов блока 6 управления выдается серия (последовательноегь) тактовых импульсов, которая сдвигает соответствующие значения в блохах савигаЗ.1-3.5 (на чертеже 3.1-3, N), процвигает содержания регистров 2,1-2,6 (на чертексе 2,1 -2.М+1) на входы сумматоре в-вы читателе и 1.1-1.6 (на чертеже l,.N + 3). с первого выхода блока 3.1 Сдвига 3.4 на второй вход сумматора- вычитателя 1.3 поступает значение V2. со второго выхода на третий вход сумматора-вычитателя 1,4-значение У , с третьего входа на четвертый вход матора-вычитате пя 1.5 (на чертеже 1-t)- значение У 2. J с четвертого входа на пятый вход сумматора-вычитателя 1,6, (на чертеже 1.N + 1)- значение УZ J и с ПЯ7Ч5ГО выхода на пятьп вход сумматора-вычитателя, 1.7 (на чертеже 1.N-2)- величгша У Р «1. Со второго выхода регистра 2,3 на вход блока сдв1гга подается величина U/ , С первого выхода блока 3.2 сдвига на второй вход сум- матора-вычитателя 1.4 поступает значечение ХГ 2 2Г ,со второго выхода на второй вход сумматрра-вычитаггеля 1.5- значение lJj3., с третьего вы-. хода на второй .вход сумматора-вычитате- ли 1,6-значение iTj 4,2-j ., с четвертого выхода на первый выхоп сумматрр&-вычитателя 1.7- значение Uj 52 Со второго выхода регистра 2,4 на вход блока 3.3 сдвига подается величина (fi)j. С первого выхода блока сдвига на третий вход сумматора-вычитдтеля 1,5 поступает значение Cs)- 3-2 , со второго выхопа HQ третий вхоп сумматор -вычитатепп 1,6- 3Ha40nne(fl)j-6 , с третьего выхода па второй вхоп о.ммпторо-вычитг те пя 1.7-эн ачеиие Сс) . 10 2 -I. Со в то jooто выхопа регистра 2.5 (пп чертемсе 2 ) на выход блока 3.4 сппнга (не. чертеже 3. L-1) подается величина V,j . С пер вого выхопа блока 3,4 сдвига на четвер тый вхоп сумматора-вычетатепя 1.6 посlynaeT значение Vj4 2 S , со вгорого выхода на третий вхоа суыматор а-вычнтатепя 1.7 - значение VJ 10-2 i, Со второтх) выхода регистра 2,6 (на чертеже 2lN.fl) на вход блока 3.S сцвига (на чср теже 3. М ) подается величина Si. С выхо да блока 3,5 сдвига на четвертый вход сумматора-вычитателя 1.7 поступает значение Si 5.2.- о С выхода блока формирования констант 4jia второй вход сумма ор а-вычитателя 1.2 попаетси величина 2. Результаты операции в cy ш:aтope-вьгштателе 1.7 подают па второй (вычитшощий), вход сумматора-вычшателя 1,1 С выходов сумматоров-ВБ Читатхэлей 1,1- 1.6 результаты .алгебраического суммирования подшотся мпоцшими разрядами внереп. на входы старших регистров 2,l-f.2.6 соответственно и продвигаются по мере освобождения разрядов при сдвиге к началу этих регистров. После окончания i-ои ите.рации в ра истрах 2,1-2,6 содержатся промежуточные результаты. После выполнения каждой итерации в блоке 5 анализа определяется значение сигнала (.|, i по знаку содержания региогра 2Д, а также производится сравнение этого соцержания с Нулем. Особенностью данного алгхэритма является то, что при нулевом содержантте регистра 2,1 процесс вычисления закончен и в регистрах 2.2 2,6 соцержатсяг точные эиаченип вычисляемых корней степени из ()ункций, причем этот момент для бопьшинсл ва значений - аргументов наступает на итерашш, номер которой меньше н , При нулевом значении в регистре 2Д со второго выхода блока 5 анализа выдается сигнал остагова н блок 6 управления перестает выдавать тактовые импульсы на слепующей итерации. После вьшолнения цикла вычисления, остоящегх) ма итераций или при нулевом содержании регистра 2.1 в регистре 2.2 содер У1Тся значение корня пятой степени из артумента X, aeneimoro на аргумент У, в регистре 2,3 значение корня пятой степени из аргумента X, умножешюго на четвертую степень аргумента У, в регистре 2,4-значение корня пятой степени из квадрата X, умноженного на куб аргумента У, в регистре 2,5 - значения корня пятой степени из куба аргумента X, умноженного на квадрат арг -мента У, в регистре 2,6 значение корня пятой степени из четвертой степени аргумента X, умноженного на аргумент У„ Мака1мальное время вычисления одноврз1ч енно всех указанных корней равно в тактах Т $ TL (t| -l) Аргументы X и У могут быть представлены в системе счисления с фиксированной запятой с пределам и от величины больше нуля до единицы. В таблице приведен числовой пример вычисления указанных корней для аргументов X О,О15625 и У 0,5.В колонках таблицы последовательно приведены номер итерации, содержание регистра 2.1, значение оператора для следующей итерации и содержания регистров 2.2 + 2,6 соответственно.

О 0,484375 1 О

0,5

Окончание процесса вычисления для этого случая происходит на второй итерации, длительность процесса равна 30 тактам для двенадцатиразряднотнэ apryMGirra в прецполондании, что формирование аначе-ний в блоках Сдвига 3,1-3,5 осуществляется за Один такт. Точность вычисления определяется длиной разрядки сетки устройства.

0,5

0,5

0,5

0,625 ОД25 О,О3125

Время вычисления да7ке одного результата в предложенном устройстве значительно меньше; времени вычисления в известных шшлогичных устройствах, причем использование асинхронного режима (прерыва;ет8 процесса вычисления при равенстве нулю содержания {хггистра 2.1) гополнителыю сокращеет врамя вычисле ния. По сгравнению с известными устройствами преплагеемое устройство позволяет опновременнс вычислять корни N -и степени из частного двух аргументов и произвеае1шя их степеней {сумма степеней аргументов всегда равна BenH4HHeN).

Параллельно-лосяедоваТельная струкtypa преппагаемого устройства обпаааег

простотой схемных решений из стандарт ных цифровых элементов и может быть иготовлена в виде одной БИС, обладдат мнимальными аппаратурными затратами с высоким быстродействием.

Данное устройство используется в качестве специализированного вычислительного блока (спецпроцессора) в управляющих или вычислительных системах для работы в реальном маоцтабе времени в вычислительных машинах для научных

расчетов, в настольных вычислителях и т п

формула изобретения

Устройство для вычисления корняМ-ой степени, содержащее блок управления, Bt,fходы которого соединены со входами сдвига соответственно первого по №-1)-ый регистров, выходы первого по (М-1)-ый регистров соединены, соответственно, с первыми входами с первого по (М-1)-ый сумматоро&-вычитателей, выходы которых соединены, соответственно, сО входами первого по IN -1 )-ый регистров, отличающее ся тем, что, с целью расширения класса решаемых задач, за счет возможности извлечения корня N -ой степени одновременно из частного двух аргументов и произведения их степеней, устройство содержит N -ый по (N+2) сумматорьг-вычитатели, N блоков .сдвига, блок формирования констант, блок анализа, первый выход которого сое дине а с управляющими входами со второго по (N+2)-oй сумматоров-вычитателей, второй выход - со входами блока управления, а вход - со вторым выходом первого регисг ра, выходы N -го по (N-f-l)-ый регистров соединены с первыми входами, соответсурBeHHO,N-ro по (N+l)-ыйcyммaтopOiB вь читателей, выходы которых соединены со входами соответствующих регистров, (fV+2)rro сумматора-вычиптеля соединен со вторым входом первого суммен тора-вычитателя, выход блока формирования констант соединен со вторым входом . второго сумматора-вычитателя, первый выход блока ;двига соединен со вторым входом третьего сумматора-вычитателя, второй выход - с третьим входом, чет чертого сумматора-вычитателя, t-ый - с (1 + 1)-ым входом (1+2)-го сумматора-вычитателя (t-l-N), (М-1)-ый Bbtход - с N-ым входом (N+l)-ro сумматорадычитателя, N-ый выход - cN-ым входом (М+2)-го сумматора-вычитателя, вторые выходы с третьего по (Ы+1)-ый регистров соединены с первыми входами со второго по Д1-ЫЙ блоков сдвига, первый выход второго блока Сдвига соединен со вторым входом четвертого сумматора-вычитателя, L-ый выход - со вторым входом (ц-З)-го сум иатора-вычитателя, (М-2)-ой выход со вторым входом (N + 1)-го сумматорав§1читателя, (Ы-1)-ый выход с первым входом (N+2)-ro сумматора-вычитателя, рыход третьего блока сдвига соединен с третьим входом {t+4)-ro сумматора-вычитателя, (М-З)-й выход - с третьим входом (N+l)-ro сумматора-вычитателя, (Ы-2)-ой выход - со вторым входом (N+2)-ro сумматора-вычитателя, первый выход i -го блока Сдвига соединен с t -ым входом (t+2)Го сумматора-вычитателя, второй выход с t-ым входом (1+3) - его сумматора-вычитателя, третий выход - с t-ым входом (1-+4)-го сумматора-вычитателя, (М- +1)-ьг выход - с (t-l)-biM входом (N-f 2)-госум матора-вычитателя, выход /V-ro блока сдвига соединен с (-1)-ым входом (fft-2)-ro сумматора-вычитателя, выходы блока управления соединены соответственно со вторыми входами блоков сдвига и входом блока формирования констант.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР К9 127862, кл.с Об F 7/38, 1957.

2.Авторское свидетельство СССР № 491946, кл.С06 F 7/38, 1973.

В Тицапкя-- ; - - ,

..,„,.1..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для возведения в степень | 1975 |

|

SU616628A1 |

| Устройство для вычисления корня к-ой степени | 1976 |

|

SU736096A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Цифровой функциональный преобразователь | 1975 |

|

SU586458A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления функции вида ух | 1975 |

|

SU579612A1 |

| Устройство для вычисления корня пятой степени | 1976 |

|

SU691848A1 |

| Устройство для извлечения квадратного корня и его обратной величины | 1988 |

|

SU1545218A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

Авторы

Даты

1980-06-25—Публикация

1977-04-19—Подача