Изобретение относится к области запоминающих устройств.

Известно устройство для контроля полупроводниковых оперативных накопителей, содержащее выходной регистр, преобразователь кода и блок сравнения 1. Однако это устройство не позволяет проводить контроль накопителей |ПО сложным квадратичным тестам.

Наи-более близким техничеоки1м решением к изобретению является устройство для контроля лолупроводниковых оперативных накопителей, содержащее адресный блок и блок формирования данных, подключенные к блоку управления 2.

Недостатком этого успройсгва является то, что на проверку при его .помощи схемы выборки кристалла 1полу1проводни1ковых оперативных накопителей требуется значительное число тестов, так как код выборки кристалла является приращением кода адреса по старшим разрядам.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что предложенное устройст1во содержит счетчик, регистры и блок сравнения, входы которого подключены соответственно к выходам счетчика и первого регистра и ко входам второго регистра, выход которого соединен с выходом устройства. Входы счетчика и первого регистра подключены к выходам блока управления, вход которого соединен с вы.ходом блока сравнения.

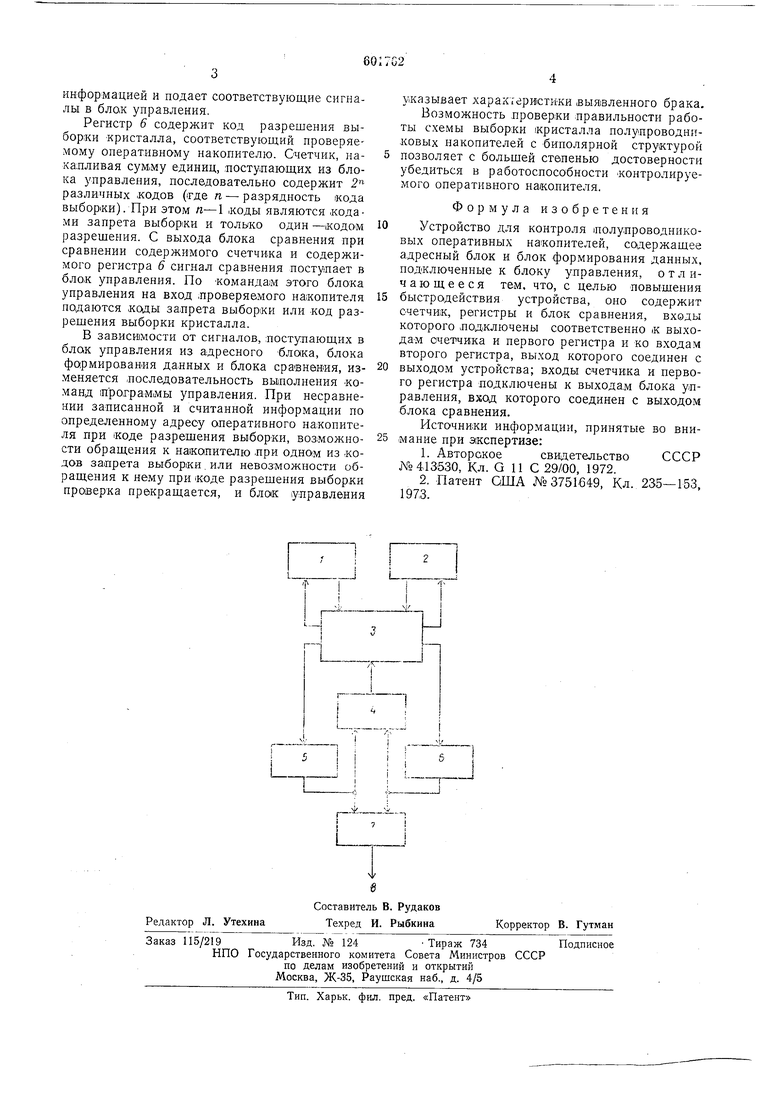

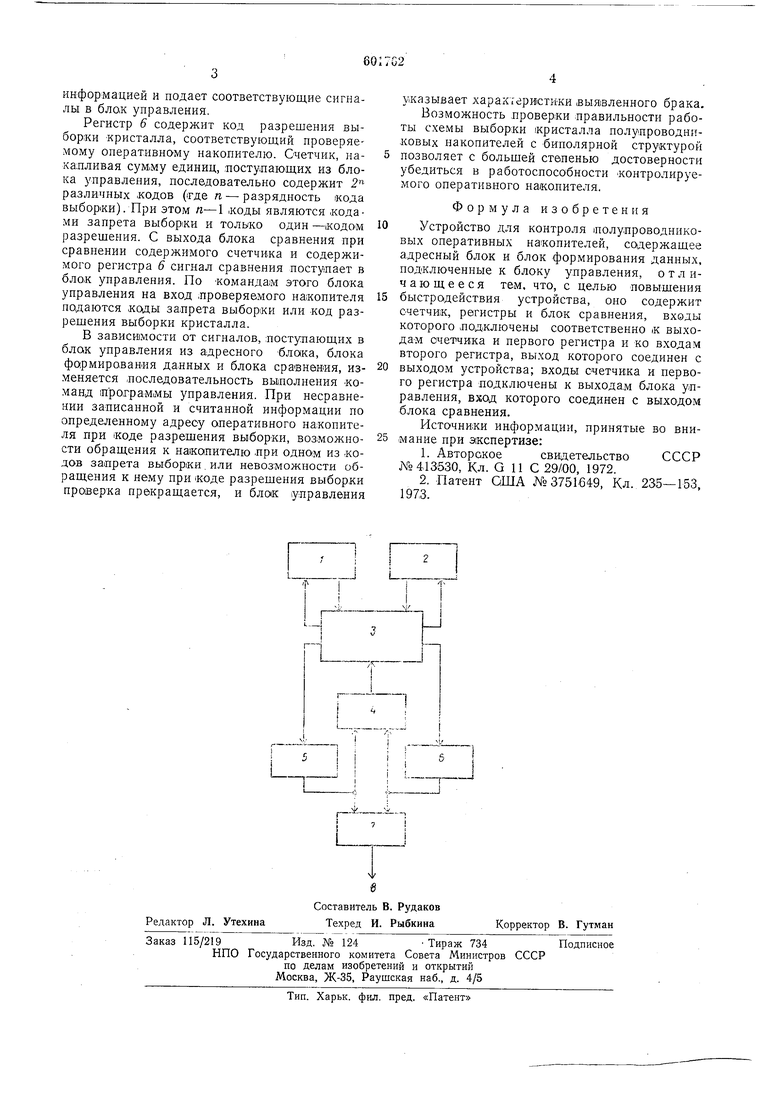

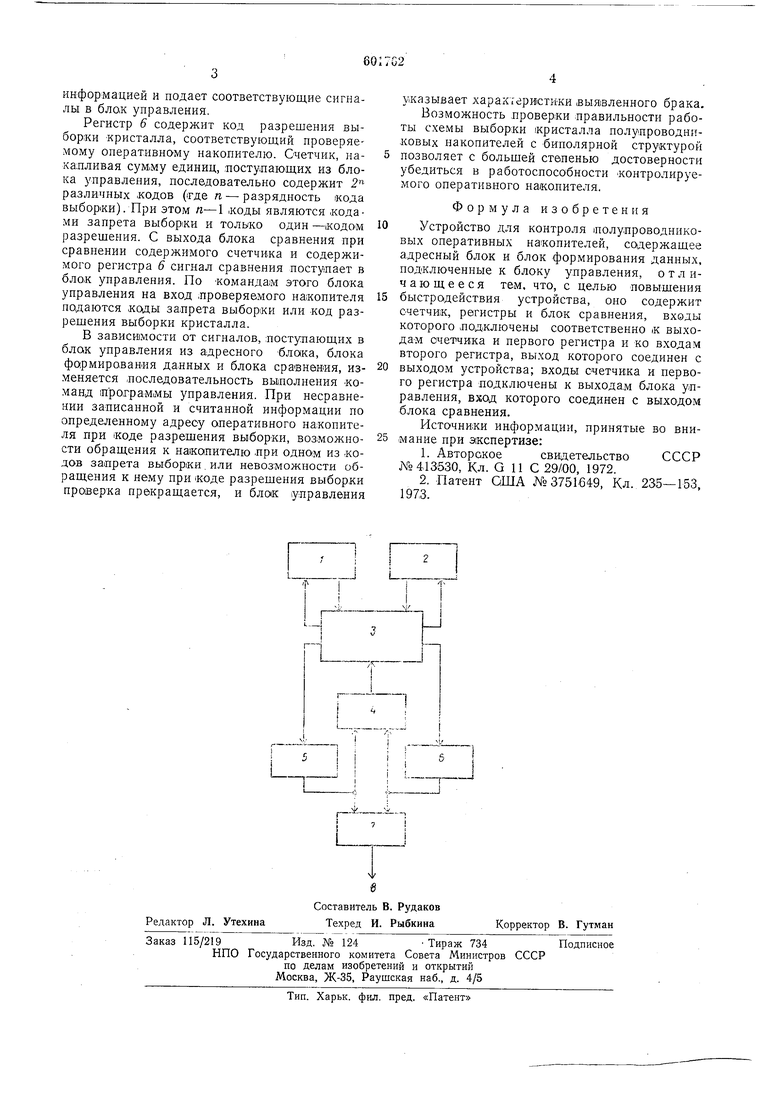

На чертеже представлена структурная схема устройства для контроля полупроводниковых оперативных накопителей.

Устройство содержит адресный блок /, блок формирования данных 2, блок управления 3, блок сравнения 4, счетчик 5, первый 6

и второй 7 .регистры.

Выходы блока управления подключены соответственно ко входам адресного блока, блока формирования данных, счетчика и регистра 6. Выходы адресного блока, блока

рования данных и -блока сравнения подключены ко входам блока управления. Выходы счетчика и регистра 6 .подключены ко входам блока сравнения и регистра 7, выход которого соединен с выходом 8 устройства.

Блок управления хранит программу с набором команд, определяющих проверку полупроводникового оперативного накопителя по определенному алгоритму. Адресный блок по командам блока управления формирует адреса накопителя, в которые записываются или с которых считываются данные. Блок формирования данных в зависимости от команд блока управления формирует записываемые данные, сравнивает их со считываемой из накопителя

информацией и подает соответствующие сигналы в блОгК управления.

Регистр 6 содержит код разрешения выборки кристалла, соответствующий проверяемому оперативному накопителю. Счетчик, пакалливая сум,му единиц, .поступающих из блока управления, последовательно содержит 2 различных .кодов (где п - разрядность «ода выборКи). При этом п-1 .коды являются .кодами запрета выборки и толыко один -жодоад разрешения. С выхода блока сравнения при сравнении содержимого счетчика и содержимого регистра 6 сигнал сравнения поступает в бло.к управления. По Команда1М этого блока управления на вход .проверяемого накопителя подаются коды запрета выборки или код разрешения выборки кристалла.

В зависи1мости от сигналов, поступающих в блок управления из адресного блока, блока

формирования данных и блока сравнения, изменяется последовательность выполнения команд 1про.грам1мы управления. При несравнении записанной и считанной информации по определенному адресу оперативного накопителя при коде разрешения вьгборки, возможности обращения к накопителю при одном из кодов запрета выборки или невозможности обращения к нему при коде разрешения выборки

проверка прекращается, и бло1К 1у:правления

указывает характеристики (Выявленного брака. Возможность проверки правильности работы схемы выборки кристалла полупроводниковых накопителей с биполярной структурой позволяет с большей степенью достоверности убедиться в работоспосОбности контролируемого оперативного накопителя.

Формула изобретения

Устройство для контроля толупроводниковых оперативных накопителей, содержащее адресный блок и блок формирования данных, подключенные к блоку управления, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик, регистры и блок сравнения, входы которого подключены соответственно к выходам счетчика и первого регистра и ко входам второго регистра, выход которого соединен с выходом устройства; входы счетчика и первого регистра подключены к выходам блока управления, вход которого соединен с выходом блока сравнения.

Источники информации, принятые во внимание при экспертизе:

1.Авторскоесвидетельство СССР №4.13530, Кл. G 11 С 29/00, 1972.

2.Патент США №3751649, Кл. 235-153, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля микросхем оперативной памяти | 1983 |

|

SU1149312A1 |

| Процессор полупроводниковой внешней памяти высокопроизводительной вычислительной системы | 1987 |

|

SU1539789A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Устройство для контроля оперативных накопителей | 1980 |

|

SU947913A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для контроля блоковОпЕРАТиВНОй пАМяТи | 1979 |

|

SU832603A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| Устройство для сопряжения ЭВМ с накопителями на магнитных дисках | 1985 |

|

SU1280644A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970480A1 |

Авторы

Даты

1978-04-05—Публикация

1976-09-27—Подача