(54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В КВАДРАТ

ДВОИЧНЫХ ЧИСЕЛ

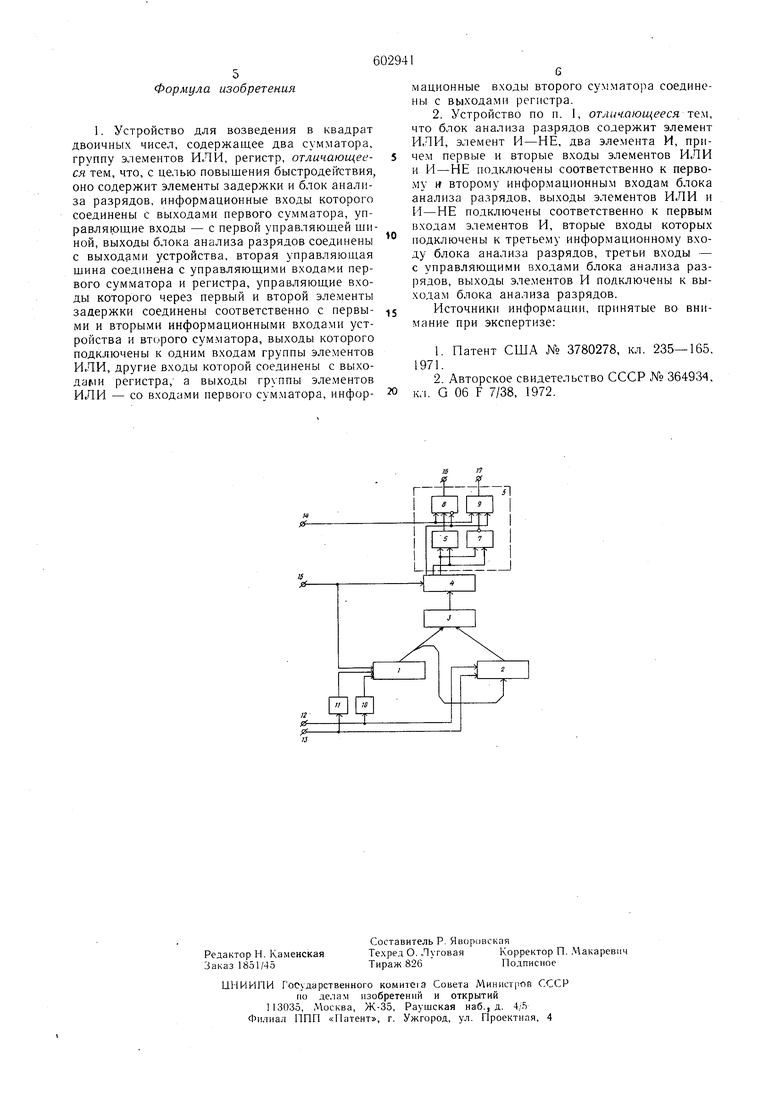

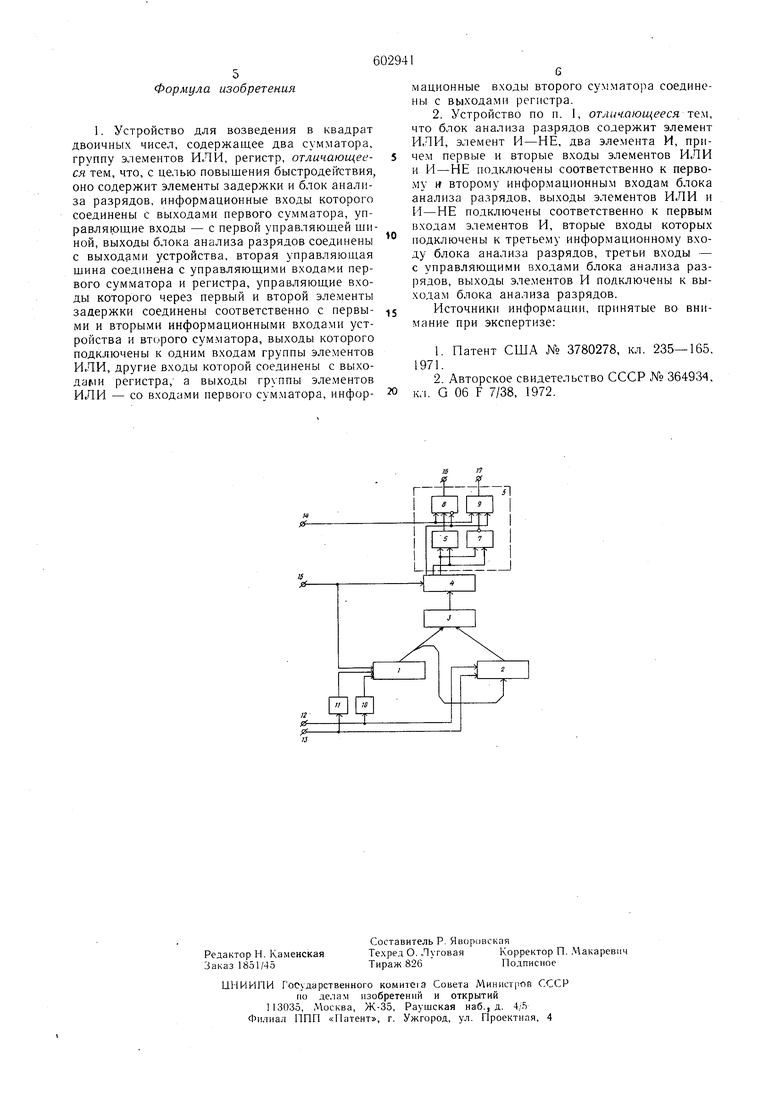

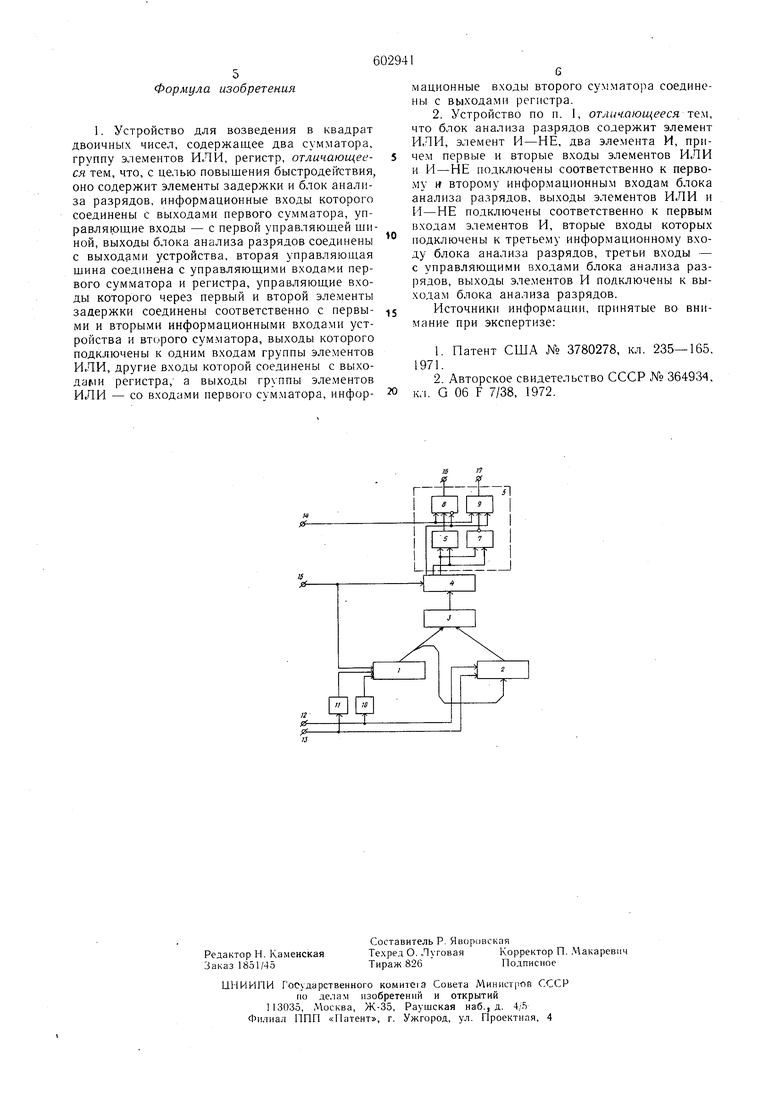

В устройство входят сдвигающий регистр 1, сумматор 2, блок элементов ИЛИ 3, сумматор 4, блок анализа разрядов 5, элемент ИЛИ б, элемент И-НЕ 7, элементы И 8, 9, элементы задержки 10, 11, информационные входы 12, 13, управляющие входы 14, 15 и выходы 16, 17.

Сдвигающий регистр 1 и сумматор 2 содержит п разрядов, где п - разрядность представления операнда. Сумматор 2 имеет знаковый разряд.

Выходы сдвигающего регистра 1 связаны со входами сумматора 2 и блока элементов ИЛИ 3. Выходы сумматора 2 подключены ко вторым входам блока элементов ИЛИ 3. Блок элементов ИЛИ 3 содержит (п + 1) элементов ИЛИ Выход первого разряда сдвигающего регистра 1 связан со входом второго элемента ИЛИ, . выход второго разряда сдвигающего регистра 1 подключен ко входу третьего элемента ИЛИ и т. д., а выход каждого i-rb разряда сдвигающего регистра 1 связан со ВХОД01М (i + l) элемента ИЛИ. Выход каждого i-ro разряда сумматора 2 связан со вторым входом i-ro элемента ИЛИ. Выходы блока элементов ИЛИ 3 подключены ко входам сумматора 4, причем выход каждого i-ro элемента ИЛИ связан со входом (i + 5)-ro разряда сумматора 4, который содержит (п + 5) разрядов. Блок анализа разрядов 5 содержит элемент ИЛИ 6, элемент И-НЕ 7, элемент запрета 8 и элемент И 9. Входы знакового разряда и разрядов целой части сумматора 4 подключены ко входам блока анализа разрядов 5. Выходы второго и третьего разрядов сумматора 4 (разряды целой части) подключены ко входам элемента ИЛИ 6 и элемента И-НЕ 7. Выход элемента ИЛИ 6 связан со входом элемента И 8. Выход элемента И-НЕ 7 подключен ко входу элемента И 9. Выход знакового разряда сумматора 4 связан с инверсным входом элемента И 8 и элемента И 9.

Устройство работает в соответствии со следующим алгоритмом

l.Ni . 2Ri-i + xi (2-Xi-,. + X; .)

Xi Xi-i + Xi 22. . ГТ,еслиН, , Y j 0, если - 1 Ni 1

11,еслиН; Л 3.R,- N;-2Y;,.

где xi - очередной разряд операнда (x, с (1,0,1}), Xi -содержимое сумматора 2 (в нем записано известное к этому времени значение операнда, (X) .

у - очередной разряд вычисляемой функции (,0,1})....

R,.i- содержимое сумматора 4 к каналу i-ro цикла вычислений,

N, - содержимое сумматора 4 в i-ом цикле вычислений, i 1,2,..., п + 3.

В исходном состоянии в старщем разряде сдвигающего регистра 1 записана единица, в остальных разряда.х - нули. В сумматорах 2, 3 записаны нули.

Вычисление функции осуществляется в (пЧ- 3) циклах, каждый из которых состоит из трех тактов. В первом такте (каждого i-ro

цикла) на информационные входы 12, 13 поступает значение очередного разряда операнда (операнд поступает, начиная со старщих разрядов). При этом, если единичный сигнал поступает на информационный вход 12, это свидетельствует о том, что очередной разряд операнда численно равен 1. Если единичный сигнал поступает на информационный вход 13, очередной разряд операнда численно равен единице..Если же единичный сигнал не поступает ни на один из информационных входов 12, 13, это свидетельствует о том, что очередной разряд операнда численно равен нулю.

Если единичный сигнал поступает на информационный вход 12, содержимое сумматора 2, сдвинутое вправо на один разряд, вычитается из содержимого сумматора 4.

Если единичный сигнал поступает на инфор.мационный вход 13, содержимое сумматора 2, сдвинутое на один разряд вправо, су.ммируется с содержимым сумматора 4.

Время, на которое сигнал задерживается в элементах задержки 10, 11, должно быть больще времени, необходимого на эту операцию. Затем сигнал с информационных входов 12. 13 снимается, появляется сигнал на выходе одного из элементов задержки 10, 11. EC.IH единичный сигнал появляется на выходе элемента задержки 10, содержимое сдвигающего регистра 1 вычитается из содержимого сумматора 2, и этот же код, сдвинутый на два разряда вправо р,ь1читает(;я Hi содержимого сумматора 4. Если единичный сигнал появляется на выходе элемента задержки 11, содержимое сдвигающего регистра 1 суммируется с содержимым сумматоров 2, 4.

Во втором такте по управляющему сигналу, поступающе.му на управляющий вход 14, производится выдача информации на выходы устройства. Если единичный сигнал появится на выходе 16, это свидетельствует о то.м, что очередной разряд требуемого значения функции численно равен 1, если единичный сигнал появится на выходе 17, очередной разряд требуемого значения функции численно равен 1. Если единичный сигнал не появится ни на одном из выходов 16 17, очередной разряд требуемого значения функции численно равен 0.

В третьем такте по управляющему сигналу, поступающему на управляющий вход 15, производится сдвиг информации в сумматоре 4 и сдвигающем регистре 1.

После этого в сумматоре 4 образуется значение RI, а в (i-fD-M разряде сдвигающего регистра 1 будет записана единица. На этом оканчивается очередной цикл вычислений. В результате (п + 3) циклов вычислений на выходах 16, 17 последовательно разряд за разрядо.м фор.мируется требуемое значение функции f(X) представленное избыточным двоичны.м кодом с цифрами 1,0,1 в каждо.м разряде. Причем, в результате выполнения (n-f 3) циклов, результат получается симметрично округленным.

Формула изобретения

1. Устройство для возведения в квадрат двоичных чисел, содержащее два сумматора, группу элементов ИЛИ, регистр, отличающееся тем, что, с целью повышения быстродействия, оно содержит элементы задержки и блок анализа разрядов, информационные входы которого соединены с выходами первого сумматора, управляющие входы - с первой управляющей щиной, выходы блока анализа разрядов соединены с выходами устройства, вторая управляющая щина соединена с управляющими входами первого сумматора и регистра, управляющие входы которого через первый и второй элементы задержки соединены соответственно с первыми и вторыми информационными входами устройства и второго сумматора, выходы которого подключены к одним входам группы элементов ИЛИ, другие входы которой соединены с выходами регистра, а выходы группы элементов ИЛИ - со входами перво1Ч) сумматора, информационные входы второго сумматора соединены с выходами регистра.

2. Устройство по п. 1, отлич.ающееся те, что блок анализа разрядов содержит элемент ИЛИ, элемент И-НЕ, два элемента И, причем первые и вторые входы элементов ИЛИ и И-НЕ подключены соответственно к первому и второму информационным входам блока анализа разрядов, выходы элементов ИЛИ и И-НЕ подключены соответственно к первым входам элементов И, вторые входы которых подключены к третьему информационному входу блока анализа разрядов, третьи входы - с управляющими входами блока анализа разрядов, выходы элементов И подключены к выходам блока анализа разрядов.

Источники информации, принятые во внимание при экспертизе:

1.Патент США № 3780278, кл. 235-165. 1971.

2.Авторское свидетельство СССР № 364934, кл. G 06 F 7/38, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для алгебраического сложения чисел | 1976 |

|

SU638959A1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

| Устройство для вычисления обратной величины | 1984 |

|

SU1262477A1 |

| Устройство для деления | 1988 |

|

SU1513444A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

Авторы

Даты

1978-04-15—Публикация

1976-08-16—Подача