ю

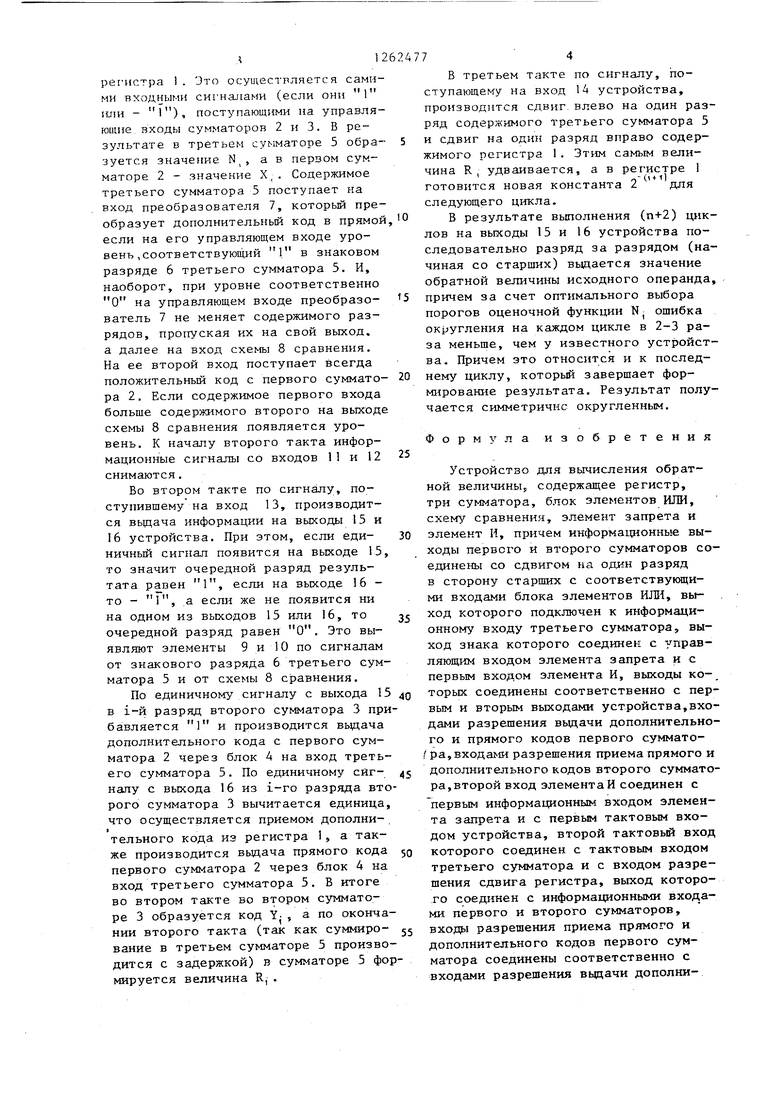

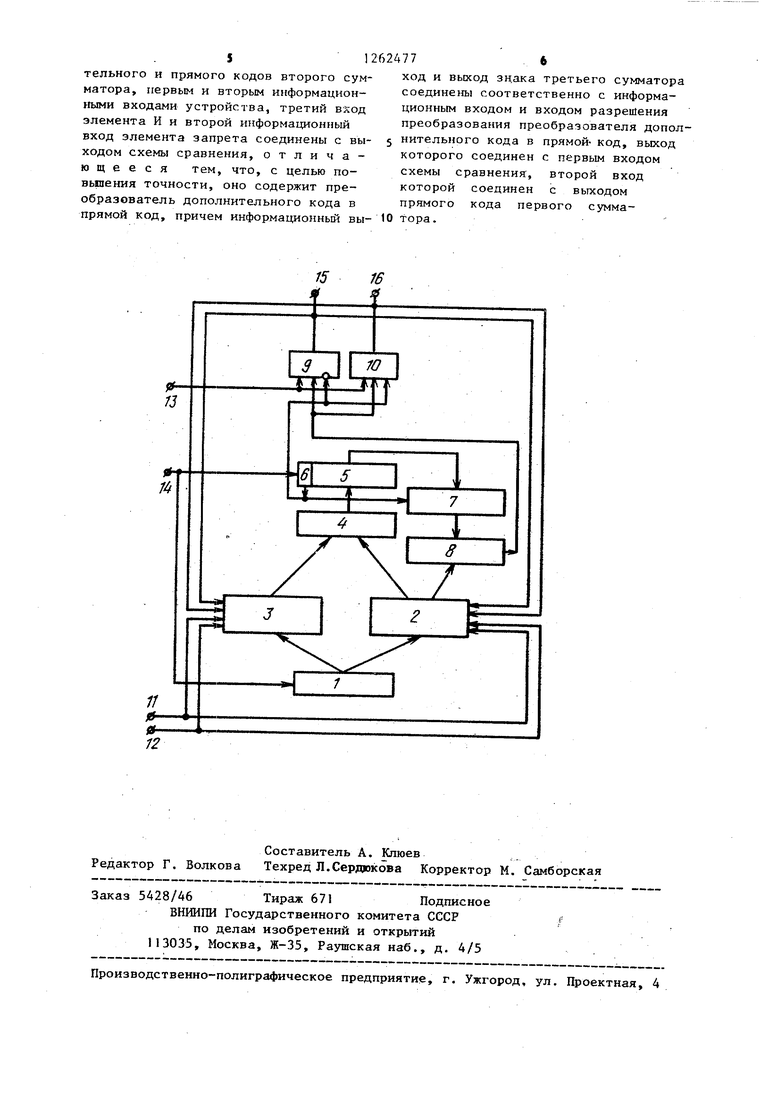

О) IS9 U Изобретение относится к вычислительной технике и может быть исполь зовйно в цифровых вычислительных и управляющих системах. Целью изобретения является повышение точности. На чертеже представлена схема ус ройства для вычисления обратной величины. Устройство для вычисления обратной величины содержит регистр 1,сум маторы 2 и 3, блок 4 элементов ИЛИ, сумматор 5, знаковьш разряд 6 сумматора 5, преобргчзователь 7 дополни тельного кода в прямой код, схему 8 сравнения, элемент 9 запрета, эле мент И 10, информационные входы 11 и 12 устройства, тактовьк входы 13 и 14 устройства, выходы 15 и 16 уст ройства. Регистр 1, сумматоры 2 и 3, преобразователь 7 дополнительного кода в прямой код, схема 8 сравнения име ют (п+1) двоичный разряд (п - разрядность аргумента и результата без знака). Сумматор 5 и блок 4 элементов ИЛИ имеют (п+2) двоичных разряда. В качестве сумматоров 2, 3 и 5 используются накапливающие сумматоры, работающие в дополнительном коде Суммирование в третьем сумматоре 5 производится с задержкой за счет при менения в его регистре двухтактных триггеров. На входах 13 и 14 появляются два сдвинутые один относител но другого на треть периода прямоугольные импульсы напряжения с амплитудой, соответствующей уровню. со скважностью около 6. Первый из импульсов (вход 13) сдвинут во вре;мени на треть периода по отношению к моменту появления импульсов на вх дах 11 и 12. Для представления операнда X и ре зультата Y 1/X применяется избыточная симметричная двоичная система счисления с цифрами {}, О, l} . Устройство работает в соответстВИИ со следующим алгоритмом N, 2R.,,- 2Y..,X, Х, Х,, + Х,-2- , f, если N, -X, У j О, если -X, N, i t , если N j X ,. Y м + У, - 2 R, N - 2Х, у, (i 1,2,...), где X - очередная цифра операнда; Xj - содержимое сумматора 2 в i-M цикле вычислений; У, - очередная цифра результата; Y; - содержимое cyMifaTopa 3 в i-м цикле вычислений; R - содержимое сумматора 5 к началу i-ro цикла вычислений; N - содержимое сумматора 5 в i i-M цикле вычислений. Устройство работает следующим образом . Исходное состояние: N 0,5; Xg Y 0. На величину аргумента накладываются ограничения: 2 У. i - i . В начальном состоянии в n-t-i разряде регистра 1 записана I, в остальных разрядах - О. Кроме того, в п-й разряд сумматора 5 занесена 1, его остальные разряды - в О. Обратная величина исходного операнда вычисляется за несколько циклов, один цикл дает один разряд результата. Число циклов выбирается в зависимости от требуемой точности результата. Так как результат рациональное число, он не имеет конечного (п+2)-разрядного представления в двоичной системе. Учитьтая, что аргумент X подается округленным до п разрядов, число верных знаков результата также п, а получается он с задержкой на два разряда, поэтому окончательный результат формируется за (п+2) циклов вычисления. Каждый цикл состоит из трех тактов. В первом такте каждого i-ro цикла на входы 11 и 12 устройства поступает очередной разряд операнда (операнд поступает, начиная со старших разрядов). При этом, если сигнал поступает на информадионньй вход 11, это свидетельствует о том, что оче- редной разряд операнда равен 1. Если сигнал поступает на вход 12, очередной разряд аргумента .равен Г. Если же сигнала нет ни на одном из входов 11 и 12, очередной разряд операнда численно равен О. В зависимости от сигнала, поступившего на входы 11 и 12, содержимое второго сумматора 3 прибавляется ипи вычитается из содержимого третьего сумматора 5 со сдвигом на один разряд влево. Кроме того, к содержимому первого сумматора 2 прибавляется прямой или дополнительный код содержимого регистра 1 . Это осуи;естрляется самими входными сигналами (если они 1 шш - 1), поступающими на управляющие входы сумматоров 2 и 3. В результате в третьем cy iмaтope 5 обра- зуется значение N, а в первом сумматоре 2 - значение X,. Содержимое третьего сумматора 5 поступает на вход преобразователя 7, которьм преобразует дополнительный код в прямой если на его управляющем входе уровень , соответствующий 1 в знаковом разряде 6 третьего сумматора 5. И, наоборот, при уровне соответственно О на управляющем входе преобразователь 7 не меняет содержимого разрядов, пропуская их на свой выход, а далее на вход схемы 8 сравнения. На ее второй вход поступает всегда положительный код с первого сумматора 2. Если содержимое первого входа больше содержимого второго на выходе схемы 8 сравнения появляется уровень. К началу второго такта информационные сигналы со входов 11 и 12 снимаются. Во втором такте по сигналу, поступившему на вход 13, производится выдача информации на выходы I5 и 16 устройства. При этом, если единичный сигнал появится на выходе 15 то значит очередной разряд результата равен 1, если на выходе 16 то - 1, а если же не появится ни на одном из выходов 15 или 16, то очередной разряд равен О. Это выявляют элементы 9 и 10 по сигналам от знакового разряда 6 третьего сумматора 5 и от схемы 8 сравнения. По единичному сигналу с выхода 15 в i-й разряд второго сумматора 3 при бавляется 1 и производится вьщача дополнительного кода с первого сумматора 2 через блок 4 на вход третьего сумматора 5. По единичному сигналу с выхода 16 из i-ro разряда вто рого сумматора 3 вычитается единица что осуществляется приемом дополнительного кода из регистра 1, а также производится выдача прямого кода первого сумматора 2 через блок 4 на вход третьего сумматора 5. В итоге во втором такте во втором сумматоре 3 образуется код YJ, а по оконча нии второго такта (так как суммирование в третьем сумматоре 5 произво дится с задержкой) в сумматоре 5 фо мируется величина R,. 7 4 В третьем такте по сигналу, поступающему на вход 14 устройства, производится сдвиг, влево на один разряд содержимого третьего сумматора 5 и сдвиг на один разряд вправо содержимого регистра 1. Этим самым величина R, удваивается, а в регистре 1 готовится новая константа I для следующего цикла. В результате выполнения (п+2) циклов на выходы 15 и 16 устройства последовательно разряд за разрядом (начиная со старших) выдается значение обратной величины исходного операнда, причем за счет оптимального выбора порогов оценочной функции N ошибка округления на каждом цикле в 2-3 раза меньше, чем у известного устройства. Причем это относится и к последнему циклу, который завершает формирование результата. Результат получается симметрично округленным. Формула изобретения Устройство для вычисления обратной величины, содержащее регистр, три сумматора, блок элементов ИЛИ, схему сравнения, элемент запрета и элемент И, причем информационные выходы первого и второго сумматоров соединены со сдвигом на один разряд в сторону старших с соответствующими входами блока элементов ИЛИ, выход которого подключен к информационному входу третьего сумматора, выход знака которого соединен с управляющим входом элемента запрета и с первым входом элемента И, выходы которых соединены соответственно с первым и вторым выходами устройства,входами разрешения выдачи дополнительного и прямого кодов первого сумматора, входами разрешения приема прямого и дополнительного кодов второго сумматора, второй вход элемента И соединен с первым информационным входом элемента запрета и с первым тактовым входом устройства, второй тактовьй вход которого соединен с тактовым входом третьего сумматора и с входом разрешения сдвига регистра, выход которого соединен с информационными входами первого и второго сумматоров, входа разрешения приема прямого и дополнительного кодов первого сумматора соединены соответственно с входами разрешения вьщачн дополни$ 1

тельного и прямого кодов второго сум матора, первым и вторым информационными входами устройства, третий вход элемента И и второй информационный вход элемента запрета соединены с вы ходом схемы сравнения, отличающееся тем, что, с целью повьюения точности, оно содержит преобразователь дополнительного кода в прямой код, причем информационный вы

624776

ход и выход зн.ака третьего сумматора соединены соответственно с информационным входом и входом разрешения преобразования преобразователя допол5 нительного кода в прямой- код, выход которого соединен с первым входом схемы сравнения:, второй вход которой соединен с выходом прямого кода первого сумма10 тора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Устройство для вычисления функции | 1976 |

|

SU662937A1 |

| Вычислительное устройство | 1983 |

|

SU1173411A1 |

| Устройство для вычисления квадратного корня | 1987 |

|

SU1481753A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

| Устройство для вычисления корня квадратного из суммы квадратов | 1989 |

|

SU1695295A1 |

| Устройство для возведения в квадрат двоичных чисел | 1976 |

|

SU602941A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Арифметическое устройство | 1977 |

|

SU669353A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в управляющих и информационно-измерительных системах. Цель изобрететгая - повьппение точности устройства. Поставленная цель , достигается тем, что устройство для вычисления обратной величины, содержащее три сумматора, регистр, блок элементов ИЛИ, элементы И и запрета, схему сравнения, содержит преобразователь дополнительного кода в прямой код с соответствующими связями. В устройстве использовано представление входных и выходных величин в последовательном зиакоразрядном двоичном коде с цифрами (-1, О, И. 1 ил. Q - «

| ВСЕСОЮЗНАЯ I | 0 |

|

SU362296A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления обратной величины | 1976 |

|

SU732861A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-10-07—Публикация

1984-12-12—Подача