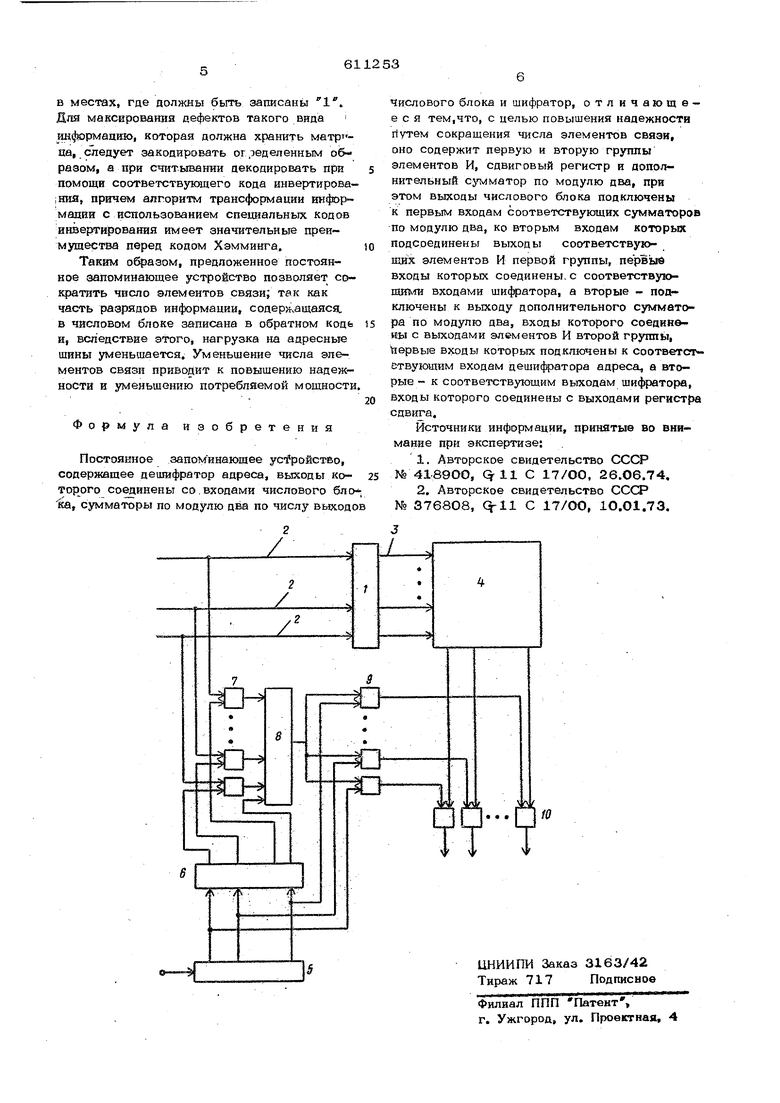

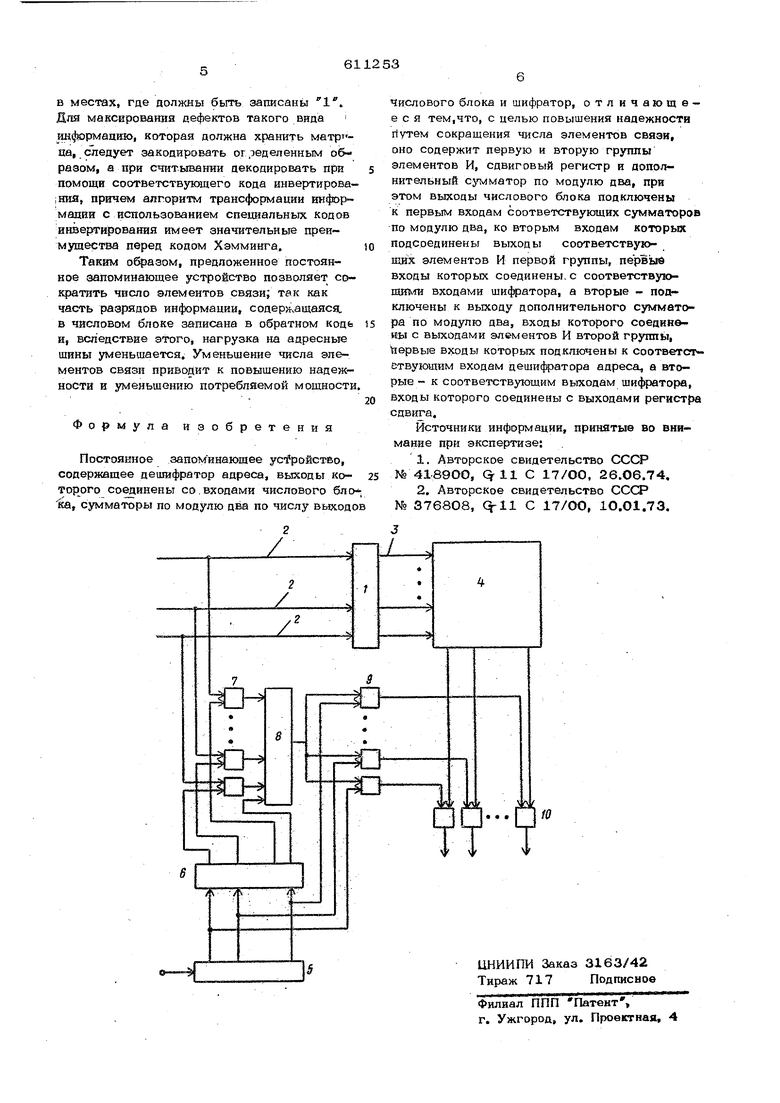

Изобретение относится к области вьяис лительной техники, в частности к постоянным запоминающим устройствам (ПЗУ). Известны постоянные запоминающие уст ройства i, 2 . Одно из известных ПЗУ |lj содержит числовой блок с большим числом элементов связи, либо с большим числом проиттых сердечников, вход которо соедннби с яеига(|ратором, а выход- с усилителем считывания, формирователи адресных токов. Недостатком известного устройства является большое потребление мощности, а также неравномерность нагрузки на адрес. ные шины. Известно и другое постоянное запоминающее устройство 2 , которое содержи дешифратор адреса, выходы которого соодияены со входами числового блока, шифрато и сумматоры по модулю два по числу вь ходов числового блока. Недостатками известного устройства являются большое число элементов связи используемых при реализации устройства, большая разрядность ЧНСЛОЕЮГО блока, низкая надежность устройства. С целью повышения надежности устройства путем сокращения числа элементов связи пред; агаем ое постоянное запоминающее устройство содержит первую и вторую группы элементов И, сдвиговый регистр и дополнительный сумматор по модулю два, при этом выходы числового блока подключены к первым входам cooff- ветствующих сумматоров по модулю два, ко вторым входам которых подсоединены выходы соответствукидих элементов И первой группы, первые входы которых соединены с соответствующими входами шифратора, а вторые - подключены к выходу дополнительного сумматора по модулю два, входы которого соединены с выходами впементов И второй группы, первые входы которых подключены к соответствующим входам дешифратора адреса, а вторые - к соответствукшим выходам шифратора, входы которого соединены с выходами регистра . На чертеже нэббражена 6ло&. крсп лагаемого постоянного запомпнающегэ ;,СГ ройетва. Постоянное запок1ипаюшее устройства со держит дешифратор адреса 1, кодовые шииь 2, адресные шины 3, числовой блок 4, регистр сдвига 5, шифратор б, BTopjio группу элементов И 1, дополнительный cj /JMa- тор по модулю два 8, первую группу элементов И 9, сумматоры по модулю два 1С .Дешифратор адреса 1 через адресные шины 3 подключен ко входам числового блока 4,. выходы которого соединены с пер выми входами соответствующих cx-TviMaropoB по модулю д1за 10, вторьте входы -которых подключены к выходам соответствуюшнх элементов И пфвой группы 9, первые входы которьж подсоединены к соответствуьэ-щим входам шифратора 6, а вторые - к выходу дополнительного . сумматора по Модулю два 8, входы которого подсоединены к вьвсодам соответствующих элементов И второй группы 7, первые входы которых подсоединены к соответствующим входам 2 дешифратора 1, а вторые входы к соответст вуюшим выходам шифратора б, входы которого подсоединены к выходам регистра .5„ Предлагаемое ПЗУ работает следующим образом. Пусть, например, в iircjioBovf бло-ке 4 хранится двоичная ипфор.мацяя, зако дированная TSKIIM образом, что в каждом разряде машинного С ова-цифра записана в . прямом или в обратном коде с налью сокргз ния количества записанных enj-nnm цо М -и:к1-мума, Следовательно5 при счнтываннк jreобхояимо яроиввести поразрядную операиию инвертирования там, где это требуется при помощи, так называемого, кода тп перт-нрования. Код иивертироваи 5Я -выбирается спедующ№1 образом. Часть разрядов j -I-G . столбца, а Cij -го. разряда слов, которое тр буется записать в числовой блок) рб7зед,и няются в группу и ес.ни число едтгани- в ©той группе больше числа нулей .группа в числовой блок/аписьшается в обратном коде, а в определенном разряде кода ЁПЭертирования зашю.ывается едапила, Сггос объединения разрядов кода столбца в rf..ynnb и число групп, вьгбирается аналогичным oi5 разом, как и В коде Хэмминга, .где число. групп К определяется из вьтражеикя: ,(pii) где Р - разрядность кодов столбл.о. . Количество кодов инвертирования равно, соответетвенноа количеству столбиов чксло вого блока. Коды инвертирования -согласно схеме поступай-т. с выхода шй рагора .ёп , В режиме выдачи информация, хранящаяс в числовом блоке, корректируется слеяуто шим образом. Не KOjiOHT f Ol-peCfS я nOCTJ TfQQT жод ад;:йса -ой ячейзш, содержимое кото Р .г: :ги:5у;;тся с-|лтать, ка зхоя дегш-гфратора snpoc.Q ,1, на перрлда в,ходы элементом И второй грулпы 7, На вторые вкоды зле-vsenroB И второй группьз 7. с вькояа шифратора 6 поступает код инвертирования | -го столбца, т,е„ д ГО раэр.яаа считьшаемого слова в результате появления сигнала еди нииа на j --ОМ входе шйфратора 6 с вы копя рэгис ра сдвига- 5, В результате вььполпеайя эле1..ШЕд-амк И второй группы 7 операции пора.зрядного логического ут.ноже™ ТП1Я н.а.д кодом адреса м кодом йнвартироваиня, па гзксЛ дополгительпого сумматора по модулю два 8 цост5яает определенное копи-tjecTBo 55 .J/. Если количество едишпг нечеткое, то па выходе дополнительного cj-iv-sMsi npa по мояул1-э дш 8 по.йвляется код 1. поступает на вторые входы элементов И первой группы 9 к на выходе одного Ji3 элементов И первой группы 9, а именно т-сго, Г1ерв.ьтй вход которого Соединен с У -ь. ретастра сдвига S появляется код 1 и гюстуиаетна второй вкод одного из сумматоров, ио мояун-ю - дна 10. иа первый вход которого поса упа8т Код J .. разряда -1 -гослрв&.хранящегаеявчкс новом блоке 4, Таким образоыв даяном раз-ряде прон-сходЬт лявер-тированке. Для |. столе.иа сущест-Бубт цругой код ин-вертировавия, пп- /ц/о.пожим т.5Лой, ЧТО в р-езультате вьтпол- jieiniK второй грртпой аяементов И 7 оппрзшп nnpR3p«ni:oro логического умножеН я Л njcon пополнительного cyN MBTOpa по модулю дЕа 8 доступгзетчеткое количество ei.. На выходе его код., на вто- nriTv входе-одного из сумматоров, по моду .:-:--; -,;: ; .;п) ; -Л разряда тоже код нуля и, . )oqoM, цифра этого разряда { -го плгтя ч.-чтп-тд.ается без иемеиения. Итак, коц :::локь хранящегося гю t му адресу Ol:o o блоке 4 счктмваотся последовательцо (с пекоторьы интервалом времени) разряд за разрядом с коррекцией тех рааряпов, Гдо требуется HDK эамепе числового блока 4 или при пэмеиеиЕп информации в нем, в ши4раторе 6 ааписываютея новые значеш1Я кодов ин- - йсловой блок из.вестного вертировап1 . VCTDDiicTBa имеет 2 запоминающих элементов а числовой блок предлагаемого устройства - только ft запоминающих элементов,, что облегчает его интегральное . исполпенне,, В случае применения ч1-1слового блокгг ъ 51нтегралгзном исполнении в виде матрзшы .возможно использование дефектньзх матрип, .г;,е, таких где присутствуют дефекты вица отсутствие элемегггов связи в мес-гах, где должны быть записаны 1. Для макснрования дефектов такого вида шсформадию, Которая должна хранить матрт1И, следует закодировать ог.эеделенным образом, а при считывании декодировать при помощи соответствующего кода инвертироваjima, причем алгоритм трансформации ннформадии с использованием специальных кодов инвертирования имеет значительные преимущества перед кодом Хэмминга. Таким образом, предложенное постоянное запоминающее устройство позволяет сократить число элементов связи; теге как часть разрядов информации, содержащаяся в числовом блоке записана в обратном кодь и, вследствие этого, нагрузка на адресные шины уменьшается. Уменьшение числа элементов связи приводит к повышению надежности и уменьшению потребляемой мощности Формула изобретения Постоянное запоминающее устройство, содержащее дешифратор адреса, выходы котор ого соединены со.входами числового бло ка, сумматоры по модулю два по числу выходо Числового блока и шифратор, отличающееся тем,что, с целью повышения надежности путем сокращения числа элементов связи, оно содержит первую и вторую группы элементов И, сдвиговый регистр и дополнительный сутиматор по модулю два, при этом выходы числового блока подключены к первым входам соответствующих сумматоров по модулю два, ко вторым входам которых подсоединены выходы соответствующих элементов И первой группы, первые входы которых соединены, с соответствук щи те входами ши(}чэатора, а вторые - подключены к выходу дополнительного сумматора по модулю два, входы которого соедин кы с выходами элементов И второй группы, нервые входы которых подключены к соответст бтвующим входам дешифратора адреса, а вторые - к соответствующим выходам шифратора, входы которого соединены с выходами регистра сдвига. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 418900, QUO 17/00. 26.06.74. 2.Авторское свидетельство СССР № 376808, q-11 С 17/ОО, 10.О1.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU649039A1 |

| Постоянное запоминающее устройство с коррекцией считываемой информации | 1977 |

|

SU720511A1 |

| Запоминающее устройство с контролем и коррекцией информации | 1983 |

|

SU1109809A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU641499A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU733028A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Постоянное запоминающее устройсство | 1977 |

|

SU637869A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

Авторы

Даты

1978-06-15—Публикация

1976-10-25—Подача