1

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам.

Известно постоянное запоминающее устройство, содержащее числовой блок, который характеризуется большим числом элементов связи.

Однако большое количество элементов связи приводит к неравномерности нагрузки на адресные шины и большой потребляемой мощности 1.

Наиболее близким техническим решением ю к изобретению является постоянное запоминающее устройство, содержащее накопитель с дефектными запоминающими элементами, подключенный к регистру адреса и регистру слова, регистр контрольных разрядов, блок восстановления информации по контрольным разрядам, входы которого подключены к соответствующим выходам регистра контрольных разрядов, а выходы - ко входам регистра слова и блок управле J - жж 20

Недостаток этого устройства - неэффективное использование емкости накопителя с дефектными запоминающими элементами, так как необходимо большое количество дополнительных разрядов (избыточность) для коррекции ошибок.

Целью изобретения является упрощение и повышение надежности устройства.

Поставленная цель достигается тем, что устройство содержит элементы НЕ и элементы И, первые входы которых подключены к выходам регистра адреса, вторые входы - к первому выходу блока управления, выходы одних из элементов И соединены с первыми входами регистра слова, выходы других элементов И подключены через элементы НЕ ко вторым входам регистра слова, третьи входы регистра слова соединены со вторьш и третьим выходами блока управления.

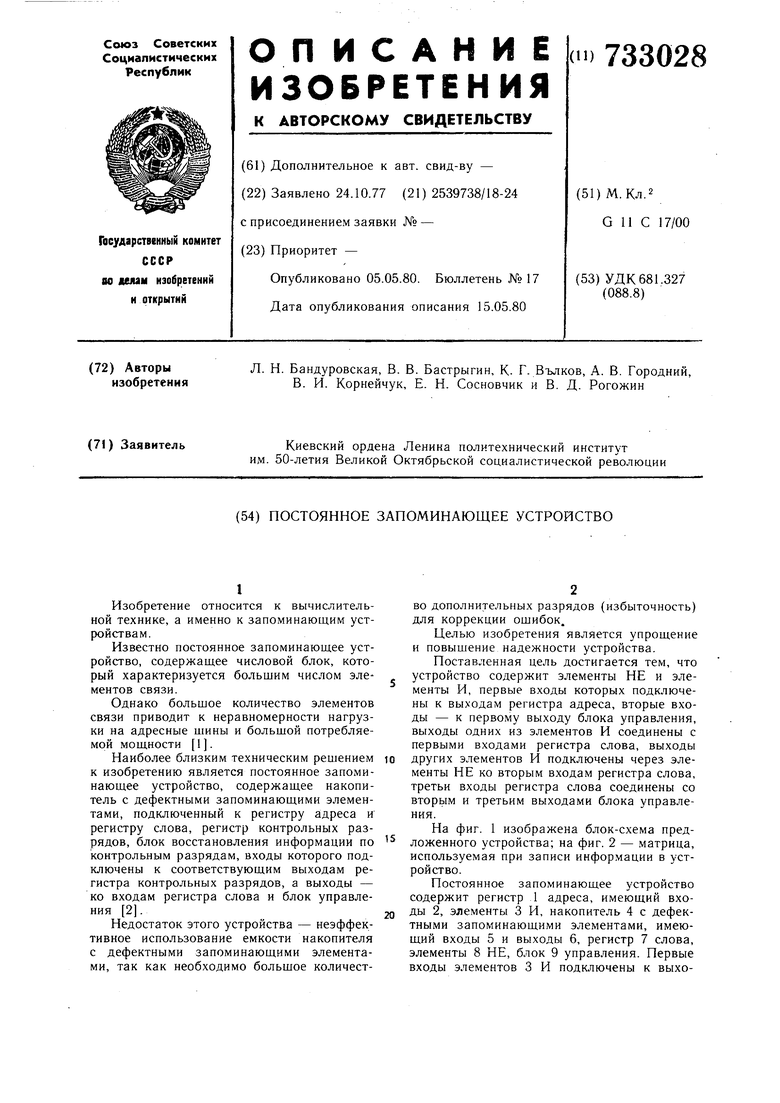

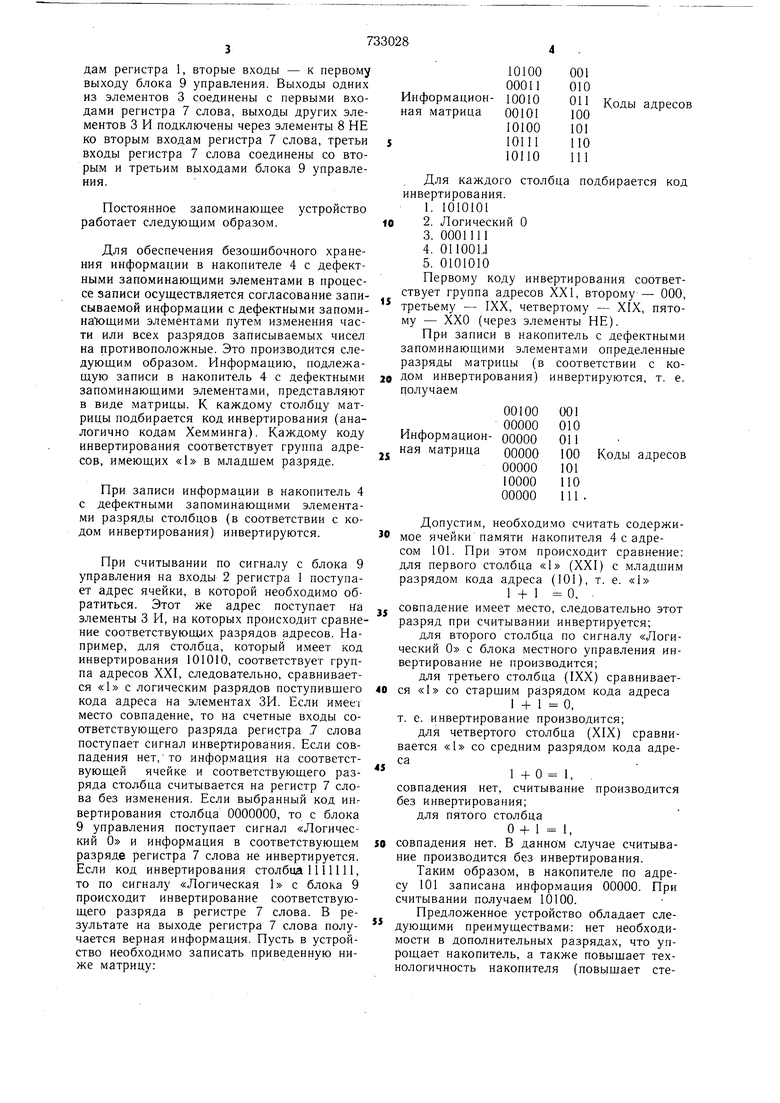

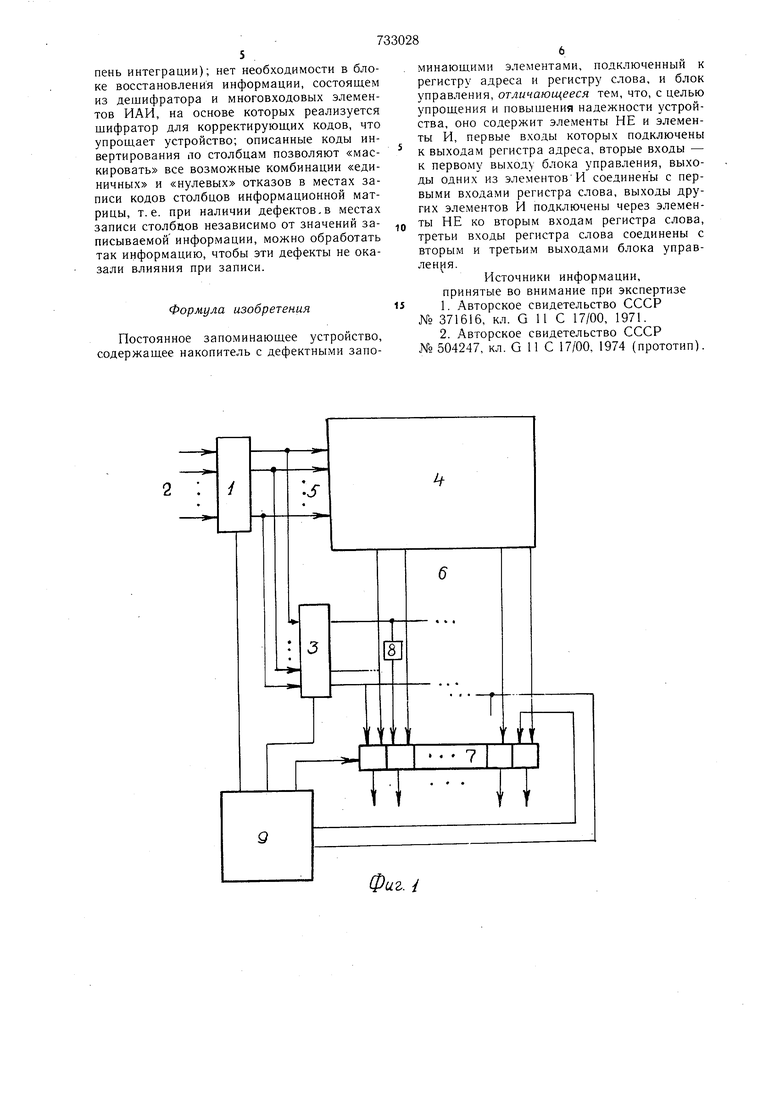

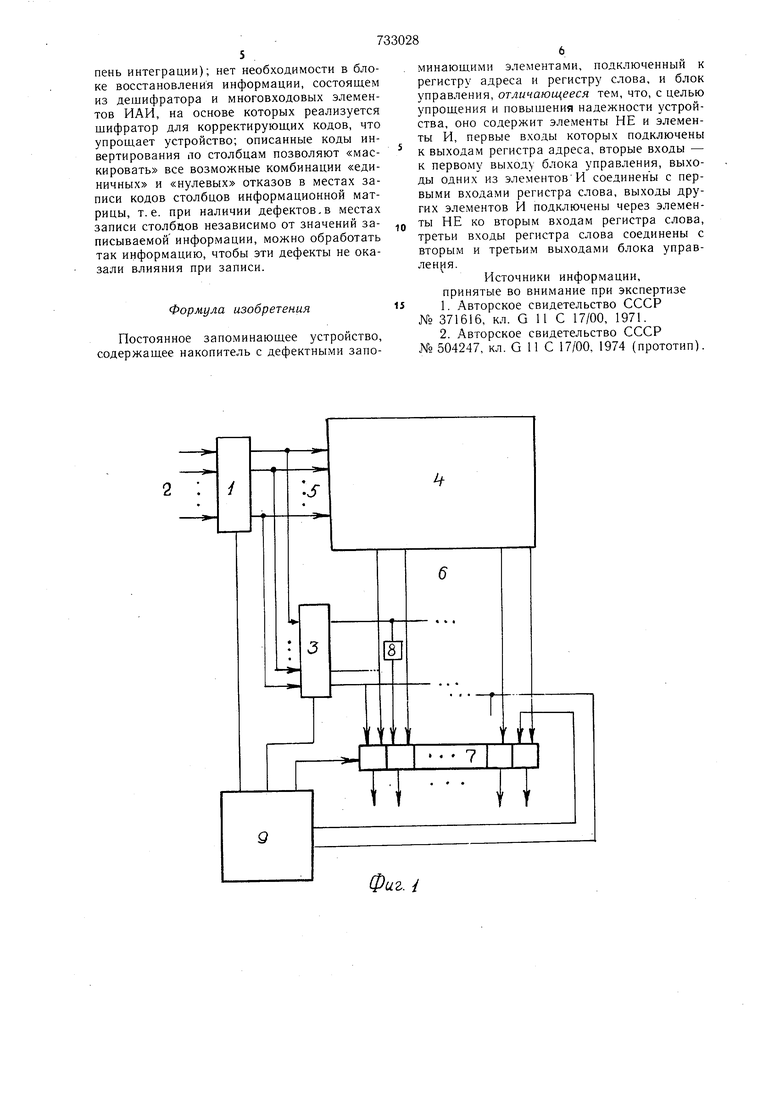

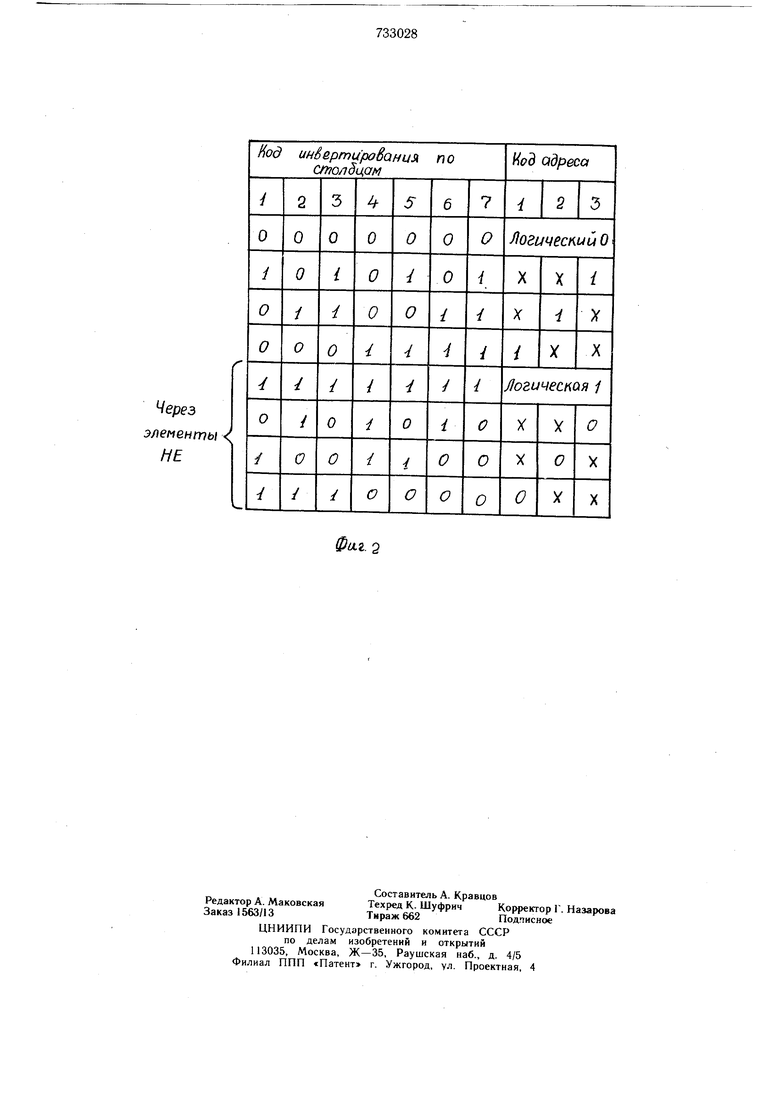

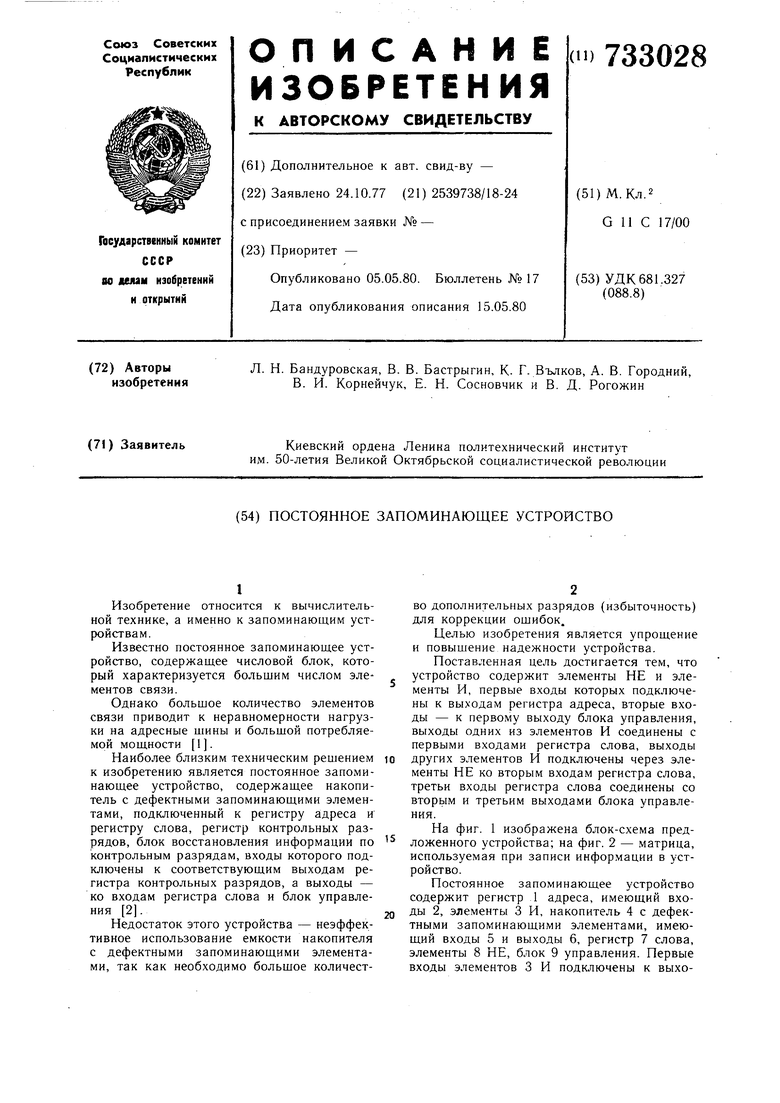

На фиг. 1 изображена блок-схема предложенного устройства; на фиг. 2 - матрица, используемая при записи информации в устройство.

Постоянное запоминающее устройство содержит регистр 1 адреса, имеющий входы 2, элементы 3 И, накопитель 4 с дефектными запоминающими элементами, имеющий входы 5 и выходы 6, регистр 7 слова, элементы 8 НЕ, блок 9 управления. Первые входы элементов 3 И подключены к выходам регистра 1, вторые входы - к первому выходу блока 9 управления. Выходы одних из элементов 3 соединены с первыми входами регистра 7 слова, выходы других элементов 3 И подключены через элементы 8 НЕ ко вторым входам регистра 7 слова, третьи входы регистра 7 слова соединены со вторым и третьим выходами блока 9 управления.

Постоянное запоминающее устройство работает следующим образом.

Для обеспечения безощибочного хранения информации в накопителе 4 с дефектными запоминающими элементами в процессе записи осуществляется согласование записываемой информации с дефектными запоминающими элементами путем изменения части или всех разрядов записываемых чисел на противоположные. Это производится следующим образом. Информацию, подлежащую записи в накопитель 4 с дефектными запоминающими элементами, представляют в виде матрицы. К каждому столбцу матрицы подбирается код инвертирования (аналогично кодам Хемминга). Каждому коду инвертирования соответствует группа адресов, имеющих «1 в младщем разряде.

При записи информации в накопитель 4 с дефектными запоминающими элементами разряды столбцов (в соответствии с кодом инвертирования) инвертируются.

При считывании по сигналу с блока 9 управления на входы 2 регистра 1 поступает адрес ячейки, в которой необходимо обратиться. Этот же адрес поступает на элементы 3 И, на которых происходит сравнение соответствующих разрядов адресов. Например, для столбца, который имеет код инвертирования 101010, соответствует группа адресов XXI, следовательно, сравнивается «1 с логическим разрядов поступивщего кода адреса на элементах ЗИ. Если имееч место совпадение, то на счетные входы соответствующего разряда регистра .7 слова поступает сигнал инвертирования. Если совпадения нет,ТО информация на соответствующей ячейке и соответствующего разряда столбца считывается на регистр 7 слова без изменения. Если выбранный код ин.вертирования столбца 0000000, то с блока 9 управления поступает сигнал «Логический О и информация в соответствуюц1ем разряде регистра 7 слова не инвертируется. Если код инвертирования столбца 1111111, то по сигналу «Логическая 1 с блока 9 происходит инвертирование соответствующего разряда в регистре 7 слова. В результате на выходе регистра 7 слова получается верная информация. Пусть в устройство необходимо записать приведенную ниже матрицу:

10100

001 00011 010

нформацион10010011

Коды адресов 00101 100 ая матрица 10100 101 10111 ПО 10110 111

Для каждого столбца подбирается код инвертирования.

1. 1010101 2. Логический О

3.0001111

4.01100 и

5.0101010

Первому коду инвертирования соответствует группа адресов XXI, второму - 000, третьему - IXX, четвертому - XIX, пятому - ХХО (через элементы НЕ).

При записи в накопитель с дефектными

запоминающими элементами определенные

разряды матрицы (в соответствии с кодом инвертирования) инвертируются, т. е.

получаем

00100001

00000010

Информацион- 00000011

ная матрица ООООО100 Коды адресов

00000101

10000ПО

ООООО111.

Допустим, необходимо считать содержимое ячейки памяти накопителя 4 с адресом 101. При этом происходит сравнение; для первого столбца «1 (XXI) с младщим разрядом кода адреса (101), т. е. «1

1 + 0, .

совпадение имеет .место, следовательно этот разряд при считывании инвертируется;

для второго столбца по сигналу «Логический О с блока местного управления инвертирование не производится;

для третьего столбца (IXX) сравнивается «1 со старщим разрядом кода адреса

1 + , т. е. инвертирование производится;

для четвертого столбца (XIX) сравнивается «1 со средням разрядом кода адре1 -f О 1, .

совпадения нет, считывание производится без Инвертирования;

для пятого столбца

0 + 1 1,

совпадения нет. В данном случае считывание производится без инвертирования.

Таким образом, в накопителе по адресу 101 записана информация ООООО. При считывании получаем 10100.

Предложенное устройство обладает следующими преимуществами: нет необходимости в дополнительных разрядах, что упрощает накопитель, а также повышает технологичность накопителя (повыщает степень интеграции); нет необходимости в блоке восстановления информации, состоящем из дешифратора и многовходовых элементов ИЛИ, на основе которых реализуется шифратор для корректирующих кодов, что упрощает устройство; описанные коды инвертирования ло столбцам позволяют «маскировать все возможные комбинации «единичных и «нулевых отказов в местах записи кодов столбцов информационной матрицы, т.е. при наличии дефектов.в местах записи столбцов независимо от значений записываемой информации, можно обработать так информацию, чтобы эти дефекты не оказали влияния при записи.

Формула изобретения

Постоянное запоминающее устройство, содержащее накопитель с дефектными запоминающими элементами, подключенный к регистру адреса и регистру слова, и блок управления, отличающееся тем, что, с целью упрощения и повышения надежности устройства, оно содержит элементы НЕ и элементы И, первые входы которых подключены к выходам регистра адреса, вторые входы - к первому выходу блока управления, выходы одних из элементовИ соединены с первыми входами регистра слова, выходы других элементов И подключены через элементы НЕ ко вторым входам регистра слова, третьи входы регистра слова соединены с вторым и третьим выходами блока управленря.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

№ 371616, кл. G 11 С 17/00, 1971.

2. Авторское свидетельство СССР № 504247, кл. G 11 С 17/00, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1976 |

|

SU600618A1 |

| Запоминающее устройство с коррекцией ошибок | 1986 |

|

SU1381605A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU864339A1 |

| Запоминающее устройство | 1978 |

|

SU746745A1 |

| Логическое запоминающее устройство | 1981 |

|

SU963099A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU641499A1 |

| Запоминающее устройство | 1975 |

|

SU714496A1 |

| Постоянное запоминающее устройство | 1974 |

|

SU504247A1 |

| Запоминающее устройство матричного типаС САМОКОНТРОлЕМ | 1979 |

|

SU849309A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1026165A1 |

S

Ш

7 I I

И It

Фиг.

Через

элементы ( НЕ

Ф(г. 2

Авторы

Даты

1980-05-05—Публикация

1977-10-24—Подача