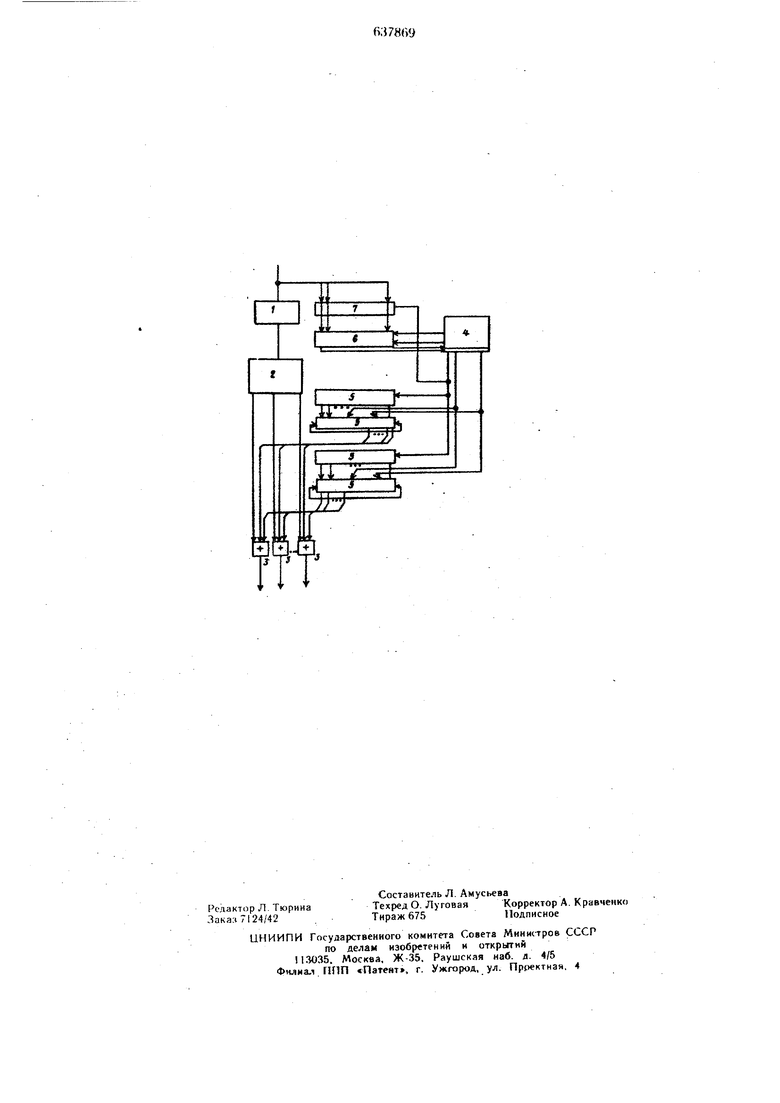

Изобретение относится к вычислительной технике н может быть использовано в цифровых вычислительных машинах и приборах. Известны постоянные запоминающие устройства, одно из которых содержит числовые блоки с большим числом прошитых сердечников, характеризующихся низкой надежностью, большой потребляемой мощностью и большой неравномерностью нагрузки на адресные шины {. Наиболее близким к изобретению техническим решением является постоянное запоминающее устройство, содержашес дешифратор адреса, подключенный к накопителю, выходы которого подключены к одним из входов сумматоров по модулю два, блок местного управления и информационные шины 2|. Это известное устройство характеризуется большим числом элементов связи, используемым при реализации накопителя, большой разрядностью накопителя и низкой надежностью. Целью изобретения является повышение надежности. В предлагаемом устройстве это достигается тем, что f)HO содержит регистры адреса, счетчик импульсов и элементы И, входы KOTopi.ix соединены с информационными шинами, с одними из регистров адреса, подключенных к другим регистрам адреса и с одним из выходов блока местного управления, другие выходы которого через соответствующие регистры адреса подключены к сумматорам по модулю два, а соответствующие входы н выходы блока местного управления через счетчик импульсов соединены с выходами элементов И. На чертеже представлена блок-схема предлагаемого устройства. Оно содержит дешифратор адреса , накопитель 2, выходы которого подключены к одним из входов сумматора 3 по модулю два. Одни из выходов блока 4 местного управления подключены к регистрам 5 адреса, входы блока 4 соединены через счетчик б импульсов с элементами И 7. Обычно накопитель ПЗУ в интегральном исполнении представляет собой матрицу, во всех точках пересечения адресных и разрядных шин которой есть элемент связи, т. е. записаны единицы. В зависимости от конкретной информации, записанной в накопителе, в .местах записи нулей элементы связи уничтожаются. На практике при изготовлении матрицы возникают отказы типа «Генератор П или «Генератор 1. Условный «нулевой отказ имеет место при одимаковых направлениях возникшего дефекта и записываемой информации (т. е. имеется отказ типа «Генератор О и записвтается «О или отказ типа «Генератор 1 и записывается «I) и «единичный отказ при разных направлениях отказа и записываемого типа. «Нулевые отказы в традиционных структурах ПЗУ не оказывают влияния, однако при наличии «единичных отказов матрица бракуется. Для «маскирования влияния «единичных отказов необходимо проинвертировать значение за11исываемых в этих местах разрядов. Так как в предлагаемом устройстве есть возможность инвертировать коды исходной информации по двум диагоналям, то можно маскировать отказы разного типа и тем самым использовать матрицы со значительными отказами. Исходная информация преобразуется сначала с целью сокращения числа элементов связи накопителя 2, потом исходя из возникших отказов использованной матрицы накопителя снова преобразуют информацию с целью «маскирования возникающих отказов. В результате этих обработок информации получают такие коды чисел, на которые возникшие отказы не влияют, и сокраш,ается число единиц. На входы дешифратора 1 поступает код адреса, .по которому производится обращение к накопителю 2; на выходах накопителя 2 получают преобразованный код; числа записаны по этому адресу. В одних из регистров адреса, подключенных к выходам блока местного управления, записаны дополнительные разряды по первым и вторым диагоналям. Считанный код из накопителя 2 поступает на входы сумматоров 3. На входы сумматоров необходимо подавать также значение тех дополнительных разрядов по первым и вторым диагоналям, которые использованы для преобразования кода этого числа. Для этой цели код адреса, по которому производится считывание «з накопителя 2, определяет, какое число сдвигов необходимо произвести в других регистрах адреса 5. Зяпис, информации в регистры Г) осушествлжп-гя по сигналу выдачи кода, по- ступающего из блока 4 местного управления. Одновременно с этим производится запись кода адреса через элементы И 7 в счетчик 6 импульсов. В регистрах адреса выполняются сдвиги соответственно вправо или влево до тех пор, пока код в счетчике 6 не станет равным «О. Последовательные операции сдвига в регистрах 5 и вычитание единицы в счетчике б осуществляются путем подачи сигналов из выходов блока 4 местного управления. После выполнения указанных операций на выходах регистра 5 получают коды дополнительных разрядов по первой и второй диагоналям, которые были использованы при преобразовании кода считанного числа. Эти коды суммируются в сумматоре 3 по модулю два со считанным из накопителя 2 кодом и на выходе получаем код. Форжг/ла изобретения Постоянное запоминающее устройство, содержащее дешифратор адреса, подключенный к накопителю, выходы которого подключены к одним из входов сумматоров по модулю два, блок местного управления и информационные тины, отличающееся тем, что, с целью повышения надежности устройства, оно содержит регистры адреса, счетчик импульсов и элементы И, входы которых соединены с информационными щинами, с одними из регистров адреса, подключенных к другим регистрам адреса, и с одним из выходов блока местного управления, другие .выходы которого через соответствующие регистры адреса подключены к сумматорам по модулю два, а соответствующие входы и выходы блока местного управления через счетчик импульсов соединены с выходами элементов И. Источники информации, принятые во внимание ripH экспертизе: 1.Авторское свидетельство СССР № 371616, кл. G 1 С 17/00, 1970. 2.Авторское свидетельство СССР № 376808, кл. G 11 С 17/00. 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU627543A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU911627A2 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1061176A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

Авторы

Даты

1978-12-15—Публикация

1977-02-25—Подача