1

Изобретение относится к области вычислительной техники, в частности, к запоминающим устройствам электронно-вычислительных машин (ЭВМ).

Одно из известных устройств содержит дешифратор адреса, выходы которого соединены со входами числового блока, сумматоры по модулю два по числу выходов числового блока и шифратор, первую и вторую группы элементов И, сдвиговый регистр и дополнительный сумматор по модулю два, при этом выходы числового блока подключены к первым входам соответствуюш,их сумматоров по .модулю два, ко вторым входам которых подсоединены выходы соответствующих элементов И первой группы,- первые входы которых соединены с соответствующими входами шифратора, а вторые подключены к выходу дополнительного сумматора по модулю два, входы которого соединены с выходами элементов И второй группы, первые входы которых подключены к соответствующим входам дешифратора адреса, а вторые - к соответствующим выходам шифратора, входы которого соединены с выходами регистра сдвига 1.

Известное устройство позволяет сократить число элементов связи, что повыщает надежность его, но данное устройство не производит коррекции считанной информации.

Наиболее боТизким техническим решением к данному изобретению является постоянное запоминающее устройство, содержащее узел постоянной памяти, узел сменной информации, выходной блок, схемы выборки адреса измененной информации, схему сборки, схему блокировки н схемы считывания измененной информации, в котором адресные шины подключены к первым входам схемы выборки адреса измененной информации, вторые входы которых подключены к элементам, хранящим адрес измененной информации, а их выходы подключены к схеме сборки и первым входам схем считывания измененной информации, вторые входы которых подключены

к элементам, хранящим измененную информацию, выход схемы сборки подключен к управляющему входу схемы блокировки, вторые входгы которой подключены к. выходным шинам узла постоянной памяти, а

,(0 ::;;;nCii прсдзйрк т и но г;5пябз :- г яс г;;, ЭГ;:1 ос пи::сти.ляется ис LjjtAViOm.eiviv алго:.- i j .

.А ;-1/1/ О ЧЧСЯ М-П.-О -V/IHt:- КО О .

CV;);K ислодной кигЬормяцни. :(; чкс.П

у/г . П ).)}-, O.D :all - рЭЗрЯД ПОСТ:., ЧИСЛа), ГО КОЛ

;:ГрОК;-; - 1; РрТИруеТ:.-Я ; :j цОПОЛ:-;ктеЛЬ5|г 1;

когля :;:с. е/и-:нип i:-ei ;..:Jjti O.;;.i, го ко,,:

ПОКИ НС ЯВРОТИОУ-ТГР fi и ,О ОJiiHРЛЬНО

рааояде зяписываетси IL преобрузоваНИК ИСХОДНО ИНфорМаДИ - -:О ;) ПСОИЗвСДЯгсн доиолните. оиерпции над кодйKi к i;o .). б нам. Если Mucjio сдкниц ;: код;Р |:ИГО , /;:iJ - 4;-;rjir

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1976 |

|

SU611253A1 |

| Устройство для накопления чисел с плавающей запятой | 1990 |

|

SU1829030A1 |

| Запоминающее устройство | 1978 |

|

SU769624A1 |

| Постоянное запоминающее устройство | 1976 |

|

SU641499A1 |

| Запоминающее устройство | 1978 |

|

SU926712A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Запоминающее устройство | 1981 |

|

SU1010654A1 |

| Запоминающее устройство | 1984 |

|

SU1251175A1 |

| Запоминающее устройство | 1978 |

|

SU769622A1 |

ПММ

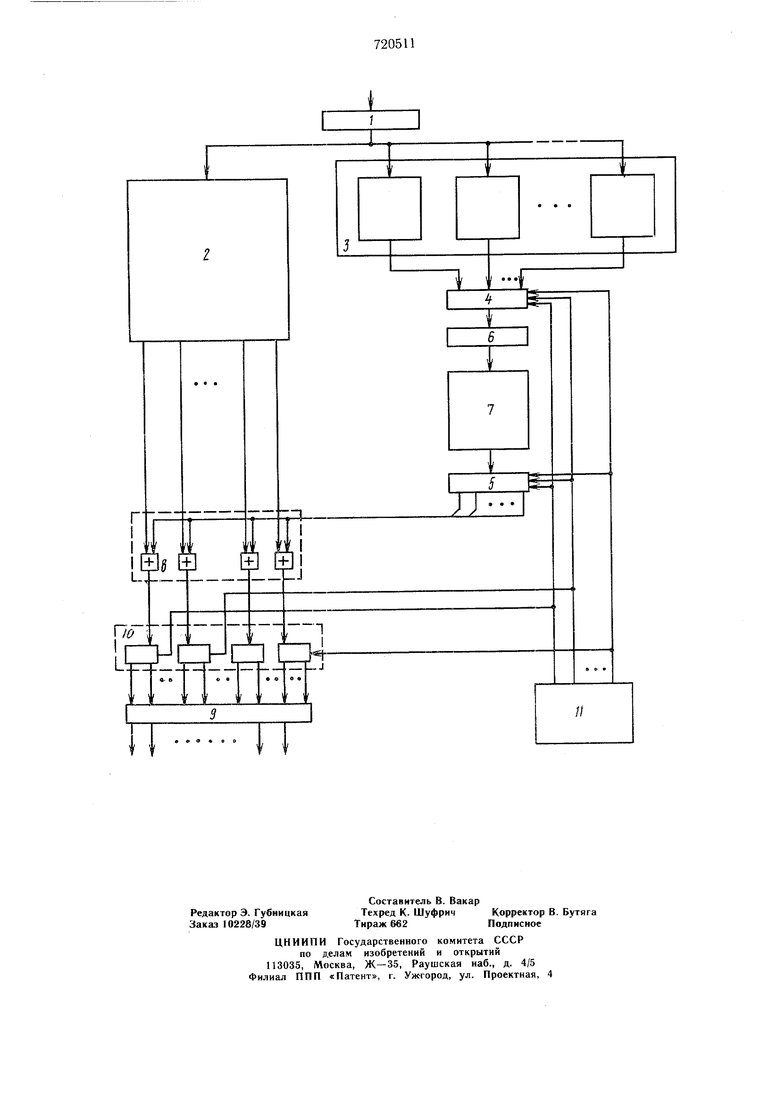

ты и 10, которые соответствуют только разрядам первой области. Восста говленные разряды, соответствующие первой об,ласти, записываются в регистр числа 9. ПССЛР этого возбуждается следующая шина блок-: .;eciного управления П. Выходы дополнительного накопителя 3 при помощи первого коммутатора 4 по сигналу с блока местного управления 11 подключаются к дополнительному дешифратору 6, возбуждается одна из его шин и на выходах дополнительного накопителя 7 получает корректирующий код, применяемый во второй области. Второй коммутатор 5 подключает выходы дополнительного накопителя 7 к соответствующи.м сумматорам по модулю два 8, сигнал блока местного управления 1 разрепзает

И ). ООТГ; ТСТ вУЮШИл (

.. peiHCTp числа 9. Пина б-лока местноy;. П по::ледоватгЛьго оо:и)у;:-сдаетСЯ до i:0p, пока не ПОДКЛН)ЧЯ п. ;; нг-:;

;;0: :,,1ьного нкуо .;::r:rv 3 v: КО;гут ру Н;; (. элгл-ут;.; И iO; которые не соответствую одной о5л;1сти, И1нал, разрешающий зйякгь якфop лu:-il в рстяшр числа 9, подается ипи счптыв ;5ии И формациа с Hai-Ajji u- j: 2.

Обгбщая. можно сделать гле;пк:ичш PivЁод. Снзчалй исходная инфоря;гуия гфеобразуется по строкам и сто.лбц.м в накогИ;еле с це.мью сокрапдения числа ед;:киц. 1отол; в зав ;симости от отказов в накопителе гфСмтзБоди 1тя преобразование с цсльс «;лйск:;;хя;аь;: х- тнх отказов, и если -л.гас.ч.фование всх отказог. невозможно :Ч:пм7Л:а 1л: коис1алле), используется способ с более BfcicoKOJi корректирующей способностью для исправления кокцентрированнь х отказов Предлагаемое устройство имеет ряд гфеичугцеств. а менпо: при Meiibruiix аппараГ) запфа гах уменьшается емкость . позьи 1ае ся надежность н тлхно,:огччйлсть. .naeTCH потребляемая siouiHfu-: -. .Изможлс чс1;о и зочать матригил с ,;еф-л;г:1ми ц;;дл едипячлой и «нулевсн - краткости-, которые для ;с::ол зован : В лоототи ге неппчгоднь. . ip-.yj araeMa5i структура постоянного занпM : a Oiuero устоойства позволяет ;: случа если накопитель 2 без дефектоБ, повысить

его информационную емкость. Это достигается путем считывания из накопителя одною числа и путем изменения отдельных разрядов посредством подключения отдельных (в частг ости всех) дополнительных накопителей получить коды, различающиеся только в части разрядов. Это очень удобно при реализации функций, у которых по «базовы.м значениям можно легко сформировать смежные значения функции.

Формула изобретения

Постоянное запоминающее устройство с коррекцией считываемой информации, содержащее накопитйть, входы которого соучл;:-f - i:CT ysoMj.HM; ыходамм де ;Ф;патор : лйпеса, а выходы -- с первыми сЛ ;)л1; сосгьетотвующих сумматоров по лллул); .;-. )лы ;;отопыл Етодклкчень :. . -Л-. , солтвлтствукщих лемея::- -Л л ---н ментпв PI соединены со О,.-aii-H рс чстпа числа, и блок местного лг-йял -нлз г м :::ющееся тем. что, с целью :л :-;Л е iH ллдежностк. оно содержит до;.1Л л;;т.ль;1ы накопители, два коммутатора, ;.лл-С:Л ителг,лч;й дешифратор адреса, при ЭЛЛ-: вхо,л слЮго дополнительного нако:;1 л лл сое: с cooтвeтcтвyющi jи выхоллгЛ: делифпатора адреса, а выходы - . yiiUNiH входа Mil первого коммутатора, й:-л-: iCnporc коммугатора подключены

.; . ЛЛ Bti4;;;) гО;Д;-М ВХОДаМ ДО| ОЛННТеЛЬНОГО

:;- л фрлтор;: адрога, входы другого допол;:;г ельног( накопителя соединены с выхода л лопол«и ельвого дешифратора адреса, 8 выходы - с одними входами второго ком,; латора. 5;ылоды которого подключены ко ч-опыч; к:-- ил с ,л;маторов по модулю два,

Л:. :Л. ,. .,О ЗТсучогО КОГ;;1 Ла1О Л : --Л: ; -ллул: . бЛ(К;; . I.:. л клгки ииформацни, : : .- , Л : .Л1г,;ймие лрн экспертизе Л;л:л: ; ллллглгльстзо ПО лпнвке /:-:,-Ji-y лг л;. G ; с 7/00, 1976.

-л-ч - . -;еголь;л- 50 СССР У:.; ;(.ip::, ,:,; vs Р С /00, iQilft (прототип).

Авторы

Даты

1980-03-05—Публикация

1977-04-15—Подача