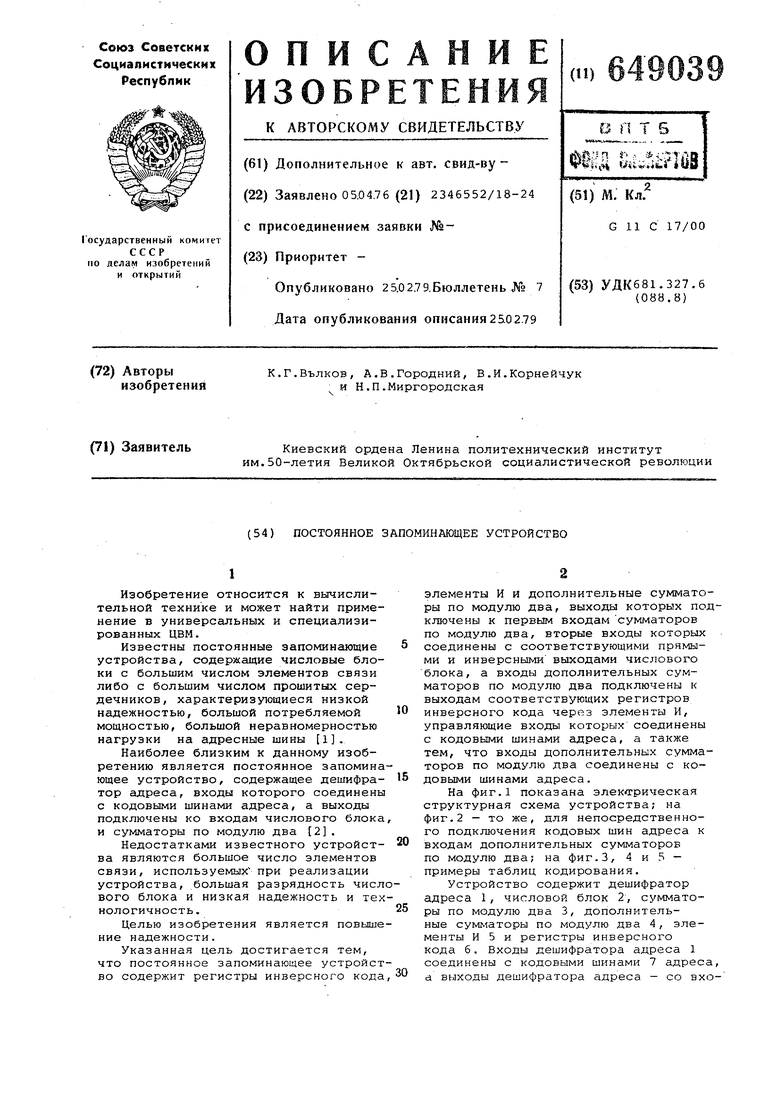

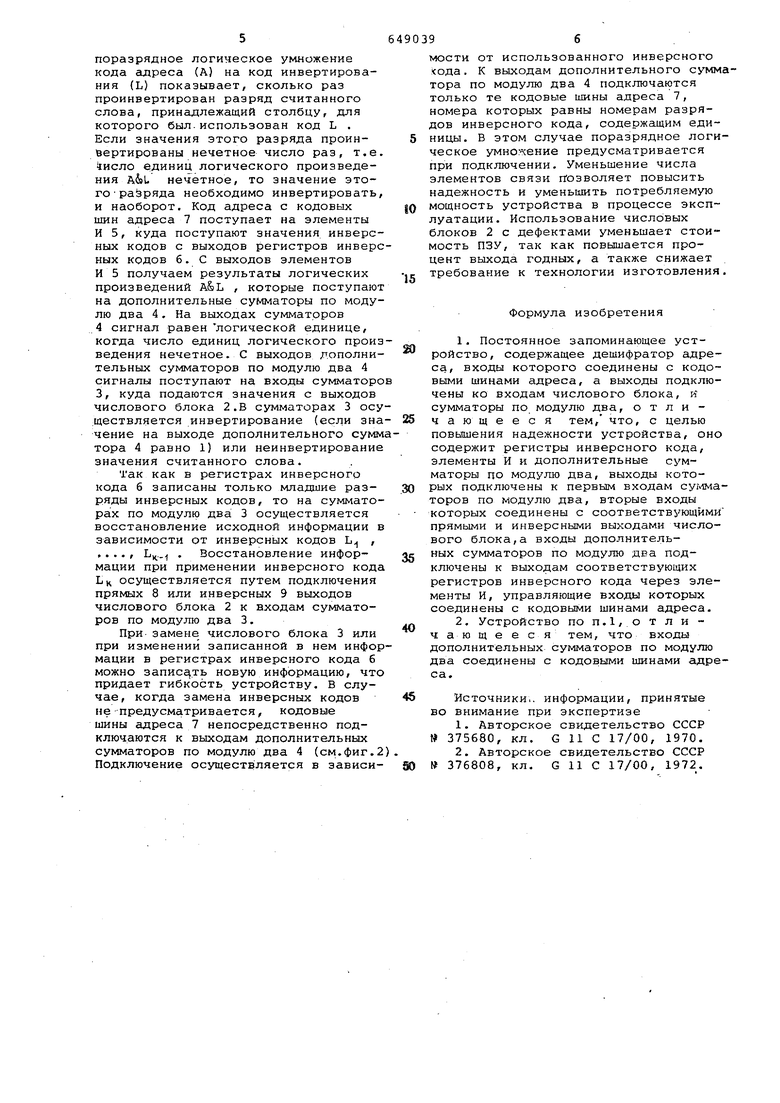

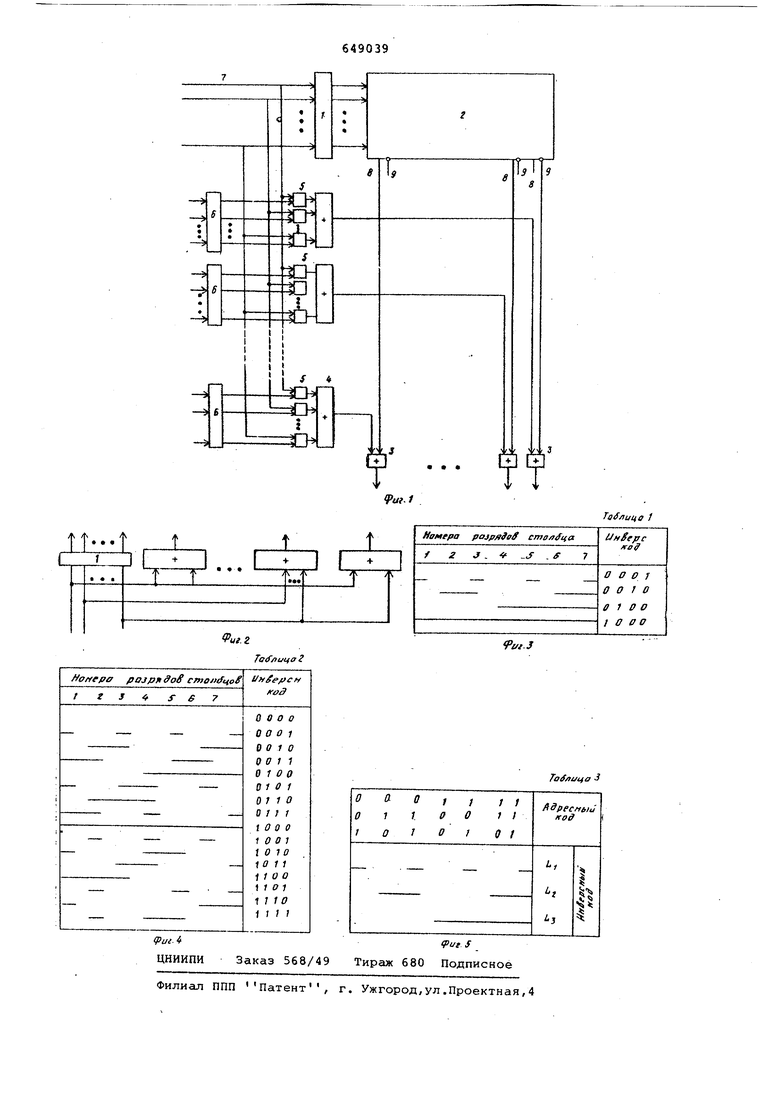

(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО дами числового блока 2, Выход i-того дополнительного сумматора по модулю два 4 подключен к первому входу 1-того сумматора по модулю два 3, ко второму входу которого подсоедине 1-тый прямой 8 или инверсный 9 выход числового блока 2.Входы дополнительных сумматоров по модулю два 4 подключены к выходам соответствующих регистров инверсного кода 6 через элементы И 5, управляющие входы которых соединены с кодовыми шинами адреса 7. Разрядность регистров инверсного кода б и число входов дополнительных сумматоров по модулю два 4 равны числу кодовых шин адреса Устройство работает следующим образом. Информация в числовом блоке 2 .записывается в двоичном коде, при этом в местах записи единиц устанавливаются элементы связи. С целью уменьшения числа элементов связи исходная информация предварительно преобразуется по следующему алгоритму. При заданной разрядности столбцов (А) записываемой информации определяется разрядность (К) инверсных кодов (К log (А+1). Выбираются основные инверсные коды L ,L2 ...., L|, значения, которых соответст венно равны 2°, , . Каждому инверсному коду соответствуют разряды столбца, которые инвертируют ся при использовании этого кода. Выбор инвертируемых разрядов кода стол ца осуществляется как и при коде Хэм минга. Инверсный код L -2 указывае что все нечетные разряды кода столбц инвертируются. Инверсный код L - 2 указывает, что инвертируются все ра ряды, двоичные номера которых содер жат во втором разряде единицу. Анал гичным образом определяются инверти руемые разряды для остальных инверс кодов,за исключением кода LK 2, п котором инвертируются все разряды столбца. На табл.1 (см.фиг.3) показ ны основные инверсные коды .и со ветствующие им разряды при А 7, к 4. На базе основных инверсных кодов формируются остальные инверсные коды, а также определяются инве тируемые разряды столбца (см.фиг.4) Инверсный код , полученный в результате суммирования кодов L,иЬ.), указывает, что инвертируются сначала те разряды кода столбца, которые соответствуют коду инвертирования L ,. а потом все разряды, соответствующие коду LJ . При преобразовании исходной инфо мации, для каждого кода столбца выбирается инверсный код таким образо чтобы после инвертирования разрядов соответствующих данному инвepcнo./ коду, число единиц в коде столбца было минимальным. Например,если код толбца равен 1101011, то из табл.2 (см.фиг.4) выбирается инверсный од 0111, который указывает, что нвертируются разряды с номерами , 2, 4 и, 7. После инвертирования олучаем код 00000010. После преобраования исходной информации произвоится запись в числовом блоке 2, а начения инверсных кодов, за исключеием старших разрядов, записываются регистрах инверсных кодов б. На практике при изготовлении матицы числового блока 2 возникают ефекты, которые могут совпадать с записываемой информацией (нулевой отказ) или иметь разные направления с записываемым битом (единичный . отказ) . Нулевые отказы не оказывают влияния, но для маскирования единичных отказов необходимо проинвертировать значения соответствующих разрядов записываемой информации. Например, если необходимо .записать столбец с кодом 1110101, и в месте записи первого и второго разрядов в матрице числового блока 2 есть соответственно единичный и нулевой отказы, то необходимо выбрать такой инверсный код, при котором инвертируется 1-ый разряд и не инвертируется 2-ой разряд. Таким инверсным кодом является код LO(OOOI), который позволяет маскировать возникшие отказы и при этом сокращает максимальное число единиц. Следовательно, преобразование исходной информации осуществляется с целью маскирования отказавших разрядов и уменьшения числа элементов связи. В зависимости от кода адреса, поступающего на кодовые шины адреса 7, возбуждается соответствующий выход дешифратора адреса 1, и из числового блока 2 считывается содержимое ячейки, номер которого равен коду адреса. На выходах числового блока 2 получается преобразованный код числа и для восстановления исходного кода необходимо проинвертировать соответствующие разряды. Код адреса (номер разряда столбца) определяют, инвертируется или не инвертируется значение считанных разрядав при соответствующем инверсном коде. На табл-.З (см.фиг,5) показаны коды адресов при и инвертируемые разряды соответствующих основных инверсных кодов. Из таблицы ; видно, что при считывании информации, записанной в ячейках.с нечетными номерами (код адреса содержит в младшем разряде единицу), значения разрядов столбцов, для которых применен инверсный код L, необходимо инвертировать, так как они были инвертированы при преобразовании исходной информации. Рассуждая аналогичным образом приходим к выводу, что

поразрядное логическое умножение кода гщреса (А) на код инвертирования (L) показывает, сколько раз проинвертирован разряд считанного слова, принадлежащий столбцу, для которого был.использован код L . Если значения этого разряда проинвертированы нечетное число раз, т.е. 1МСЛО единиц логического произведения A&U нечетное, то значение этого разряда необходимо инвертировать, и наоборот. Код адреса с кодовых шин адреса 7 поступает на элементы И 5, куда поступают значения инверсных кодов с выходов регистров инверсных кодов 6. С выходов элементов И 5 получаем результаты логических произведений A&L. , которые поступают на дополнительные сумматоры по модулю два 4. На выходах сумматоров 4 сигнал равен логической единице, когда число единиц логического произ ведения нечетное. С выходов дополнительных сумматоров по модулю два 4 сигналы поступают на входы сумматоро 3, куда подаются значения с выходов числового блока 2.В сумматорах 3 осуществляется инвертирование (если зна чение на выходе дополнительного суммтора 4 равно 1) или неинвертирование значения считанного слова.

Так как в регистрах инверсного кода б записаны только младшие разряды инверсных кодов, то на сумматора-х по модулю два 3 осуществляется восстановление исходной информации в зависимости от инверсных кодов L , ,. .. , L., , Восстановление информации при применении инверсного кода LH осуществляется путем подключения прямых 8 или инверсных 9 выходов числового блока 2 к входам сумматоров по модулю два 3.

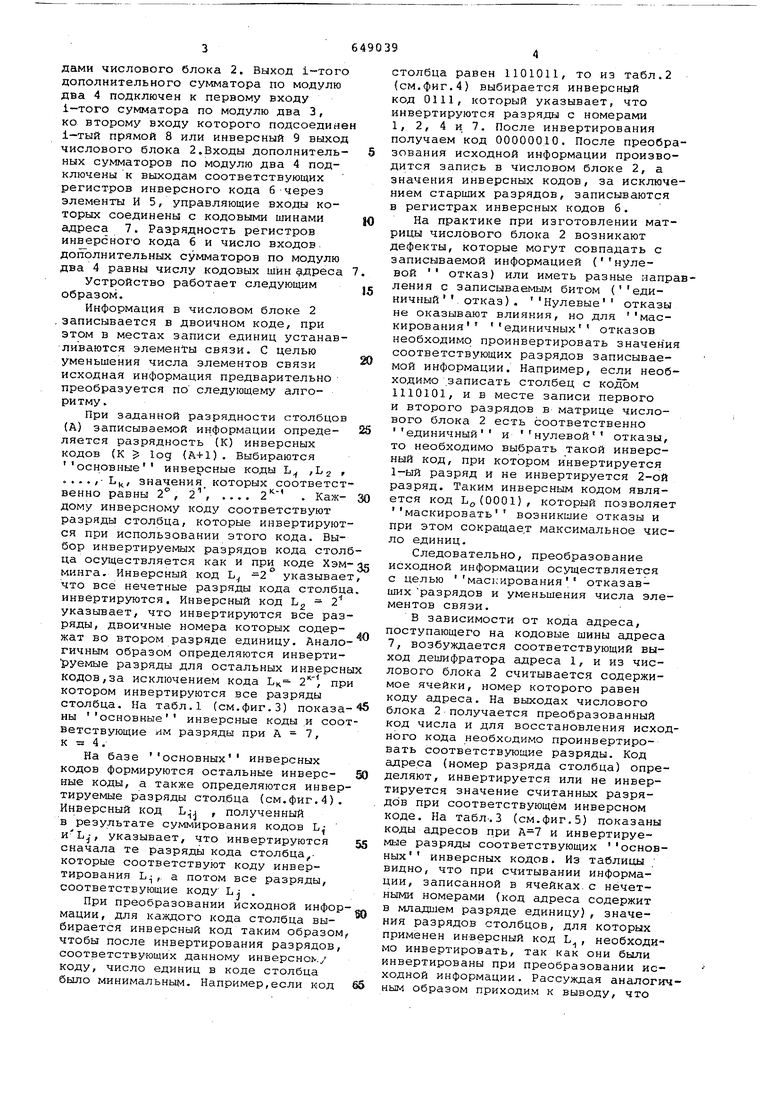

При замене числового блока 3 или при изменении записанной в нем информации в регистрах инверсного кода 6 можно записать новую информацию, что придает гибкость устройству. В случае, когда замена инверсных кодов не предусматривается, кодовые шины адреса 7 непосредственно подключаются к выходам дополнительных сумматоров по модулю два 4 (см.фиг.2 Подключение осуществляется в зависимости от использованного инверсного ода. К выходам дополнительного сумматора по модулю два 4 подключаются только те кодовые шины адреса 7, номера которых равны номерам разрядов инверсного кода, содержащим единицы. В этом случае поразрядное логическое умножение предусматривается при подключении. Уменьшение числа элементов связи позволяет повысить надежность и уменьшить потребляемую мощность устройства в процессе эксплуатации. Использование числовых блоков 2 с дефектами уменьшает стоимость ПЗУ, так как повышается процент выхода годных, а также снижает требование к технологии изготовления.

Формула изобретения

1.Постоянное запоминающее устройство, содержащее дешифратор адреса, входы которого соединены с кодовыми шинами адреса, а выходы подключены ко входам числового блока, и сумматоры по модулю два, отличающееся тем, что, с целью повышения надежности устройства, оно содержит регистры инверсного кода, элементы И и дополнительные сумматоры по модулю два, выходы которых подключены к первым входам cyi.iMaторов по модулю два, вторые входы которых соединены с соответствующими прямьами и инверсными выходами числового блока,а входы дополнительных сумматоров по модулю два подключены к выходам соответствующих регистров инверсного кода через элементы И, управляющие входы которых соединены с кодовыми шинами адреса.

2.Устройство по п.1,о т л и ч аю щ е е ся тем, что входы дополнительных сумматоров по модулю два соединены с кодовыми шинами адреса.

Источники,, информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 375680, кл. G 11 С 17/00, 1970.

2.Авторское свидетельство СССР 376808, кл. G 11 С 17/00, 1972.

1 I

Та f ли 14 о I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для коррекции отказов в полупроводниковой памяти | 1982 |

|

SU1049981A1 |

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| Запоминающее устройство с исправлением дефектов и ошибок | 1987 |

|

SU1536445A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU627543A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Постоянное запоминающее устройсство | 1977 |

|

SU637869A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1211811A1 |

Авторы

Даты

1979-02-25—Публикация

1976-04-05—Подача