Изобретение относится к вычислительной технике, в частности к микроэлектронным устройствам памяти на полупроводниковых приборах.

Целью изобретения является повышение быстродействия запоминающего устройства (ЗУ).

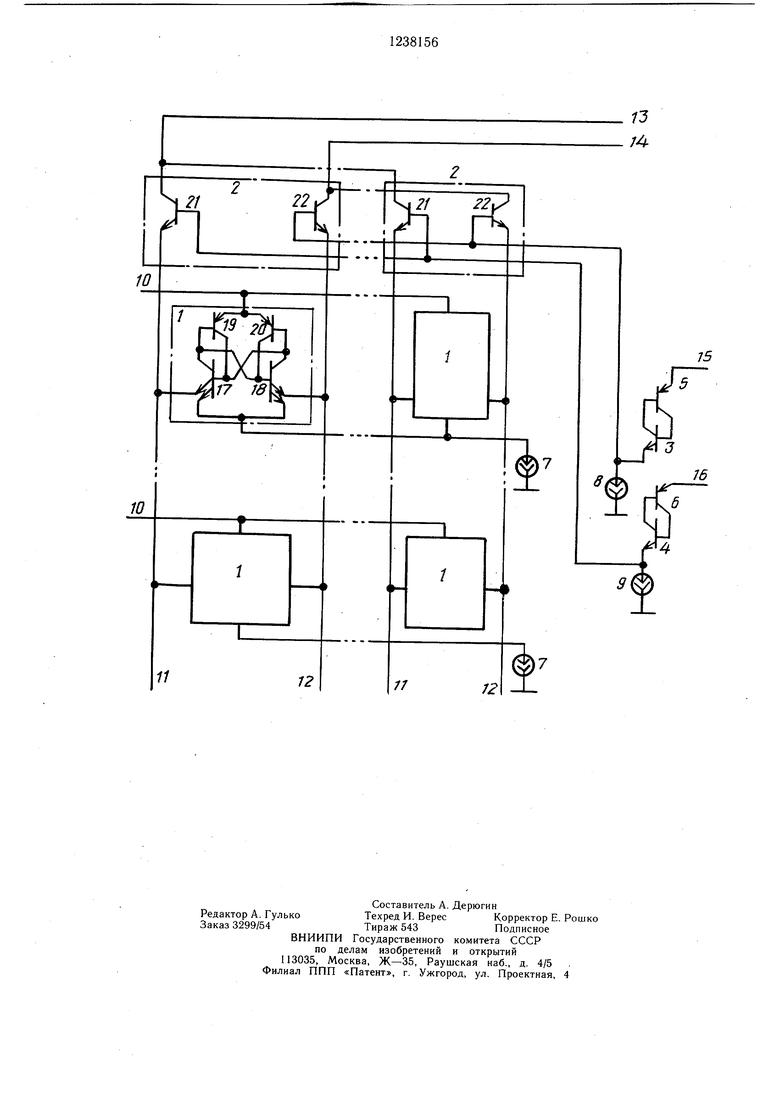

На чертеже представлена электрическая схема предлагаемого устройства.

Запоминающее устройство содержит матрицу элементов памяти 1, группу разрядных усилителей 2, первый и второй управляющие элементы 3 и 4, выполненные на транзисторах «-типа, первый и второй компенсирующие элементы 5 и 6, выполненные на транзисторах р-типа, группу источников тока 7, первый 8 и второй 9 источники тока. На чертеже показана также щина выработки 10, первая 11 и вторая 12 разрядные шины, первый 13 и второй 14 выходы считывания устройства, первый 15 и второй 16 управляющие входы устройства. Элемент памяти 1 состоит из первого 17 и второго 18 двухэмиттерных транзисторов п-типа и первого 19 и второго 20 транзисторов р-типа. Разрядный усилитель 2 состоит из первого 21 и второго 22 транзисторов п-типа.

Устройство работает следующим образом.

При считывании информации на одну из щин 10 поступает импульс напряжения амплитудой t/i, а на управляющих входах 15 и 16 устанавливаются равные потенциал t/2. При этом на базах транзисторов 21 и 22 устанавливаются равные потенциалы i/з- Если, например, в выбираемом элементе памяти транзистор 18 включен, а транзистор 17 выключен, то потенциал базы транзистора 18 (/4 выше, а потенциал базы транзистора 17 ниже потенциала Оз. При этом ток, задаваемый в разрядную шину 12, поступает в транзистор 18, а ток, задаваемый в разрядную щину 11, поступает в транзистор 21 и на выход считывания 13. Разность токов, протекающих на выходах считывания 13 и 14, характеризует сигнал считываемой информации. Транзисторы 5 и 6 и транзистор 20 (или 19), а также транзистор 3 и 4 и транзистор 18 (или 17) работают в идентичных режимах насыщения, что позволяет сократить величину разности потенциалов f/4 и Us, характеризующую быстродействие устройства. При записи устройство работает аналогич5

ным для известных ЗУ образом. Например, потенциал на управляющем входе 16 и соответственно на базе транзистора 21 понижается, а на входе 15 и соответственно на базе транзистора 22 повышается. При этом транзистор 17 включается, а транзистор 18 выключается.

Формула изобретения

Запоминающее устройство, содержащее

0 матрицу элементов памяти, каждый из которых состоит из первого и второго двухэмит- терных транзисторов п-типа, базы и коллекторы которых перекрестно соединены, и первого и второго транзисторов р-типа, базы и коллекторы которых соединены с коллекторами и базами соответствующих двухэмиттерных транзисторов л-типа, первые эмиттеры которых в каждом столбце матрицы подключены соответственно к первой и второй разрядным шинам, эмиттеры транзисторов

0 р-типа в каждой строке матрицы подключены к соответствующей шине выборки, группу источников тока, первый вывод каждого из которых соединен с вторь1ми эмиттерами двухэмиттерных транзисторов «-типа элементов памяти соответствующей строки матри5 цы, а второй вывод подключен к шине нулевого потенциала, разрядные усилители, каждый из которых состоит из первого и второго транзисторов п-типа, эмиттеры которых соединены с разрядными шинами соответствующего столбца матрицы, а коллекторы являются первым и вторым выходами считывания устройства, первый и второй источники тока и первой и второй управляющие элементы, каждый из которых выполнен на транзисторе л-типа, эмиттер которого соединен с базами соответствующих транзисторов п-типа разрядных усилителей и с первым выводом соответствующего источника тока, второй вывод которого соединен с шиной нулевого потенциала, отличающееся тем, что, с целью повышения быстродействия

0 устройства, оно содержит первый и второй компенсирующие элементы, выполненные на транзисторах р-типа, базы и коллекторы которых соединены с коллекторами и базами соответствую ицих транзисторов п-типа управляющих элементов, а эмиттеры являются пер5 вым и вторым управляющими входами устройства.

0

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1973 |

|

SU444244A1 |

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| Ячейка памяти | 1974 |

|

SU491998A1 |

| Ячейка памяти | 1974 |

|

SU536527A1 |

| Запоминающее устройство | 1976 |

|

SU613405A1 |

| Запоминающее устройство | 1985 |

|

SU1310896A1 |

| Запоминающее устройство | 1985 |

|

SU1256097A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1689991A1 |

| Накопитель для запоминающего устройства | 1983 |

|

SU1137537A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

Изобретение относится к вычислительной технике, в частности к микроэлектронным устройствам памяти на полупроводниковых приборах. Целью изобретения является повышение быстродействия запоминающего устройства (ЗУ). Элементы памяти ЗУ выполнены на двух двухэмиттерных транзисторах л-типа и двух транзисторах р-типа. Сигналы, управляющие работой ЗУ в режимах записи и считывания, проходят через управляющие элементы, каждый из которых состоит из транзистора га-типа и транзистора р-типа, включенных аналогично соответствующим транзисторам элементов памяти. Благодаря этому транзисторы управляющих элементов и элементов памяти работают в идентичных режимах, что позволяет снизить разность потенциалов между узловыми точками элемента памяти, характеризующую быстродействие ЗУ. 1 ил. (Л Ю оо ас ел о:

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО |

Авторы

Даты

1986-06-15—Публикация

1983-10-04—Подача