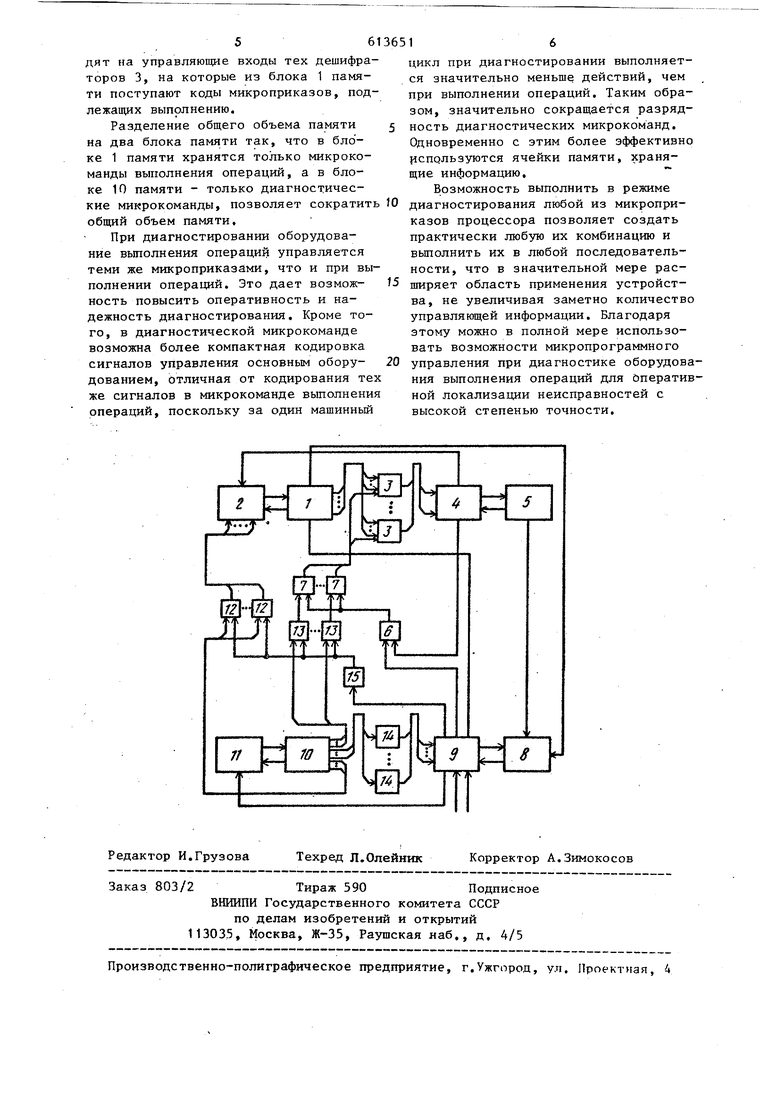

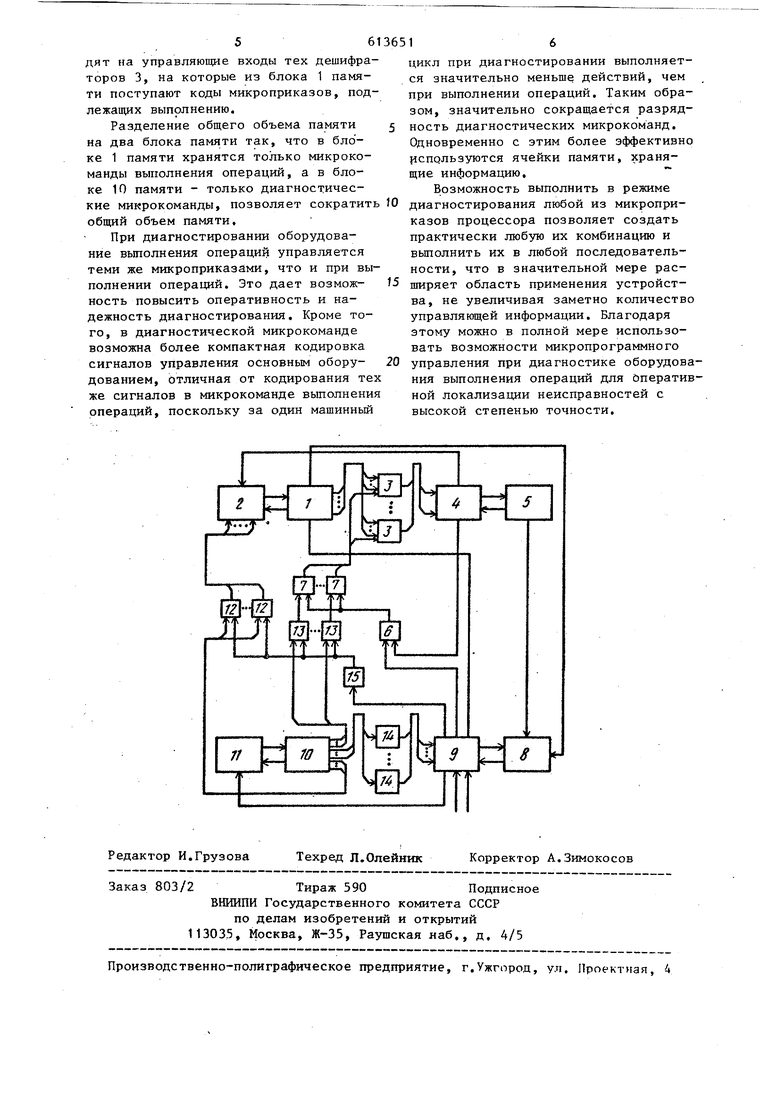

Изобретение относится к запоминающим устройствам и может использовать ся в специализированных и универсальных вычислительных машинах и средствах автоматики. Известно запоминающее устройство содержащее блок памяти микрокоманд, блок управления, арифметико-логический блок, оперативный блок памяти, блок сопряжения, блок контроля, блок диагностики. Это устройство позволяет проводить диагностику оборудования выполнения операций, однако имеет некоторые недостатки. Диагностические тесты хранятся на внешнем носителе (магнитной ленте) и для выполнения загружаются в начальную область опе ративной памяти, поэтому для диагностики процессора и каналов необходима гарантированная работоспособ ность одного из селекторных каналов и начальной области оперативной памяти, что исключает возможность, автономной диагностики. Диагностические микропрограммы выполнения те тов хранятся в блоке памяти микропрограмм вместе с микропрограммами выполнения операций, это обусловливает одинаковую разрядность тех и других микрокоманд, в результате часть объема памяти остается неиспользованной. Наиболее близким техническим решением к изобретению является запоми нающее устройство, содержащее блоки памяти, подключенные соответственно к блокам управления, блок диагности ки, первый и второй выходы которого соединены соответственно с входами первого блока памя-ги и второго блок управления, блок контроля, подключенный к первому блоку памяти, логическому блоку диагностики, дешифраторы, одни входы которых соединены с выходами первого блока памяти, а выходы - с входами логического блока Известное запоминающее устройство имеет следующие особенности. В первом блоке памяти хранятся микропрограммы выполнения операций и диагнос тические микропрограммы, во втором блоке памяти - только диагностические микропрограммы. Микрокоманды 060 их блоков памяти выбираются на один и тот же регистр микрокоманд; оба блока памяти имеют общий адресный регистр, управляемый триггером первичной выборки, у микрокоманд обоих типов одинаковая разрядность. Таким образом, второй блок памяти является продолжением первого, хотя физически они разделены. Объем памяти микрокоманд определяется количеством ячеек памяти и зависит от длины (разрядности) слова и от количества слов. К недостаткам такого устройства, вызванным его особенностями, следует отнести значительный объем памяти микрокоманд и низкую эффективную емкость, а также большие затраты оборудования вследствие двойного управления. Цель изобретения - упрощение запоминающего устройства и увеличение его эффективной емкости. Это достигается тем, что запоминающее устройство содержит элементы ИЛИ-НЕ, две группы элементов И-НЕ, триггеры и дополнительные дешифраторы, входы которых подключены к одним из выходов второго блока памяти, а выходы - к входам блока диагностики. Другие выходы второго блока памяти соединены с первыми входами элементов И-НЕ, вторые входы которых подключены к выходу первого триггера, выходы элементов И-НЕ первой группы с входами первого блока управления. Выходы элементов И-НЕ второй группы подключены к первым входам элементов ИЛИ-НЕ, вторые входы которых соединены с выходом второго триггера, а выходы - с другими входами дешифраторов. Входы триггеров подключены соответственно к третьему и четвертым выходам блока диагностики и выходу третьего блока управления. . На чертеже представлена структурная схема запоминающего устройства. Запоминающее устройство содержит блок 1 памяти, блок 2 управления, дешифраторы 3, блок 4 управления, логический блок 5, триггер 6, элементы ИЛИ-НЕ 7, блок 8 контроля, блок 9 диагностики, блок 10 памяти, блок 11 управления, первую группу элементов И-НЕ 12, вторую группу элементов И-НЕ 13, дополнительные дешифраторы 14, триггер 15. Входы дополнительных дешифраторов 14 подключены к одним из выходов второго блока 10 памяти, а выходы к входам блока 9 диагностики. Другие выходы блока 10 соединены с первыми входами элементов И-НЕ 12 и 13, вто рые входы которых подключены к выхо ду первого триггера 15. Выходы элементов И-НЕ 12 подсоединены к входа первого блока 2 управления, выходы элементов И-НЕ 13 - к первым входам элементов ИЛИ-НЕ 7, вторые входы ко торых связаны с выходом второго три гера 6, а выходы - с другими входами дешифраторов 3, Входы триггеров 15 и 6 подключены соответственно к выходам блока 9 диагностики и выходу третьего блока 4 управления. Устройство работает следующим образом, Выполнение операций процессором производится путем выборки микрокоманд (управляющих слоев) выполнения операций из первого блока 1 памяти, дешифрации групп разрядов дешифраторами 3 и вьщачи микроприказов (управляющих сигналов) в третий блок 4 управления. Последний управляет вс ми преобразованиями информации в логическом блоке 5, Выборка микрокоманд осуществляется по адресу, код которого формируется в первом блоке 2 управления. Код адреса следующей микрокоманды и коды адресов безуслов ных переходов передаются в блок 2 управления из блока 1 памяти, призна ки условных переходов - из блока 4 управления. Блок 1 памяти предназначен только для хранения 5шравляющих слоев выпЬлнения операций. Активизация всех дешифраторов 3 производится триггером 6 через элементы ИЛИ-НЕ 7, Триггер 6 взводится из блока 4 управления при выполнении операций. Функционирование логического блока 5 и правильность выбираемых из блока 1 памяти управляющих слов проверяется блоком 8 контроля, который в случае ошибки отработки, пересьтки или хранения информации инициирует работу блока 9 диагностики. При наличии ошибки блок 8 контроля включает блок 9 диагностики, ко торый останавливает выполнение операций путем прекращения выборки управлякнцих слов из блока 1 памяти и сбрасывает триггер 6, снимая тем самым активизацию дешифраторов 3. Затем блок 9 диагностики начинает вы борку управляющих слов из блока 10 памяти, который предназначен для хранения только диагностических управняющих слов. Начальные адреса микрокоманд диагностических процедур и признаки условных и безусловных переходов поступают из блока 9 диагностики и блока 10 памяти во второй блок 11 управления, который формирует коды адресов управляющих слов. Для процедур диагностики необходима работа как диагностического оборудования, так и оборудования выполнения операций под управлением диагностики, Для выполнения первой задачи группа разрядов выбранного из блока 10 памяти управляющего слова поступает на дешифраторы 14, с выхода ко.торьЬс диагностические управляющие сигналы проходят в блок 9 диагностики. Для выполнения второй задачи в устройстве управление работой оборудования выполнения операций осуществляется теми же самыми управляющими сигналами, которьми это оборудование управляется при выполнении операций. Когда в диагностическом режиме возникает необходимость выполнить те или иные микроприказы процессора, блок 9 диагностики вызывает из блока 1 памяти любую из микрокоманд, содержащую эти микроприказы. Все разряды этой микрокоманды поступают на дешифраторы 3, но из них активизируются только те, на которые подаются коды микроприказов, подлежащих выполнению. Для реализации указанных действий блок 9 диагностики взводит триггер 15 и другая группа разрядов микрокоманды из блока 10 памяти, в которой содержится код адреса необходимой микрокоманды вьтолнения операций, через элементы И-НЕ 12 поступает на адресный вход блока 2 управления , Одновременно из блока диагностики подается разрешающий сигнал в блок 1 памяти и из него по заданному адресу выбирается необходимая микрокоманда. Третья группа разрядов этой же диагностической микрокоманды из блока 10 памяти поступает на первые входы элементов И-НЕ 13, Эта группа разрядов содержит признаки тех микроприказов микрокоманды блока 1 памяти, которые необходимо вьтолнить в данный момент. В соответствии с этими признаками открываются те или иные элементы И-НЕ 13, Сигналы с выхода поседних через элементы ШМ-НЕ 7 прохо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выбора информации из блока памяти | 1976 |

|

SU615538A1 |

| Микропроцессор | 1977 |

|

SU943734A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1991 |

|

RU2042189C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042190C1 |

| УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1991 |

|

RU2042188C1 |

| Устройство для управления,контроля и диагностирования | 1985 |

|

SU1297063A1 |

| Запоминающее устройство | 1976 |

|

SU877613A1 |

| Процессор программируемого контроллера | 1988 |

|

SU1550515A2 |

| Устройство микропрограммного управления | 1974 |

|

SU528568A1 |

| Программируемый контроллер | 1988 |

|

SU1642446A1 |

ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки памяти, подключенные соответственно к блокам управления, блок диагностики, первый и второй выходы которого соединены соответственно с входами первого блока памяти и второго блока управления, блок контроля, подключенньш к первому блоку памяти, логическому блоку и блоку диагностики, дешифраторы, одни входы которых соединены с выходами первого блока памяти, а выходы - с входами дополнительного блока управления, подключенного к первому блоку управления и логическому блоку, отличающееся тем, что, с целью упрощения и повышения эффективности емкости устройства, оно содержит элементы ИЛИ-НЕ, две группы элементов И-НЕ, триггеры и дополнительные дешифраторы, входы которых подключены к одним из выходов второго блока памяти, а выходы — к входам блока диагностики, другие выходы второго блока памяти соединены с первыми входами элементов И-НЕ, вторые входы которых подключены к выходу первого триггера, выходы элементов И-НЕ первой группы соединены с входами первого блока управления, выходы элементов И-НЕ второй группы подключены к первым входам элементов ИЛИ-НЁ вторые входы которых соединены с выходами второго триггера, а выходы -. с другими входами дешифраторов, входы триггеров подключены соответственно к третьему и чет'вертому выходам блока диагностики и выходу допол- нительЬого блока управления.S(ЛсCD00 Oiел

| Патент США № 3863059, кл. | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-15—Публикация

1976-12-16—Подача