Изобретение относится к вычислительной технике и может быть использовано для функционального диагностирования запоминающих устройств (ЗУ).

Цель изобретения - повышение надежности устройства.

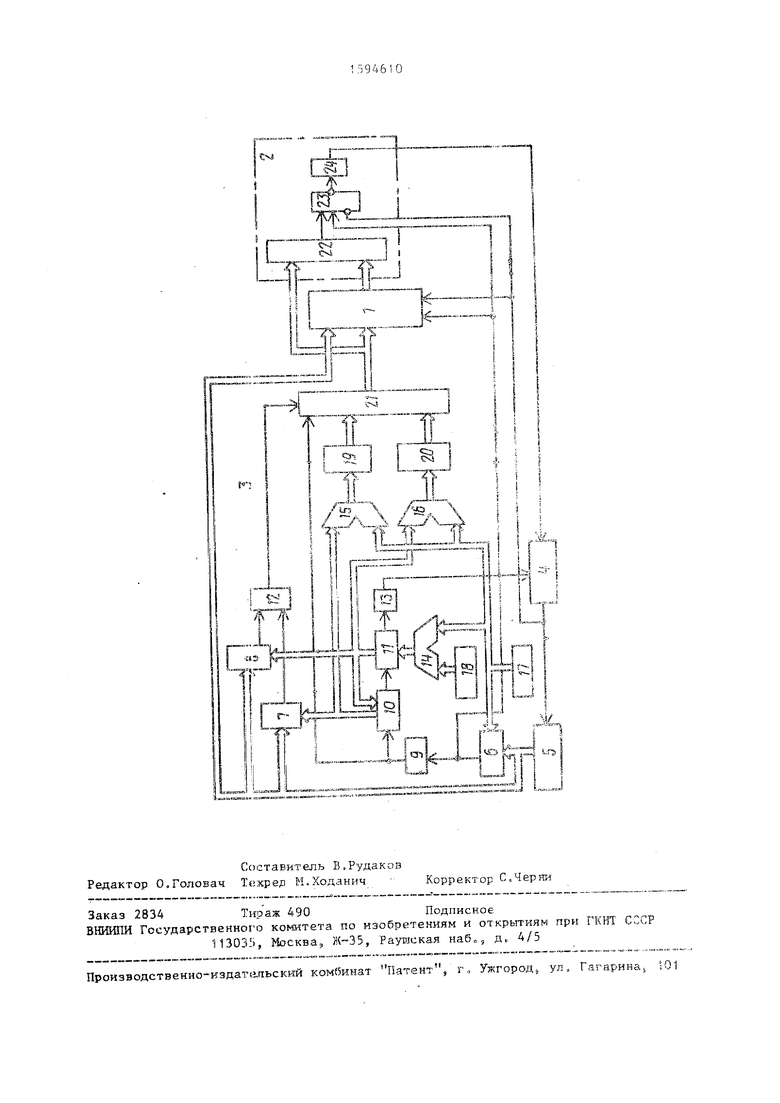

На чертеже изображена структурная схема устройства для контроля блоков памяти.

Устройство в процессе,работы под- клю чается к блоку 1 контролируемой памяти.

Устройство содержит блок 2 сравнения, имеющий выход 3, генератор 4 синхроимпульсов, счетчик 5 адресов,

первый 6, второй 7 и третий 8 мультиплексоры, первый триггер 9, счетчик 10 строк тест-программы, счетчик 11 зон тест-программы, сумматор 12 по модулю два, второй триггер 13, первый 14, второй 15 и третий 16 cyMt-ia- торы, первый 17 и второй 18 регистры, первый 19 и второй 20 преобразователи кодов, блок 21 сумматоров по модулю два.

Блок 2 содержит блок 22 поразрядного сравнения, элемент И-ЯЕ 23 и третий триггер 24,

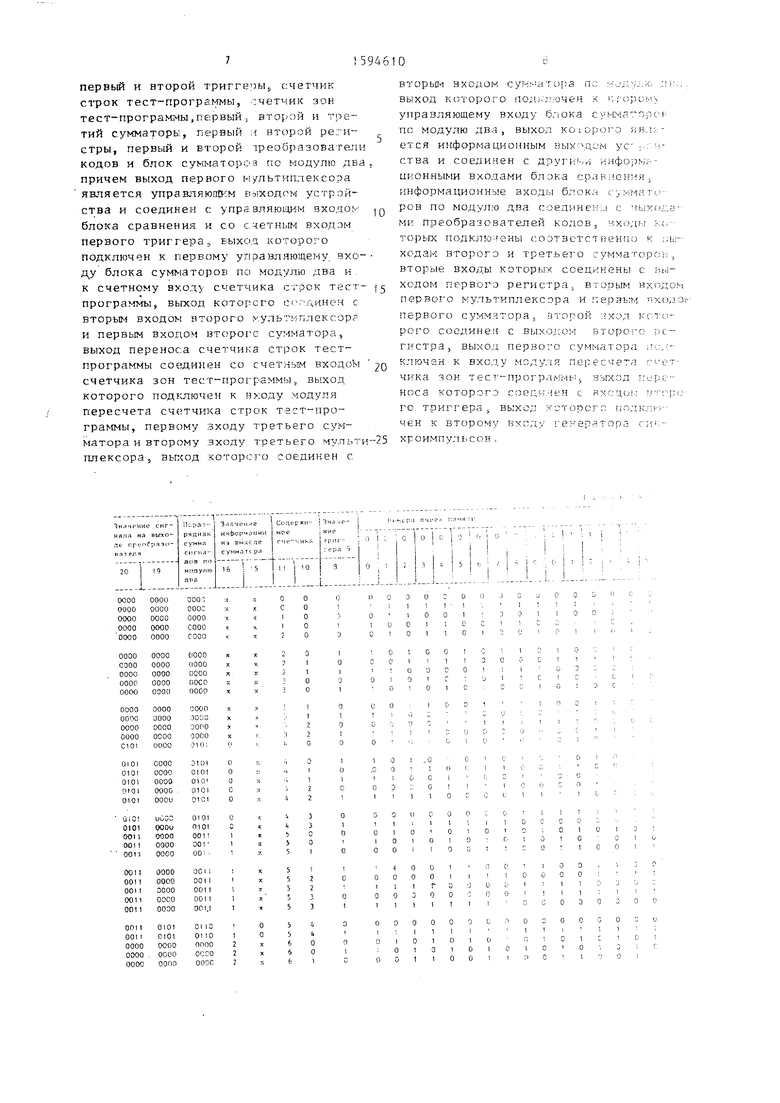

В табл, 1 приведена цифровая диаграмма работы устройства.

В правой части табл:. 1 дано знаение сигнала на ВЫКОДЕ- сумматора 12 ля каждого состояния счетчика 5. остояния этого счегчиЕ:а определяют дрес ячейки памяти и даны в загоовке.

Табл.1 построена для ЗУ объемом 6 четырехразрядных слов.

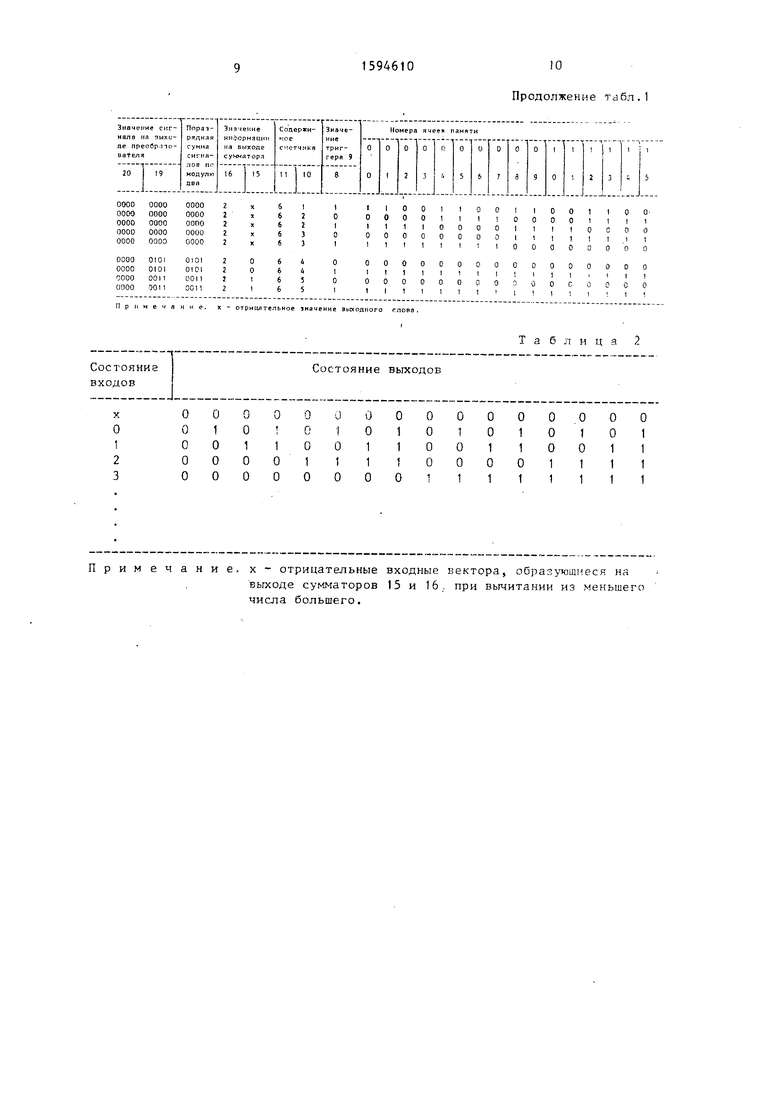

В табл. 2 приведена таблица ис- ш инности преобразователей 19 и 20.

В левой части табл.2 возможые состояния входных векторов, а в равой - соответствующие им выходные

ектора. ,

В качестве преобразователей 19 и

20 используются запрограммированное

согласно данным .габл.2 постоянные

запоминающиеся устройства,

Устройство работает следующим 20

образом.

Подача ниакогб потенциала вызывает сброс счетчиков 5, 10 и 11, триггеров 9, 13 и 24, приостановку работы генератора 4, прием в регистр 18 кода,25 равного логарифму от числа d информационных входов блока 1, прием в регистр 17 К1эда а -чис.-:а адрес1 ых входов блока V, Нумер.гция адресных входов производится О - О до а-1 . (Ue- 30 пи сброса на чертеже не показаньО .

Далее производится запись тестовых данньгх по всем адресам: блока 1 , после чего происходит чтение информации и сравнение ее с эталоном. За- тем по всем адресам записываются противоположные (ипвеотированные.) тестовые /;анные,, которые также считываются и сравниваются с эталоном.

,Вид тестовых данных зависит от дО состояния счетчиков 11 и 10, которое остается сгабильньм на протяжении описанного цикла работы. По окончании этого цикла содержимое счетчиков изменяется и работа устройства дз повторяется,, но y/se с ины№1 тестовыми данными о

В любом цикле по каядо- :у адресу блока 1 записьшаются индивидуальные значения данных, полная совокупность которых образует строку тест-прсгран- мы. Номер m пары определяется значением счетчика 10. В каждой паре первая строка содержит прямые, а вторая -- инвертированные тестовые

данные.

Совокупность строк образует зону

тест-программы,, номер z которой равен значению счетчика 1 1 ,. Счетчик 1 1

способен изменять . сост; i;-;;;e сг О до п-1, где п - чиачение 11,ан1ых его входе модуля перерасчега,

Счетчик 1(1 изменяет свое 1:о: И ние внутри ка;«дой зоны с- - У цс :г-- ;эскольку .1одулем пересчета гч1 ТЧ( ка 10 является содержимое СМРТЧК- ка 11.

Таким образом, тecт- lpcя pд:1 a ;: держит п ЗОН; где п а + ci .. а кал, дан зона состоит из г пар строк, i, Z - номер зоны. (Ыулег ая зона H;I- ляется исключением. В ней сс деркит одна пара строк, причем m О и z -- одновременно,) .

Рассмот1зи -1 уст юйзтпа п. формированию нулевой зонь гест- ш .. граммы.

Мульт иплексот5ом Ь .. служащим д;1я формированр я KOMAHJV-: запкси-чтени Быбирается а-н разр,;;:; ;че1- икл } Поскольку в качалькык 1мг;г- ент тгст г ряд равен Hy:no,Ha H:-ixo;;e :. у:;ьт пм; сора 6 г:р исутс Г;5у;-т н 1енои :н) п:, ()знача:о11;и1 комаилу загн;;- : . блок .Этот сигж л MvK. ту п/г т -i;: ра,аяю1ций BXC;J, блока , };::.:i ; ; том ДНЯ иости м;няии) чнл;;- :-;П Hvjieijcjft ::оте п;;к Л ;;а ip ;:1маг; . г,, дение от геж; ;а 1ч;иа - ; ;-п 1 ;г::и;. исстН1ЛЯН ЛИх /акис -. iiripjpr-;;: мять. Сигн;и: с: Rh;xo;i,a муг ь , г ра 6 nocTviiae i также на зл:; - еит 23, занрепая работу блока 1: в рч -к записи и ра -ре1 ;ая Б -:теч1 я.

18 с вихо.ца сумматора 1- осту;:ч.: i.. вход модуля нересчега гч:е гч;ч:я : i (эпределяя K(: :- H4t:cT)3i.i он Tt--; T--i;p :.-раммь1„

Сумматоры U; к Ь л и,:-;-;;;:;-: .;;: от . ственно из го ;ержи,уго счеч ч;г-.о; j и 11 код числа ал,ресных ,цон, хра- няаинся и регистре :/. и качь;:ы; ,,, циклах разность отрнцате; ьн;1Я , и на выходах преобразователей и 2и ;;ор шруются нули по всем иь;х;ъ ного слова (табл.2),

Мультиплексорами 7 и 8 выС-ираетс нулевой разряд счетчика 5 м его значение передается на вход с- 1матоэа 12. -Нулевой разряд в процессе пересчета адресов счетчиком Ь изменяется наиболее часто, однако на выходе сумматора 12 сохраняется постоянный потенциал при любом значении адреса. Этот сигнал передактся на один из

51

входов блока 21, на другой вход которого поступает нулевой потенгдаал с выхода триггера 9. На информационные входы блока 21 поступают нулевые векторы с выходов преобразователей 19 и 20, что ведет к записи нулей по всем адресам и по всем разрядам блока 1. После этого а-й разряд счетчика 5 устанавливается в единицу, и описанный цикл работы повторяется, но уже в режиме чтения. При этом прочитанная информация поступает с выхода блока 1 на один из входов блока 22, на другой вход которого посту пают эталонные данные. В случае несовпадения этих з-начений, хотя бы . по одному информационному разряду, происходит срабатывание блока 22 и в момент спада сигнала генератора 4 этот факт фиксируется в триггер 24, что приводит к останову работы устройства. Стробирование сигнала несовпадения синхросигналом необходимо дл исключения ложных срабать заний в мо- мент изменения состояния счетчика 5, которое происходит по фронту синхросигнала .

После того, как закончится цикл чтения и сравнения по всем адресам, срабатывает триггер 9, а (а-й) разряд счетчика 5 нновь обращается в нуль. Цикл записи повторяется, но уже с единичными данными, поскольку сигнал с выхода триггера 9, пэступая на общий вход блока 21, инвертирует все разряды тестового слова. Таким образом формируются первыи две строки табл.1.

По окончании цикла записи-чтения триггер 9 сигналом с мультиплексора 6 возвращается в нулевое состояние, задний фронт выходного сигнала триггера 9 воздействует на счетчик 10. Сигнал с выхода переноса счетчика 10 поступает на счетный вход счетчика 11, что ведет к его срабатыванию. Следующие две строки тест-программы формируются устройством для и (графы 6, 7, табл.1). При этом мультиплексором 7 выбирается нулевой -разряд, а мультиплексором 8 - первый разряд счетчика 5. Состояние этих разрядов ,изменяющееся от адреса к адре- су, смешивается в сумматоре 12 и передается на вход блока 21, на информационных входах которого по-прежнему сохраняются нулевые векторы (графы 1

6

д 0 5

0 , 0

0

о 6

2, табл,1). Следующий импульс с выхода триггера 9 переводит на короткое время счетчик 10 в состояние 1, но тут же следует его сброс, поскольку на входе модуля пересчета присутствует единичный код. Сигнал переноса с выхода счетчика 10 увеличивает содержимое счетчика 11, и устройство переходит к формироваН1-м второй зоны тест-программы () и так далее.

Нулевые данные сохраняются на выходах преобразователей 19 и 20 до тех пор, пока содержимое счетчиков 10 и 11 не сравняется или не превысит содержимое регистра 17. ЗУ объемом 16 четырехразряднкк слов впервые это происходит в четвертой зоне. Содержимое счетчика 11 п регистра 17 сравнивается, и на выходе сумматора 16 появляется )1улеаой код. При этом на выходе преобразователя 20 сформи- руется шахматный код, что ведет к инвертированию нечетных разрядов тестового слова.

Работа устройства продолжается до тех пор, пока состояние счетчиков 11 и ;0 не станет рапным п-1 и п-2 со отЕзетствен1го ,после чего происходит сброс этих счетчиков в нуль и установка тр :ггера 13. Нулевой потендиал с выхода триггера 13 останавливает генератор 4.

Формула изобретения

Устройство для контроля блоков памяти, содержащее счетчик адресов, блок cpaвнe ия, первый, второй и третий мультиплексоры, сумматор по модулю два, генератор синхроимпульсов, выход которого является синхронизирующим выходом устройства и соединен со стробирующим входом блока сравнения и счетным входом счетчика адреса,выходы которого являются ад- ресньми вь1ходами устройства и соединены с первыми входами мультиплексоров, выход второго мультиплексора подключен к первому входу сумматора по модулю два, одни из информационных входов блока сравнения являются информационными входами устройства, вход блока сравнения подключен к первому входу генератора синхроимпульсов, отличающееся тем, что, с целью повьшения надежности устройства, в него введены

первый и второй триггеры, счетчик строк тест-программы, 1:четчик: зон тест-программы (Гге.рвый ,. второй н третий сумматоры:, первый :{ второй регистры, первый и второй 1реобразоватеи 1н кодов и блок сумматорс а гю модулю два причем выход первого мультиплексора является управляющем в жодом устройства и соединен с; упра,вляюtJ м вхо.цог- блока сравнения и со с.четным входом первого триггера,, Е;ЫХО,Ц которого подключен к первому управляющему вхо блока сумматоров по модулю два и . к счетному входу счетчика строк тест- программы, выход которого с т динен с вторым входом второго у.ультмплексорр и первым входом второго сумматора, выход переноса счетчика строк тест- программы соЕщинен со счеткьм входоЫ счетчика зон тест-программы, выход, которого подтслючен к ходу модуля пересчета счетчика строк тест-про- грамь1Ы, первому входу третьего сумматора и второму входу третьего мультплексора j вькод которого соединен с

0

вторьп входом сун;-атч)ра пс :- oj;vj :) выход ксггорого (юд/а-мчеи к кг орсм-ч управляющем у входу блока сукчаг прг по модулю два, выход KOioporo HB,.U: ется информадионным БЫХ цсм yc i. M ства и соединен с друпп- л инфо;)г-;;:- ционными входами блока срлв; сь:ия , информационные входы блокя суммаго ров по модулю два соединен;:, с -ibixo ми преобразователей кодов, ;-: торых подключены соотвстст Езеимо к ходам второго и третьего cyMssaTopo вторые входы которых соединены с ь ходом первого регистра, вторым нхг. первого мультиплексора и первым - -.У: первого сумматора, ;5торой ;;ход кот рого соединен с выходюм второго Г) гистра, выход первого сумматора ;. к. почен к входу модуля пересмета чика зон тест прогр. J яъкод ;ер носа которого соедр чен с го триггера J выход которого иодк,ги-1 чей к второму вхс Д;,- генерятора rni. хроимпульсов,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Запоминающее устройство с тестовым самоконтролем | 1986 |

|

SU1396160A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО КОНТРОЛЯ | 1991 |

|

RU2015523C1 |

| Запоминающее устройство | 1985 |

|

SU1249594A1 |

| Устройство для тестового контроля больших интегральных схем | 1984 |

|

SU1218390A1 |

| Система для контроля и диагностики цифровых узлов | 1988 |

|

SU1594544A1 |

| Устройство контроля микропроцессорных блоков | 1982 |

|

SU1042023A1 |

| ФОРМИРОВАТЕЛЬ ТЕСТОВ | 1991 |

|

RU2012924C1 |

| Формирователь тестов | 1985 |

|

SU1260963A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

Изобретение относится к вычислительной технике и может быть использовано для функционального диагностирования запоминающих устройств (ЗУ) и, в частности, для контроля больших интегральных схем (БИС) ЗУ на этапе их изготовления и эксплуатации. Цель изобретения - повышение надежности устройства. Устройство содержит блок сравнения, счетчики адресов, строк и зон тест-программы, мультиплексоры, сумматоры, преобразователи кодов, сумматоры по модулю два, регистры, триггеры и генератор синхроимпульсов. Генерируемая устройством тест-программа при минимальной длине способна выявлять любые статические дефекты ЗУ (в частности БИС ЗУ), обусловленные взаимным влиянием ячеек в матрице запоминающих элементов, если число взаимно влияющих ячеек не превышает трех. 1 ил., 2 табл.

X - отрииательное значение выходного слова.

Примечание, х- отрицательные входные вектора, образующиеся на

выходе cyt jaторов 15 и 16. при вычитании иэ меньшего числа большего.

Продолжение табл,

Таблица 2

| Устройство функционального контроля интегральных схем с функцией памяти | 1978 |

|

SU748303A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-09-23—Публикация

1984-12-27—Подача