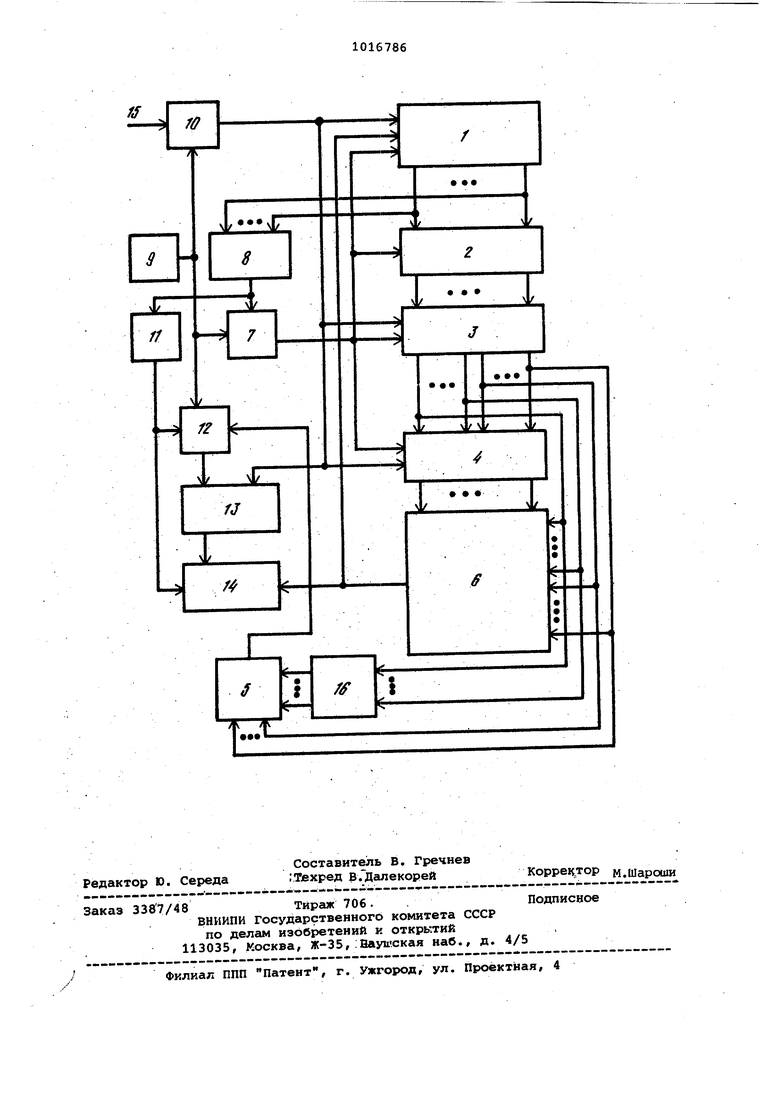

Изобретение относится к вычислительной технике и может быть исполь зовано для контроля логических схем Известно устройство для контроля цифровых узлов, содержащее блок памяти, блок сравнения, блок индикации и регистр 1. В этом устройстве при контроле логических схем можно обнаружить отказы регистра, но нельзя обнаружи отказы блока памяти/ так как возник новение отказа блока памяти будет отображено как отказ контролируемой логической схемы. Наиболее близким по технической сущности к предлагаемому является устройство для контроля цифровых блоков, содержащее блок памяти, сче чик адреса, первый и второй регистр первый блок сравнения и блок индика ции, причем выходы счетчика адреса соединены с адресными входами блока памяти, выходы блока памяти соединены с входами первого регистра, первые выходы которого подключены к первым входам первого блока сравнения f 2 3. В этом устройстве блок индикации также отображает отказы блока памяти как отказы контролируемой логической схемы и исправная логическая схема может быть принята за неисправную. Блок памяти является изделием высокой сложности, вероятность отказа которого может быть сравнима с вероятностью отказа контролиру емой логической схемы. Цель изобретения повышение надеж ности контроля путем обнаружения отказов блока памяти. Поставленная цель достигается те что в устройство для контроля логических блоков, содержащее счетчик адреса, блок памяти, два регистра, первый блок сравнения,; блок индикации, причем выходы счетчика адрес соединены с адресными входами блока памяти, первая группа входов первого блока сравнений соединена с выходами контролируемого логического блока, введены триггер, элемент ИЛИ, три элемента И, генератор тактовых импул сов, элемент задержки, второй блок сравнения, причем выходы блока памят соединены с группой входов первогб регистра, первая и вторая группы выходов которого соединены с первой группой входов второго блока сравнения и группой входов второго регистра, выходы.которого соединены р второй группой входов второго блока сравнения, первая группа выходов первого регистра соединена с входами контролируемого логического блока, вторая группа выходов первого регистра соединена с второй группой входов первого блока сравнения, выход генератора тактовых импульсов соеди нен с первыми входами трех элементов И, выход первого элемента И соединен с управляющими входами двух регистров, блока памяти и со счетным входом счетчика адреса, выходы которого соедине ны с взводами элемента ИЛИ, выход которого соединен с вторым входом первого элемента И и через элемент задержки соединен с вторым входом третьего элемента И-и управляющим входом блока индикации, вход запуска устройства соединен с вторым входом первого элемента и, выход которого соединен с ВХОДОМ начальных установок счетчика адреса и нулевыми входами триггера и двух регистров, выход второго блока сравнения соединен с первым входом блока индикации и нулевым входом счетчика адреса, выход первого блока сравнения соединен с третьим входом третьего элемента И, выход которого соединен с единичным входом триггера,выход которого соединен с вторым входом блока индикации. На чертеже представлены функциональная схема устройства для контроля логических блоков и контролируемый логический блок. Устройство содержит счетчик 1 адреса, блок 2 памяти, первый регистр 3, второй регистр 4, первый блок 5 сравнения, второй блок 6 сравнения, первый элемент И 7, элемент ИЛИ 8, генератор 9 тактовых импульсов, второй элемент .И Ю, элемент 11 задержки, третий элемент И 12, триггер 13,блок 14 индикации, вход 15 запуска устройства и контролируемый логический -блок 16. Блок 2 памяти предназначен для хранения и выдачи в первый регистр 3 тестовой информации - упорядоченной последовательности тестов. Каждая ячейка блока 2 памяти разделёйа на две зоны. В разрядах первой зоны ячейки хранятся стимулы - набор сигналов, подаваемых на входы контролируемого логического блока 16, в разря-дах второй зоны хранятся эталоны набор сигналов, которые должны появиться на выходах контролируемого логического блока 16, если он исправен. /Первая зона каждой ячейки блока 2 памяти состоит из п двоичных разрядов (по количеству входов контролируемрго логического блока 16), вторая зона каждой ячейки блока 2 содержит m двоичных разрядов ( по количеству вьахрдрв контролируемого логического блока 16). При этом первый (старший ) разряд ячейки соответствует первому входу, второй разряд - второму входу, п-ый разряд - п-ому входу логического блока 16, (п+-1Ьый разряд ячейки - первому выходу, (п + 2) -ый разряд - второму выходу, ..., (п+ + m )-ый разряд (младший ) - т-му выходу логического блока 1-6. Таким , образом, в каждой ячейке блока 2 па мяти хранится один тест - набор сти мулов и эталонов, представляющих со бой 1 п + m ) разрядное двоичное числ ) ( ..2 к I - т . , т. j , ... , Х j г - «i-ii-. где i - номер ячейки блока 2 памяти к - количество ячеёй блока 2 памяти Двоичному числу Т соответствует десятичный эквивалент Д. n+m . д,,Ш,т.п-, Тестовая последовательность, эаписанная в ячейках блока 2 памяти упо рядочена по следующему правилу. Десятичный эквивалент Д. теста Т., эа санного в ячейке i, меньше или раве десятичному эквиваленту Д 4.,, теста Т- , записанного в {i + 1 )-й ячейке. Если длина тестовой последовательности количество, тестов ) контролируемого логического блока 16 оказалась меньше количества ячеек блока 2 памяти , то в ксокдой из оставшихся ячеек блока 2 памят располагается последний тест Т , имеющий наибольший десятичный эквив лент Дд. Следовательно тестовая информация в блоке 2 памяти расположе на в порядке неубывания десятичных эквивалентов тестов. Счетчик 1 адреса предназначен для выбора адресов ячевк.,блрка 2 памяти таким образс)м, чтoбJЦ щecты считывались из блока 2 памяти в порядке возрастания номеров хранящих их ячеек. Первый регистр 3 предназначен дл хранения одного теста Т и выдачи в течение одного такта стимулов на. контролируемый логический блок ;1б и эталонов на первый блок 5 сравнен Второй регистр 4 предназначен для хранения теста Т-, используемого. для контроля логического блока 16 в предыдущем такте. Первый блок 5 сравнения предна1эначен для поразрядного )внения значейий эталонов теста и выходн реакций контролируемого логического блока 16 на стимулы теста. Второй блок 6 сравнения предназначен для сравнения десятичного эквивалента Д. теста ., хранящегося во.втором регистре 4 с десятин ным эквивалентом Д,- теста Tj , хран щегося в первом регистре 3. Блок 14 индикации отображает технологическо состояние контролируемого, логического блока 16 и блока 2 памйтй. Устройство работает следующим образом. После, подачи на вход 15 запуска устройства импульса запуска, длительность которого не меньше период повторения тактовых импульсов генератора 9 тактовых импульсов, на выходе второго элемента И 10 в момент, соответствующий появлению на его первом входе импульса генератора 9 тактовых импульсов, появляется импульс, который подается на входа установки в ноль триггера 13 регистров 3 и 4, и на вход начсшьных установок счетчика 1 адреса. Триггер 13 и регистры 3 и 4 устанавливаются Ё нулевое состояние а счетчик 1 адреса устанавливается в состояние, соответствующее записи в него одного импульса. С выходов счетчика 1 адреса на адресные входы блока 2 памяти и входы элемента ИЛИ 8 поступают сигналы, соответствующие адресу первой ячейки блока 2 памяти. Однако считывания информации из этой ячейки блока 2 памяти не происходит, так как на управляющие входы блока 2 памяти и регистров 3 и 4 не подан тактовый импульс генератора 9. Появившийся на одном из выходов счетчика 1 сщреса сигнал Логическая единица, пройдет через элемент ИЛИ 8 на пер- вый вход первого элемента и 7, разрешая прохождение тактовых импульсов с выхода генератора 9 через первый элемент. 17 на счетный вход счетчика 1 адреса, управляющие входы бло-ка 2 памяти, регистров 3 и 4, и через элемент 11 задержки на один такт, на второй вход третьего элемента И 12. По первому тактовому импульсу, поCTynijBmeMy с выхода генератора 9 через первый элемент И 7, происходит считывание первого теста Т, хранящегося в первой ячейке блока 2 памяти, и запись этого теста в первый регистр 3. При этом второй регистр 4 остается в нулевом состоянии. С первой группы выходов первого регистра 3 стимулы поступят на входы контролируемого логического блока 16, а эталоны с второй группы выходовпервого регистра 3 поступят на вторую группу входов первого блока 5 сравнения. На первую группу входов блока 5 сравнения начинают поступать сигналы с выходов контролируемого логического блока 16 - реакция на стимулы первого теста. Кроме того, первый тест с первой и второй групп выходов регистра 3 поступает на первую группу входов блока 6 сравнения, на вторую группу входов которого поступает нулевая комбинация сигналов с выходов второго регистра 4. К моменту появления на выходе генератора 9 тактовых импульсов второго тактового импульса на выходе элёмейта 11 задержки появляется сигнал логическая единица, который поступйет на второй вход третьего элемента И 12. Если контролируемый логический блок 16 неисправен и его реакция на стимулы первого теста не

правильная, то с выхода первого блока 5 сравнения на третий вход третьего элемента И 12 поступает сигнал Логическая едница. При этом второй тактовый импульс, поступая на первый вход третьего элемента И 12, проходит через третий элемент И 12 на единичный вход триггера 13--и устанавливает его в единичное состояние, соответствующее неисправности коН тролируемого логического блока 16,

Если К моменту появления на выходе генератора 9 тактовых импульсов второго тактового импульса реакция контролируемого логического блока 16 на стимулы первого теста соответствует эталонам, то на выходе первого блока 5 сравнения установится сигнал Логический ноль, который, поступая на третий вход третьего элемента И 12, запретит поступление вторрго,тактового импульса на единичный вход триггера 13,

Второй тактовый импульс генератора 9 тактовых импульсов через первый элемент И 7 подается на счетный вход счетчика 1 адреса и на управляющие входы блока 2 памяти и регистров 3 и 4. После окончания второго тактового импульса второй тест из второй ячейки блока 2 памяти запишется в первый регистр 3 и поступит на контролируемого логического блока 16 и вторую группу входов первого блока 5 сравнения, первый тест из первого регистра 3 перепишется во второй регистр 4, а в счетчике 1 адреса добавится один импульс. На выходах счетчика 1 адреса установятся сигналы, .соответствующие адресу следующей, третьей ячейки блока 2 памяти,

Таким образом, по каждому (i + 1Ь ому тактовому импульсу генератора 9, проходящему на выход первого элемента И 7, с выхода первого блока 5 сравнения через третий элемент И 12 на единичный вход триггера 13 происходит передача сигнала о результате сравнения сигналов с.выходов контролируемого логического блока 16 с эталонами теста Tj , В то же время во втором блоке 6 сравнения происходит сравнение десятичных эквивалентов Д и flj -тестов и Т. хранящихся соответственно в регистрах 3 и 4, Если Д,- R. то сигнал Логическая единица , соответствующий неисправности блока 2 памяти, поступит на первый вход- блока 14 индикации И на вход установки в ноль счетчика 1 адреса. При этом счетчик 1 адреса установится в нулевое состояние и с выхода элемента ИЛИ 8 сигнал Логический ноль поступит на второй вход первого элемента И 7, запрещая подачу импульсов генератора 9 тактовых импулсов на счетный вход счетчика 1 адреса и управляющие входы блока 2 памяти

регистров 3 и 4. С задержкой на один .такт сигнал Логический ноль с вмхода элемента ИЛИ 8 через элемент 11 задержки поступит на второй вход третьего элемента И 12 и управляющий вход блока 14 индикации.

Сигнал Логический ноль, поступиший на управляющий вход блока 14 индикации, разрешит отображение неисправности блока 2 памяти.

В том случае, когда при сравнении во втором блоке 6 сравнения оказалос что Д ), Д.на выходе блока 6 появляется сигнал исправности блока 2 памяти Логический ноль, который не обнуляет:-счетчик 1 адреса. При этом работа устройства п юдолжится и на счетный вход счетчика 1 адреса, /. управляющие входы блока 2 памяти регистров 3 и 4 через первый элемент И 7 поступит следующий тактовый импульс.

Если в момент подачи очередного тактового импульса на выходе первого бпока 5 сравнения установится сигнал неисправности контролируемого логического блока 16 Логическая единица, то импульс, появившийся на выходе генератора 9 пройдет через третий элемент И 12 на единичный вход триггера 13, Триггер 13 установится, в единичное состояние, запомнив факт проявления несиправности блока 16, а сигнал Логическая единица с его единичного выхода поступит на второй вход блока 14 индикации. Работа устройства при этом не прекращается и тактовые импульсы генератора 9 будут поступать на выход первого элемета И 7 ,

Предпоследний, к-ый тактовый им-/ пульс генератора 9 тактовых импульсов, пройдя через первый элемент И 7, поступит на счетный вход счетчика 1 адреса. При этом счетчик 1 адреса установится в нулевое состояние, а из последней ячейки блока 2 памяти будет записан в первый регистр 3 последний тест Т,стимулы которого поступят на входы контролируемого логического блока 16, а эталоны - на вторую группу входов первого блока 5 сравнения.

После обнуления счетчика 1 адреса сигнал Логический ноль с выхода элемента ИЛИ 8 поступит на второй вход первого элемента И 7 и запретит прохождение тактовых импульсов с выхода генератора 9 через первый элемент И 7, С задержкой, на один такт .сигнал Логический ноль с выхода элемента ИЛИ 8 через элемент 11 задержки поступит на управляющий вход блока 14 индикации и на второй вход третьего элемента И 12, Если при сранении по последнему тесту на выходе первого блока 5 сравнения появится сигнал неисправности контролируемого логического блока 16 Логическая единица , то ввиду задержки на один такт сигнала с выхода элемента ИЛИ 8 последнийДк + 1)-ый иишульс генератора 9 тактовь:х импульсов, поступивший на первый: вход третьего эле.мента И 12, пройдет на единичный вход триггера 13. Триггер 13, если он был и нулевом состоянии,установится в еди.ничное состояние.При этом сигнал Логическая единица с единичного выхода триггера 13 поступит на второй вход блока 14 индикации,.а сигнал Логический ноль, поданный на управ лякмций вход блока 14 индикации, разрешит отображение неисправности контролируемого логического блока 16. Если после обнуления счетчика 1 адреса и псзступления последнего тактового импульса с выхода генератора 9 триггер 13 будет находиться в нуле вом состоянии и с выхода второго бло |ка 6 сравнения на первый вход блоЬса 14 индикации будет подаваться сигнал Логический НОЛ1,, свидетельствующий об отсутствии . неисправнЪЬти блока 2 памяти, то сигйал Логический ноль, поступивший с выхода элемента 11 задержки на управлякивий вход блока 14 индикации, разрешит отображение в блоке 14 индикации исправного состояния контролируемого логического блока 16 и блока 2 памяти. .Таким образом, предлагаемое устpoidcTBo дает во время {сонтроля логических блоков KOHTJPOлировать техническое состояние ,блока 2 памяти и обнаруживать неисправности блока 2 памяти, приводящие к нарушению условия расположения тестов в ячейках блока 2 памяти в порядке неубывания десятичных эквивалентов тестов..

fS

rff

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1982 |

|

SU1086433A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1988 |

|

SU1681304A1 |

| Устройство для контроля дискретных объектов | 1984 |

|

SU1242958A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для программного контроля | 1987 |

|

SU1464142A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для тестового контроля цифровых блоков | 1983 |

|

SU1136169A1 |

| Устройство для диагностирования логических блоков | 1986 |

|

SU1520518A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯЛОГИЧЕСКИХ БЛОКОВ, содержащее счетчик адреса, блок памяти, два регистра, первый блок сравнения, блок индикации, причем выходы счетчика адреса соединены с адресныкда входами блока памяти, первая группа входов первого блока сравнения соединена с выходами контролируемого логического блока, отличак1щееся тем, что, с целью повышения надежности контроля путём обнаружения отказов блока памяти, введены триггер, элемент ИЛИ, три элемента И, генератор тактовых импульсов, элемент задержки, второй блок сравнения, причем выходы блока памяти соединены с группой входов первого регистра, первая и вторая группы выходов которого соединены с первой группой входов второго блока сравнения и группой входов второго регистра, выходы которого соедит иены с второй группой входов второго блока сравнения, первая группа выходов первого регистра соединена с входами контролируемого логического блока, вторая группа выходов первого регистра соединена с втосюй группой входов первого блока сравяевия, выход генератора тактовых икшульсов соединен с первыми входами тре,х элемен тов И, &ЫХОД первого элемента И соединен с управляющи1 в1 входами двух регистров, блока памяти и со счетньт входом счетчика адреса, выходы Которого соединены с входами элемента ИЛИ, выход которого соединен с вторым ВХОДСЯ4 первого элемента И и чет рез элемент задержки соединен с втО рым входом элемента И и (Л управлякицим входом блока и щикацки, вход запуска устройства соединен с входе второго элемента И, выход которого соединен с входом начальных установок счетчика адаеса и нулевьвли входами триггера и двух регистров , выход второго блока сравнения соединен с первьаи входом Спока индикации и нулевым входом счетчика адреса, выход первого блока сравнения Од соединен с третьим входом третьего элемента И, которого,соединен с единичным входом триггера, выход 00 которого соединен с вторым входом О) блока индикации.

vl/

8

i

//

//

4 i/

fj

f

ji.

/ /i t

-$

l

$4f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для контроля цифровых блоков | 1975 |

|

SU607218A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| , | |||

Авторы

Даты

1983-05-07—Публикация

1981-07-28—Подача