Изобретение относится к цифровой вычислительной технике. Известно вычислительное устройств последовательного действия, содержащее несколько сумматоров EIJ Недостатком такого устройства яеляется низкая производительность. Наиболее близким по технической сущности является операционное устройство {2}, содержащее в каждом канале управляющий триггер, единичны и нулевой входы которого соединены через элементы И с выходами соответствующих элементов ИЛИ-НЕ, входы которого- соединены с соответствующим входами устройства, и приемный триггер. Выходы управляющего триггера через элементы 2И-ИЛИ соединены с входом последующего канала. Входы приемного триггера через элементы И соединены с.соответствующим входом устройства. Выход одного элемента И соединен через первый элемент НЕ со входом другого элемента И. Выход управляющего триггера соединен с первы входом реверсивного параллельного сдвигателя, второй вход которого сое динен с соответствующим входом устро ства . Вход одного элемента и приемtsdro триггера соединен с выходом пер вого коммутатора, а выход второго элемента НЕ - со входом -нулевого элемента И управляющего триггера. Недостатками этого устройства являются низкое быстродействие и ограниченные функциональные возможности. ; .Цель: изобретения-1 С ВБШ1ёнйё быстродействия и расширение функциональных возможностей путем обеспечения вычисления операций преобразования координат. Поставленная цель достигается тем, что в предложенное устройство введены три триггера с соответствующими элементами И, 2Й-ИЛИ и второй крмиутатор. Выход реверсивного параллельного сдвигателя соединён с первыми входами элементов 2И-ИЛИ всех триггеров и входами коммутаторов. Вторые входы элементов 2И-ИЛИ соединены с выходом элемента 2И-ИЛИ управляющего триггера предьщущего канала. Третзьи и четверTijie входы элементов 2И-ИЛИ соединены с выходами .соседних каналов. Выход каждого введенного элемента 2И-1ШИ через элементы И соединен с единичными и нулевыми входами соответствующих триггеров. Входы единичныхи нулевых элементов И введенных триггеров -соединены соответственно с нулевым и единичным выходами управляющег триггера. Выходы введенных триггеров .соединены со входами реверсивного параллельного сдвигателя и второго коммутатора, управляющий вход которого соединен с со этветству ощим входом устройства. Выход второго коммутатора соединен непосредственно .со входом первого коммутатора и входами единичного элемента И управляющего триггера и второго элемента НЕ.

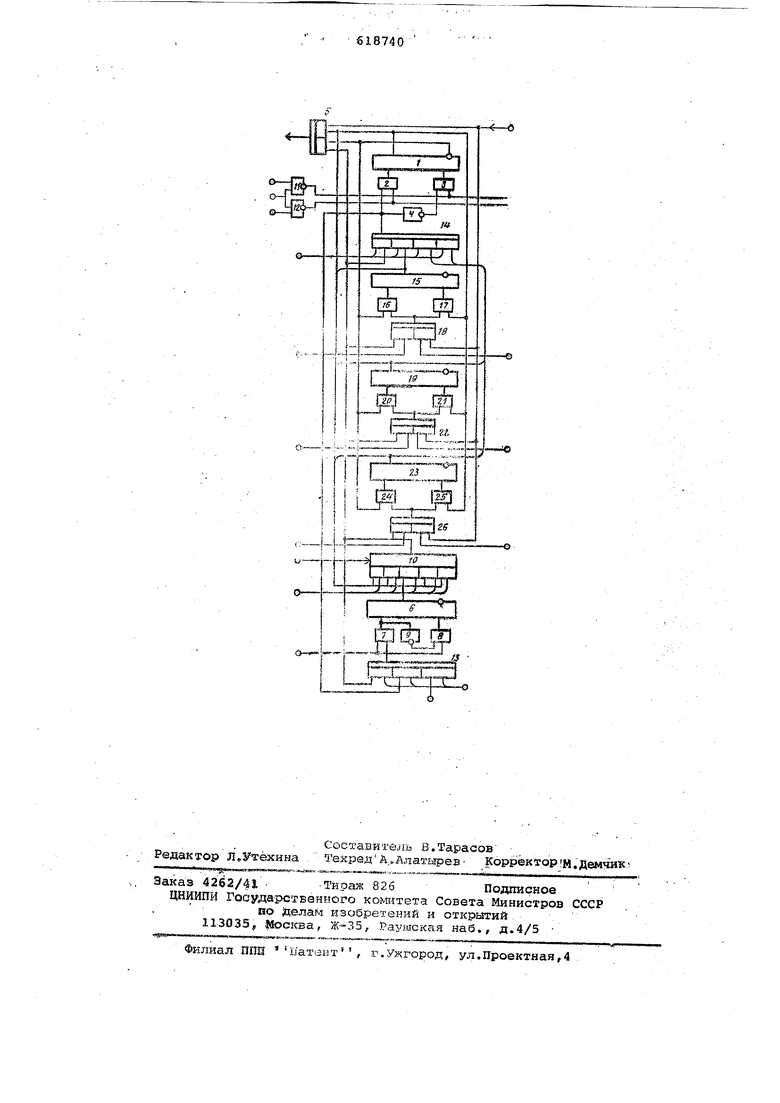

На чертеже приведена структурная схема одного канала устройства.

Каждый канал содержит управляющий триггер 1 с элементами И 2, 3, НЕ 4, 2И-ИЛИ. 5, приемный триггер б с элементами И 7,8, НЕ 9, реверсивный параллельный сдвигатель 10, элементы ИЛИ-НЕ 11, 12, коммутаторы 13, 14./. триггер 15 с элементами И 16,17, 2И-ИЛИ 18, триггер 19 с элементами И 20, 21, 2И-ИЛИ 22, триггер 23 с элементами И 24, 25 и 2И-ИЛИ 26. . Совокупности триггеров во всех канат лах составляют регистры.

Рассмотрим работу устройства на примере вычисления элементарной функции поворота вектора по алгоритму цифра за цифрой, т.е. вычислим координаты вектора х, ,повернутого на угол о( по следующей системе уравнени

XCosoLT YSinoL,

С-1) VS-inoL ± XCosot.

Поворот вектора на угол oL в диапазог не 1&0° $ci +180 осуществляется с помощью серии последовательных поворотов на заранее предрасчитанные углы|о1, значения которых определяются йыражением (2) и хранятся в ЗУ

-.i-2

ос aTctg- 2

для Ь С2)

где 1 - номер итерации При i- 1 поворот вектора осуществляется на .:±90°, а при()-на 45 к т;д. BeKT6p:j поворачивается на базисную последовательность углов таком направлении, чтобы суммарное значение угла «А , определяемое выражением (3), стремилось к нулю, а.е.

с4/с

0

.d.V

СЗ)

1где л- число итераций, определяемое длиной разрядной сетки вычислителя;

g S +1 и характеризует направление прйорота.

Значение .определяется выражением (4)

i-A

- sig-n :d:-s,-oL).

riii

d

С каждым поворотом текущее значение координат вектора определяется выражениями (5) и (6)

V.-V -f V ) ilH

(5)

V . X Y . -v. X я (i-)

4 1- i l- . (6)

Из приведенных выражений (3)-(6). видно, что для получения текущих координат необходимо к предыдущему значению прибавить или вычесть из него сдвинутое значение ординаты или абсциссы, а управление вычислительным процессом осуществляется, по знаку угла cL .

Перед началом работы уголи координаты исходного вектора записываются в триггеры 15,19 и 23. Информация из регистра 5 переписывается в триггер 1. Из памяти мащины константа считывается в триггер 8. Затем содержимое триггера 6 без сдвига .передается в триггер 16 и там вычитается (суммируется) по модулю с его содержимым.

Содержимое регистра 15 передается в триггер 1. При возникновении сигналов переноса они записываются в триггер 15,и полученное значение угла хранится в нем до следующей итерации .

Затем вычисляется одна из координат. При этом ее значение используется и для вычисления другой координаты. При этом содержимое триггера 9 через коммутатор 14 переписьшается в триггеры 1,6, а триггер 23 подключается на вход сдвигателя 10.

В триггере 19 производится сложение (вычитание) по модулю два его содержимого с содержимым триггера 23 сдвинутым в сдвигателе 10 на необходимое число разрядов.

Содержимое триггера 19 передается в триггер 1. При возникновении переносов, они фиксируются в триггере 19.

Затем вычисляется значение другой координаты. Содержимое триггера 23 передается в триггер 1, а триггер 6 подключается на вход сдвигателя 10.

В триггере 23 производится сложение- . (вычитание) по модулю два его содержимого с содержимым триггера 19 сдвинутым на необходимое число разрядов в сдвигателе 10. Содержимое триггера 23 передается в триггер 1. При возникновении переносов они фиксируются в триггере 23.

Из рассмотренного примера вычисления функции поворота вектора видно, что за время, равное времени выполнения трех операций умножения вычисляется система уравнений 1, . которая включает две функции eind:,Coa четыре операции умножениями две операции типа сложение {вычитание),т.е. производительность, .аычислительнрй машины значительно увеличивается по S сравнению с программным методом элементарных функций. Таким образом, функциональные во можности предлагаемого многоканального ойерационного устройства вычисления элементарных функций расширены, что позволяет повысить производительность вычислительной машины и уменьшить количество оборудова ния по сравнению с трехпроцессорным вычислителем. Формула изобретения Многоканальное операционное устройство, содержащее в каждом канале управляющий триггер, единичный и нулевой входы которого соединены , через элементы И с выходами соответ ствующих элементов ИЛИ-НЕ, входы которых соединены с соответствующим входами устройства, выходы управ ляющего триггера через элементы 2И-ИЛИ соединены с входом погпедующего канала, приемный триггер, вход которого через элементы И соединены с соответствующим входом устройства выход одного элемента И соединен через первый элемент НЕ со входом другого элемента И, выход управляющего триггера соединен с первым вхо дом реверсивного параллельного сдви гателя, второй вход которого соединен с соответствуюцщм входом устрой ства, вход одного элемента И приемного триггера соединен с выходом первого коммутатора, выход второго элемента НЕ соединен со входом нуле вого элемента И управляющего тригге ра, отличающееся тем. что, с целью повышения быстродействия и расширения функциональных возможностей путем обеспечения возможности вычисления координат, в него введены три триггера с соответству ощими элементами И, 2И-ИЛИ и второй коммутатор, выход реверсивного параллельного сдвигателя соединен с первыми входами элементов 2И-ИЛИ всех триггеров и входами коммутаторов; вторые входы элементов 2И-ИЛИ соединены с выходом элемента 2И-ИЛИ управляющего триггера предыдущего канала; третьи и.четвертые входы элементов 2И-ИЛИ соединены с выходёМИ соседних каналов; выход каждого введенного элемента 2И-ИЛИ через элеменг ты И соединен с единичными и нулевыми входами соответствующих триггеров, входы единичных и нулевых элементов И введенных триггеров соединены соответственно с нулевым :и единичным выходами управляющего триггера; выходы введенных триггеров соединены со входами реверсивного параллельного сдвигателя и второго коммутатора, управляющий вход которого соединен с соответствующим входом устройства; выход второго коммутатора соединен непосредственно со входом устройства; выход второго коммутатора соединен непосредственно со входом первого коммутатора и входами единичного элемента И управляющего триггера и второго элемента НЕ. Источники информации,принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 445042, кл. GОб F 7/38, 08.74. 2.Авторское свидетельство СССР 362295, кл. Q 06 F 7/38, 11.70.

-б

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Устройство интерполяции для отображения графической информации | 1984 |

|

SU1164732A1 |

| Преобразователь координат | 1988 |

|

SU1566345A1 |

| Вычислительное устройство | 1983 |

|

SU1167604A1 |

| Векторный процессор | 1979 |

|

SU849228A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для цифрового преобразования координат | 1982 |

|

SU1019445A1 |

| Устройство для поворота вектора | 1982 |

|

SU1076910A1 |

| Мультипроцессорное вычислительное устройство с параллельной обработкой информации | 1972 |

|

SU492880A1 |

| Процессор для вычисления элементарных функций | 1979 |

|

SU888131A1 |

a- ««- i--

Авторы

Даты

1978-08-05—Публикация

1975-09-29—Подача