Изобретение относится к цифровой вычислительной технике и может бытЬ использовано в высокопроизводительных вычислительных машинах и в автономных вычислителях. Известен процессор параллельного де ствия с накапливающим сумматором lj который вычисляет э;кментарные функци аппаратурным способом по послецовательно-параллельному алгоритму. Устройство еодержит три параллельных накапливающих сумматора, выполненных на трех perHcipax со счетным входом и одним общим управляющим регистром, а также приемный регистр и параллельный сдвигатель. Недостатком такого процессора является его низкая производительность. Наиболее близким техническим решением к изобретению является процессор 2 , вьтолняющий вычисление элементарных функций по параллельно-параллельн му алгоритму и содержащий три параллельных накапливающих сумматора, два сдвигателя, два коммутатора, постоянное запоминающее устройство и устройство управления, первый и второй выходы которого соединены соответственно с первым и вторым входами сумматоров третий и четвертый выходы устройства управления соединены соответственно с первыми входами сдвигателей и коммутаторов, а пятый выход соецинен с посто5шным запоминающим устройством, выход которого соединен с третьим входом первого накапливающего сумматора, а первые выходы сумматоре соединены с входом устройства управления. Недостатком известного процессора является низкая производительность. Например, на этом процессоре вычисление элементарных функций типа arcsih , агСС05, алгоритму цифра за цифрой можно выполнять только за время четырех команд умножения, поскольку каждую итерацию приходится выполнять за два этапа. На первом этапе определяется знак операции, а на втором этапе 3 произвооится собственно вычисление, при чем, кажаая .итерация, выполняется оваж аы. Можно повысить производительность процессора в два раза, если совместить по времени выполнение первого и второг этапов. Целью изобретения является повышени быстродействия. Поставленная цель достигается тем, что в устройство, содержащее три сумма тора, два с двигателя, два коммутатора, блок памяти и блок управления, первый выход которого подключен к первым вхо Цам сумматоров, вторые входы которых соединены с вторым выходом блока управления, вход которого соединен с первыми выходами сумматоров, третий выход блока управления соединен с первыми входами сдвигателей, четвертый выход блока управления соединен с управляющими входами коммутаторов, пятый выход блока управления соединен с входом блока- памяти, выход которого соединен с третьим входом первого сумматора, введен четвертый сумматор, первый и второй входы которого соединены с первым и вторым входами блока управления соответственно, третьи входы второго и четвертого сумматоров соединены с выходом первого с двигателя, вход которого соединен с выходом первого коммутатора, третий вход третьего сумматора соединен с выходом вгорого сдвигателя; вторбй вход которого соединен с выходом второго коммутатора, первый и второй информационные входы которого соединены с вторыми входами второго и третьего сумматоров, первый и второй информационные входы первого коммутатора соедине ны со втфыми выходами третьего и второго сумматоров соответственно. Блок-схема устройства представлена на чертеже. Устройство содержит сумматоры 1 4, с двигатели 5 и 6, коммутаторы 7 и 8, блок 9 памяти и блок Ю управления Блок 10 содержит генератор импульсов дешифратор и группу элементов И-НЕ. Работу устройства рассмотрим на примере вычисления функций ,, arccos, . Известно, что по численному методу цифра за цифрой функцию arcqiи можно вычистшть с использованием следующих рекуррентных формул: Х.-Х..€., Ш 1 .-eiN-.:.,--,,-x,., л I-i i Q (4) ае Q: - угловые константы, вычисленные предварительно по формуле Q -Qix-t Z оператор поворота вектора, определяющий знак в операции, , еслис(. иначе е. -1. Индекс - характеризует номер итерации, причем каждая итерация должна выполняться дважды. Максимальное количество итераций определяется выбранной разрядностью И процессора, т.е. лпц И. Линейные координаты вектора X и У будем вычислять соответственно на сумматорах 1 и 2, а угловую координа- ту - на сумматоре 3, Включенный четвертый сумматор 4 позволяет свести операции определения знака к простому анализу содержимого сумматоров . Для этого первые выходы сумматоров соединены с входом блока управления, который на втором выходе формирует соответствующее значение для каждого сумматора. Сдвинутые значения - и Х,( на ( -i -1) разрядов вправо соЪтветственно сдвигателями 5 и 6 поступают на третьи входы сумматора. Непосредственное выполнение сложениявычитания производится под воздействием синхронизирующих импульсов, поступающих на первые входы с первого выхода блока управления. Разрешение для сдвига операндов X и У формируется третьим выходом блока управления, а четвертый выход формирует сигналы Для коммутаторов 7 и 8, пропуская на вход сдвигателя соответствующую координату вектора X или У, Пятый выход устройства управления формирует а(чэеса константы , которые хранятся в постоянном запоминающем устройстве. Начальные координаты вектора(Уо ,Vo-O,Xo-C,)зaпиcывaютcя в соответствующие сумматоры I, 2, 3 и 4, где 1C- коэффициент масштабирования, который вычисляется по формуле К--ПИ4 2 - )

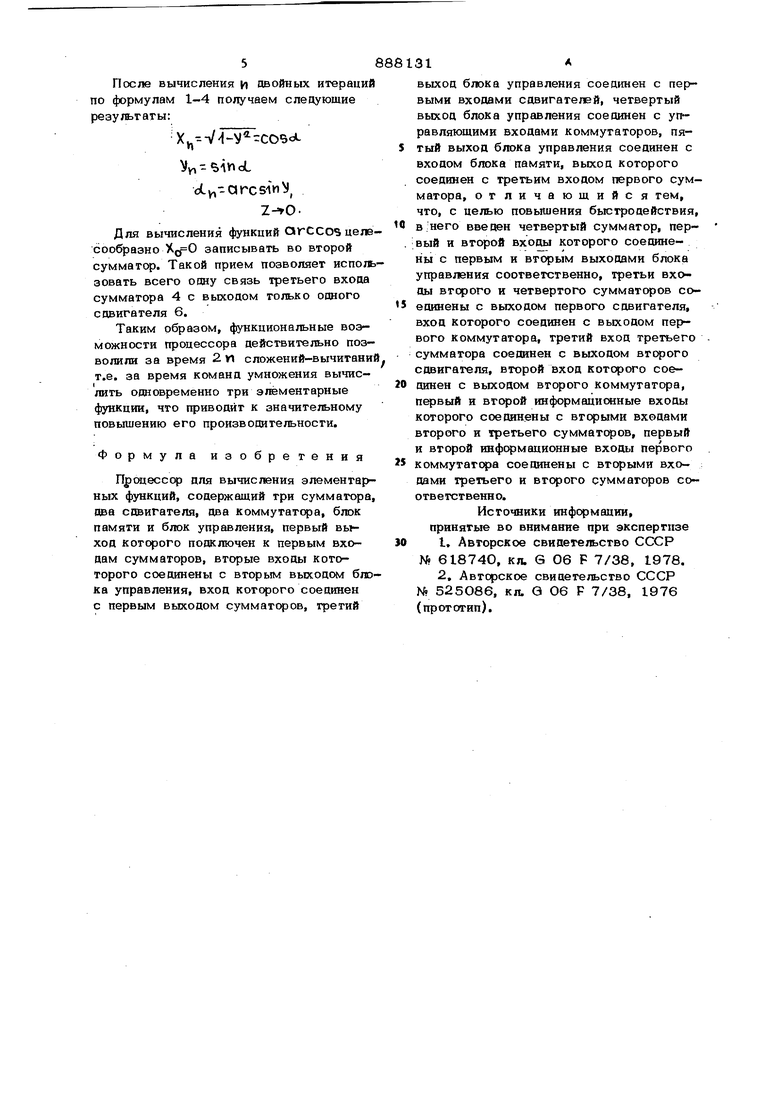

Псюле вычисления и двойных итераций по формулам 1-4 получаем следующие резуга гагы:

Xj V-l-v -cosc

Vv,

dLy,-arcsiM

Z-rOДля вычисления функций OrCCOS целесообразно записывать во второй сумматор. Такой прием позволяет использовать всего одну связь третьего входа сумматора 4 с выходом только одного сдвигателя 6.

Таким образом, функциональные возможности процессора действительно позволили за время 2 М сложений-вычитаний т.е. за время команд умножения вычислить одновременно три элементарные функции, что приводит к значительному повышению его производительности.

Формула изобретения

Пршессор для вычисления элементарных функций, содержащий три сумматора, два сдвигателя, два коммутатфа, блок памяти и блок управления, первый выход которого подключен к первым входам сумматоров, вторые входы кототорого соединены с вторым выходом блока управления, вход которого соединен с первым выходом сумматоров, третий

выход блока управления соединен с первыми входами сдвигатешй, четвертый вькод блока управления соединен с управляющими входами коммутаторов, пятый выход блока управления соединен с входом блока памяти, выход которого соединен с третьим входом первого сумматора, отличающийся тем, что, с целью повьпиения бьютродействия,

в;него введен четвертый сумматор, первый и второй входы которого соединены с первым и вторым выходами блока управления соответственно, третьи входы второго и четвертого сумматоров соединены с выходом первого сдвигателя, вход которого соединен с выходом первого коммутатора, третий вход третьего сумматора соединен с выходом второго сдвигателя, второй вход которого соединен с выходом второго коммутатора, первый и второй информационные входы которого соединены с вторыми входами второго и третьего сумматоров, первый и второй информационные входы первого коммутатора соединены с вторыми входами третьего и второго сумматоров соответственно.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР W 618740, кл. G 06 F 7/38, 1978.

2, Авторское свидетельство СССР N 525О86, кл. Q 06 F 7/38, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Векторный процессор | 1979 |

|

SU849228A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1130861A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU1103225A1 |

| Цифровой функциональный преобразователь | 1981 |

|

SU1105888A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| Вычислительное устройство | 1986 |

|

SU1322270A1 |

| Устройство для вычисления элементарных функций | 1979 |

|

SU890402A2 |

| Цифровой преобразователь координат | 1981 |

|

SU1076903A1 |

| Устройство для вычисления элементарных функций | 1982 |

|

SU1141399A1 |

Авторы

Даты

1981-12-07—Публикация

1979-11-11—Подача