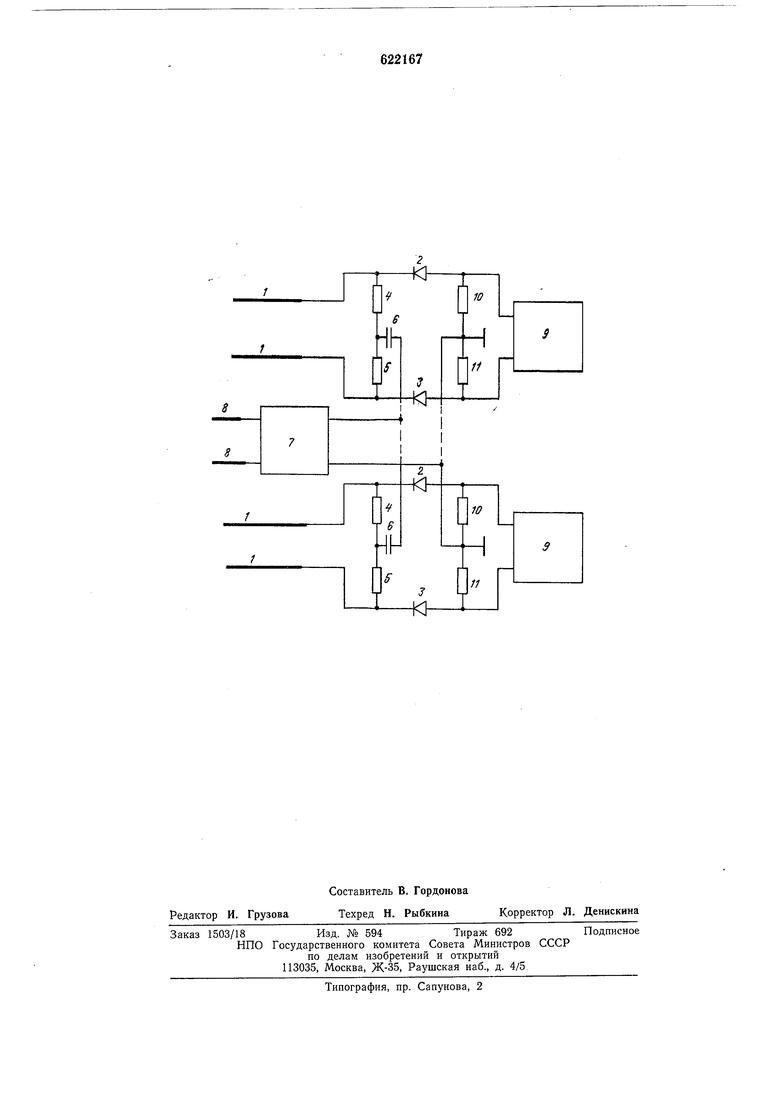

Изобретение относится к вычислительной технике и предназначено для использования в магнитных запоминающих устройствах (ЗУ). Известны схемы запоминающих устройств, блоков стробирования и усилителей воспроизведения, в которых решены в той или иной степени вопросы улучшения различных характеристик ЗУ, в частности вопросы повышения помехозащищенности и информационной надежности 1. Однако указанные устройства не позволяют осуществить воспроизведение сигналов, близкое к оптимальному, так как в них введено только плавающее стробирование, что снижает помехозащищенность ЗУ и его информационную надежность. Наиболее близким к предложенному является устройство, содержащее в каждом разряде нелинейные элементы, включенные между разрядно-считывающими шинами и соответствующими входами усилителей воспроизведения, эталонный усилитель воспроизведения, вход которого подключен к эталонной разрядно-считывающей шине, и шину нулевого потенциала 2J. В данном устройстве отсутствует подавление квазидетерминированных синфазных и дифференциальных помех, а также случайных помех, поступающих из разрядносчитывающих щин. Цель изобретения - повышение надежности ЗУ. Поставленная цель достигается тем, что блок содержит в каждом разряде элемент развязки и два делителя напряжения, первый из которых включен между разрядносчитывающими шинами, средняя точка первого делителя напряжения через элемент развязки подключена к первому входу эталонного усилителя воспроизведения, второй вход которого соединен с шиной нулевого потенциала, второй делитель напряжения включен между входами усилителя воспроизведения, а его средняя точка соединена с вторым входом эталонного усилителя воспроизведения. Схема блока воспроизведения информации для запоминающего устройства представлена на чертеже. Она содержит разрядно-считывающие шины 1, соединенные с нелинейными элементами 2 и 3 и первым делителем напряжения на резисторах 4 н 5, средняя точка которых подключена к элементу развязки на конденсаторе 6, подсоединенному другим концом к эталонному усилителю 7 воспроизведения. Входы усилителя 7 подключены к эталонной разрядно-считывающей

Шине S. Катоды нелинейных элементов 2 и 3 подсоединены к входам усилителя 9 воспроизведения и второму делителю напряжения на резисторах 10 и 11, средняя точка которых подключена к шиНе нулевого потенциала н второму выходу эталонного усилителя воспроизведения.

При считывании сигнал вместе с помехой поступает с разрядно-считывающей шины 1 на нелинейные (квадратичные) элементы 2 и 3 и резисторы 4 и 5 первого делителя напряжения, в среднюю точку которого в момент считывания через конденсатор 6 подается эталонный сигнал (сигнал одинаковой формы, что и информационный) усиленный на эталонном усилителе 7 воспроизведения.

Введение в блок воспроизведения информации для запоминаюидего устройства двух делителей напрялсения позволяет организовать воспроизведение сигиала чтения, близкое к оптимальному, так как передаточная функция блока онределяется эталонным сигналом, т. е. на входе усилителя воспроизведения при квадратичных преобразованиях оказывается сигнал, который математически можно представить в следующем виде:

U(t)K-U,(t}-U,(t),

где /С - коэффициент передачи, зависящий от параметров нелинейных элементов и резисторных цепочек;

/э(0 -эталонный сигнал;

и с (t) - сигиал чтения.

С учетом входной емкости усилителя воспроизведения или специально введенной емкости на входе усилителя воспроизведения образуется сигнал корреляции. Согласно теории потенциальной помехоустойчивости такие устройства имеют оптимальные характеристики помехозащищенности.

Помехозащищенность и информацнонная надежность в предлагаемом блоке повыщена за счет организации плавающего стробирования, которую позволяют осуществить введенные резисторные цепочки я конденсатор. Временная селекция обеспечивается с помощью автоматического смещения эталонного сигнала, являющегося одновременно стробирующим сигнадом, в соответствия с задержкой информационного сигнала в разрядно-считывающей Щине в зависимости от геометрического местоположения

данного запоминающего элемента в накопителе. При считывании сигнал с эталонной разрядно-считывающей щины всегда имеет одинаковую задержку распространения, что и информационный сигнал. Это создает равные условия воспроизведения всех информационных сигналов.

Введение конденсатора преследует цель разделения по постоянной составляющей напряжения разрядно-считывающей щины

эталонного усилителя воснроизведения, что обеспечивает стабильность режима работы нелинейных элементов.

Формула изобретения

Блок воспроизведения информации для запоминающего устройства, содержащий в каждом разряде нелинейные элементы, включенные между разрядно-считывающими щинами и соответствующими входами усилителей воспроизведения, эталонный усилитель воспроизведения, вход которого подключен к эталонной разрядно-считывающей щине, и щину нулевого потенциала,

отличающийся тем, что, с целью повышения надежности блока, он содержит в каждом разряде элемент развязки и два делителя напряжения, первый из которых включен между разрядно-считывающими

щинами, средняя точка первого делителя напряжения через элемент развязки подключена к первому входу эталонного усилителя воспроизведения, вход которого соединен с щиной нулевого потенциала, второй делитель напряжения включен между входами усилителя воспроизведения, а его средняя точка соединена с вторым входом эталонного усилителя воспроизведения.

Источннки информации,

нринятые во внимание при экспертизе

1.Авторское свндетельство СССР № 410454, кл. G НС 7/02, 1974.

2.Авторское свидетельство СССР № 448479, кл. G ПС 7/00, 1974.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1978 |

|

SU781971A1 |

| Блок воспроизведения для запоминающего устройства | 1980 |

|

SU902070A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Устройство для считывания информации из накопителя | 1980 |

|

SU864334A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU315211A1 |

| Запоминающее устройство | 1985 |

|

SU1317481A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020749C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО СРАВНЕНИЯ | 1991 |

|

RU2019031C1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ ПОРАЗРЯДНОГО СРАВНЕНИЯ | 1991 |

|

RU2020750C1 |

Авторы

Даты

1978-08-30—Публикация

1976-12-30—Подача