Изобретение относится к области вычислительной техники.

Известны устройства считывания информации из ЗУ, содержащие по два канала усилителей считьюания, логические схемы сравнения результатов считывания по двум Каналам и устройства коррекции одиночных ошибок в неисправных разрядах при несовпадении контрольной суммы с результатом свертки по модулю два l.

Наиболее близким к изобретению является устройство, содержащее элемент согласования, выполненный на первом трансформаторе, формирователь разрядного тэка записи, два усилителя считывания, два триггера числа, первый и второй элементы И, выходы которых через элемент ИЛИ и инвертор соединены со входом триггера фиксации отказа, выходы которого соединены с одними входами третьего и четвертого элементов И, другие ВлОды которых соединены соответственно с выходом одного триггера числа и с шиной сигнала несовпадения, а выходы третьего и четвертого

элементов И соединены через пятый элемент И с шиной вывода числа 2.

Целью изобретения является повышение надежности устройства.

Поставленная цель дэсти ается тем, что предложенное устройство содержит шестой и седьмой элементы И и дополнительный элемент согласования, выполненный на втором трансформаторе, первичная обмотка которого соединена со средней точкой вторичной обмотки первого трансформатора, вторичные обмотки которого сэелинены с одними входами шестого и седьмого элементов И, доугие входы которых соединет1ы с выходом устройства, а третьи входы - с выходами другого триггера числа. Выходы ujGCTorj и седьмого элемет1тов И соединены сэ входами элемента ИЛИ.

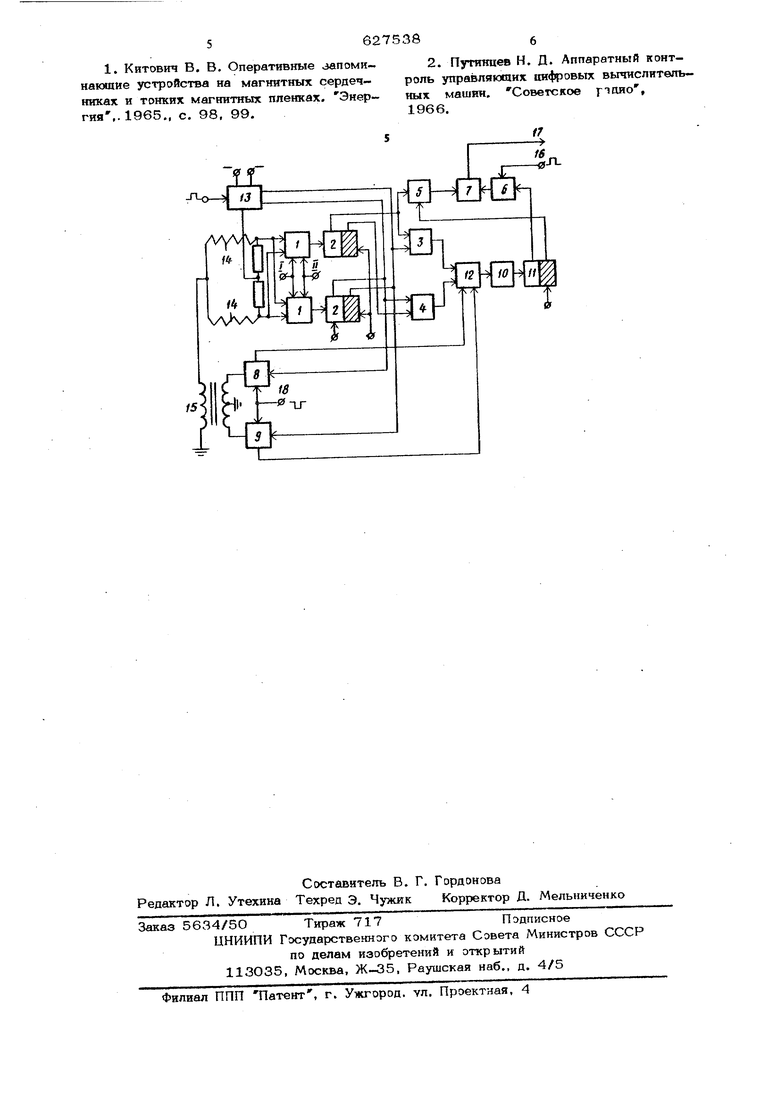

На чертеже приведена функциональная схема устройства для считывания информации одного разряда ОЗУ для случая применения элементов резисторно-транзистэрнтй логики. 36 Устройство содержит два усилителя считывания 1, два триггера числа 2, элементы И 3 9, шгоертор Ю, триг гер ({)иксации отказа11, элемент ИЛИ 12, формирователь разрядного тока запи си 13, элемент согласования на первом трансформаторе 14, дополнительный элемент согласования на трансформаторе 15,шину сигнала несовпадения 16 и ши ну вывода числа 17, Устройство работает следующим образом, При исправных усилителях считывания 1 со стробированием на выходах три гера числа 2 устанавливается одинаковая информация, а на выходах элементов И 3 и 4 такой сигнал, который при прохож деш1И через элемент ИЛИ 12 и инвертор 1О не вызовет срабатывание триггера 11, поэтому информация с выхода однО го из триггеров 2 черва элементы И 5 7 поступает на выход 18 устройства и далее в арифметическое устройство. Одновременно производится регенерация сч танной или запись новой информации с помощью формирователя разрядного тока записи 13 в соответствии с состоянием другого триггера числа 2, При протекании тока записи через обмотки трансформаторов 15 и 14 на входах элементов И 8 и 9,наводятся импульсы противоположной полярности. Если полярность каждого из этих импульсов соответствует сигналам, снимаемым с плеч триггера 2, а длительность соответствует длительности импульса контроля, что характеризует исправную работу канала записи то триггер 11 в момент записи также остается в исходном состоянии. При неисправности одного из каналов выделения информации или схем записи сигналы в элементах И 8, 9, 3 или 4 не совпадают, что приводит к срабатьгеа- нию триггера 11, При этом выход неисправного разряда блокируется элементом И 5, на оба входа элемента И 6 подаются одинаковые сигналы от левого плеча триггера 11 в состоянии отказа и от шины 16 до получения результатов сверки по модулю 2, На выходе эле лента 6 устанавливается янал, обеспечивающий нулевой потенциал на шине 17, Если после выполнения оперйции свертки помо дуяю 2 не произойдет несовпадение ре- эу71ьтатов сверки с : информацией, хранящейся в контрольном разряде, та сигнал О на шине вьтвода числа 17 можно считать истинным. Если на выходе элемента И 6 в результате контроля по модулю 2 появятся сигнал несовпадения, 8 ТО на шине 17 S результате срабатывания элементов И 6 и V информация меняется на обратную (1), т.е. корректируется одиночная ошибка. Сигнал отказа с триггера 11 подает::я Б арифметическое устройство ЭВМ, которое программными методами проводит анализ ОЗУ на выявление случайного сбоя или постоянного отказа в цепях записи-считывания и в случае постоянного отказа в одном из разрядов запрещает сброс триггера 11 неисправного разряда. Предложенное устройство кроме реше msi основной задачи - повышения надежности фугасционирования ЗУ - в ряде случаев позволяет повысить быстродействие ЭВМ, так как наптие контроля по каждому разряду позволяет исключить необходимость в выполнении операций контроля по модулю 2 при каждом обращении к ЗУ и проводить ее только при наличии отказа в одном из разрядов. Формула изобретения Устройство для считывания информации из блоков оперативной памяти, содержащее элемент согласования, выполненный на первом трансформаторе, формирователь разрядного тока записи, два усилителя считывания, два триггера числа, первый и второй элементы И, выходы которых через элемент ИЛИ и инвертор соединены со входом Триггера фиксации отказа, выходы которого соединены с одними входами третьего и четвертого элементов И, дру1-ие входы которых соединены соответственно с выходом одного триггера числа и с шиной сигнала несовпадения, а выходы третьего и четвертого элементов И соединены через пятый элемент И с шиной вывода числа, отличающее - с я тем, что, с целью повышения надежности устройства, оно содержит шестой и седьмой элементы И и дополнительный элемент согласования, выполненный на втором трансформаторе, первичная обмотка которого соединена со средней точкой, вторичной обмотки первого, трансформатора, вторичные обмотки которого соединены с одними входами шестого и седьмого элементов И, другие входы которых соединены с выходом устройства, а трегьи входы - с выходами другого триггера числа; выходы шестого и седьмого элементов И соединены со входами элемента ИЛИ. Источники информации, приш1тые во внимание при экспертизе:

56275386

1. Китович В. В. Оперативные запоми 2. Путияцев Н. Д. Аппаратный контнаюшие устройства на магнитных сердеч- роль управляюганх цифровых вычислитель- никах и тонких магнитных пленках, Энер- ных машин. Советское .

гия,.1965., с. 98, 99.

г

I

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство типа @ с обнаружением и исправлением ошибок | 1981 |

|

SU999114A1 |

| Запоминающее устройство с обнаружением отказавших блоков | 1980 |

|

SU903974A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU386442A1 |

| Оперативное запоминающее устройство с блокировкой неисправных ячеек памяти | 1981 |

|

SU1014033A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для имитации отказов и сбоев ЭВМ | 1987 |

|

SU1564628A1 |

| Устройство для сопряжения цифровой вычислительной машины (ЦВМ) с абонентами | 1984 |

|

SU1234843A1 |

| Резервированное запоминающее устройство | 1986 |

|

SU1417041A1 |

| Запоминающее устройство с автономным контролем | 1983 |

|

SU1100640A1 |

Авторы

Даты

1978-10-05—Публикация

1971-05-24—Подача