(54) НАКАПЛИВАЮЩИЙ СУММАТОР

мого сумматора содержит два элемента НЕ и, третий элемент И,, причем выходы первого и второго элементов И подключены к входам первого элемента ИЛИ, первый вход первого элемента И подключен к выходу второго элемента ИЛИ а второй вход но второй управляющей шине, первырт вход второго элемента И подключен к входу знакового разряда, который через первый элемент НЕ под-, ключей к первому экоду третьего эле мента Hj второй вход которого подключаи к входу элемента задержки, который через второй элемент НЕ подключен к второму вколу второго элемента И, третьи входы второго и третьего элементов И подключены соответственно к нулевому и единичному выходам счетного триггера знакового разряда., а четвертые акоды - к третьей управляющей шине, выход третьего зле 1енХа И подключен к иулезому установочному входу счетного триггера.

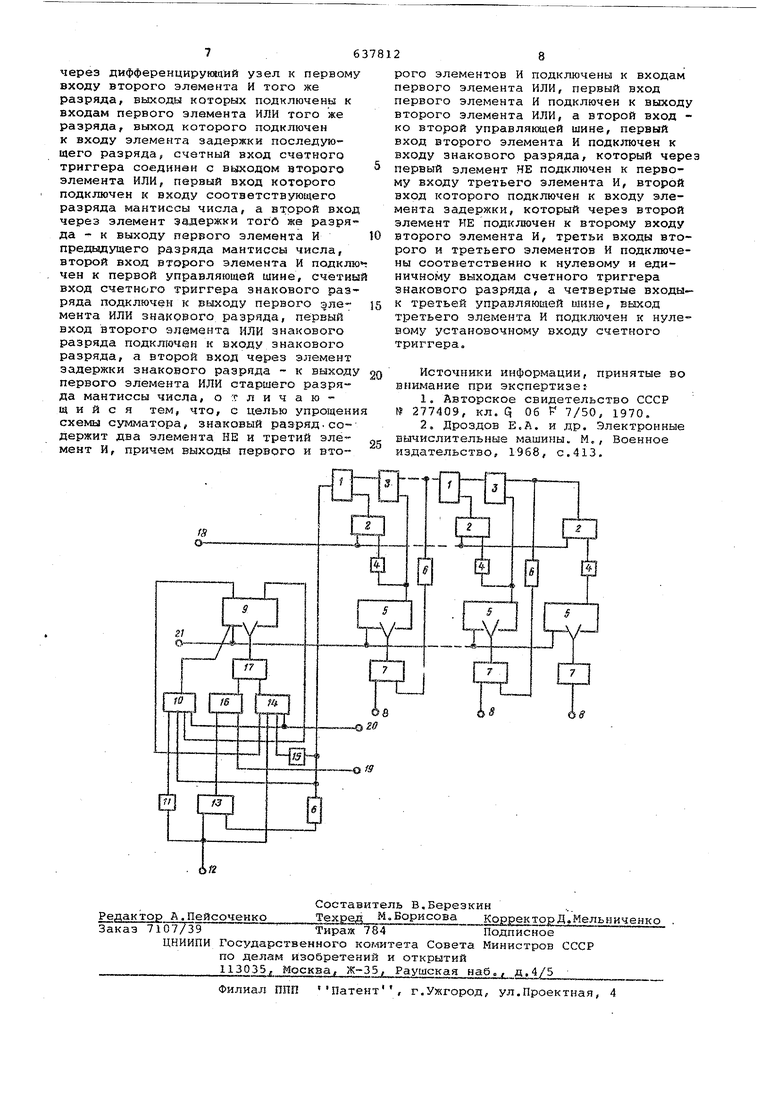

На чертеже представлена функциональная схема описываемого сумматора. Накапливающий сумматор содержит в каждом разряде мантиссы чкспв. элемент ИЛИ 1 и подключенные к его входам эле менты И 2 и 3, первый из которых чере дифференцируюо нй узел 4, а второй iieпосредственн.оподключены к единичному выходу счетного триггера 5 своего раз ряда. Выход; элемента ИЛ14 1 ка кдо1о разряда, мантиссы числа подключен чере элемент 6 задержки к входу элемента ИЛИ 7 пос.ле/7уюше,го разряда мантиссы числа. Счетный вход триггера 5 са;кдог разряда мантиссы числа соединен с выходом элемента ИЛИ 7 своего разряда, другой вход .которого подяключен к вход 8 соответствующего разряда мантиссы числа,

В знаковом разряде сумматор содержит счетный триггер 9, элемено: И 10, элемент НЕ .11 вход 12 знакового разряда, .элемент ИЛИ 13, элемент И 14 элемент НЕ 15. элемент И 16 и элемент ИЛ1Г 17. На первую упра.вляющую шину I поступают стррбирующие импульсы,- на вторую управляющую шину 19 - сигнал признака кода, на третью управляющую шину 20 - сигнал признака числа.

К нулевому установочному входу счетного триггера 9 подключен выход, элемента И 10,первый вход которого че реэ элемент НЕ 11 подключен к входу L знакового разряда, к входу элемента ИЛИ 13 и к входу элемента И.14,другой вход которого через элемент НЕ 15 подключен к входу элемента И 10 и к вход элемента б згадержки. Выход элемента 6 задержки подключен к входу элемента ИЛИ 13, выход которого подключен к входу элемента И 16., другой вход которого подключен ко второй управляющей шине 19, а выход-к входу элемента ИЛИ 17, другой вход которого подключен к выходу элемента И 14. Выход элемента ИЛИ 17 подключен к счетному входу

счетного триггера 9, нулевой выход которого подключен к входу элер 1ента И 14, а единичный выход к входу элемента И 10, другой вход которого подключен к входу элемента И 14 и к третьей управляющей шине 20, Стробируьшцие входы элементов И 2 подключены к первой управляющей шине 18.

Иакапливаюш.ий суг шатор для сквозного переноса работает следующим обраэом.

Исходное состояние всех триггеров 5 и триггера 9 нулевое„ При работе с кодами триггер 9 (модифицированного знакового разряда) работает как младший знаковый разряд, а при работе с числами как старший знаковый разряд, Рассглотрим работу модифицированногО знакового разряда сумглатора с чгюлами на конкретных примерах.

Отсутствие Признак кода на входе элемента И 16 запрещает формирование сигнала записи на входе элемента ИЛИ. 17.

Предположим, что в счетных триггерах 5 и 9 суш-SaTopa записано число О, О,,,,,,.,Of что соответствует исходному состоянию. На входах 8 и 12 разрядов присутствует число О, 10... ..О, При вводе знакового разряда второго слагаемого и отсутствии переноса из предыдущего разряда комбинационная часть cxeMi j, принадлежащая модифидкрованному знаковому разряду, не изменяет состояния и соответствует исходному.

На счетных триггерах 5 и 9 сумматора записан код О, 10 ,..,10, а на входах 8 и 12 разрядо.в присутствует число О, 10,.....о,10, Bь:paбaтьraae 5Ый при этом перенос в знаковый разряд поступает на вход элемента И 10, чере элемент НЕ 15 на вход элемента И 14 и через элемент 6 задержки на вход элемен1а ИЛИ 13.Прохождение сигналаперенос через элемент И Ю запрещается сигналом с единичного выхода счетного триггера 9. Счетный триггер 9 находится в нулевом состоянии.

Если на счетных триггерах 5 и 9 сумматора записан код 0,0 ,,,оО, а на входах 8 и 12 разрядов присутствует число 1,1.....,, то в счетный триггер 9 через элемент ИЛИ 17 с выхода элемента И 14 записывается , так как происходит совпадение сигналов признака числа, разрешающего сигнала с нулевого выхода счетного триггера 9 наличия единичного кола на входе знакового разряда и сигнала с выхода элемента НЕ 15, на входе которого от( сутствует сигнал переноса.

На счетных, триггерах 5 и 9 cyivw-iaTop записан код 1, 010 ,..,0, а на входах 8 и 12 разрядов присутствует число О, 1010...,01, Отсутствие сигнала Перенос на входе элемента И 10, единичного кода с входа 12 знакового разряда на входе элемента И 14 и разрешающего с нала с нулевого выхода счетного триг гера 9 запрещает изменить состояние счетного триггера 9. На счетных триггерах 5 и 9 записа код О, 11....о.,.,..1, а на входах 8 и 12 разрядов присутствует число 1,11. В рассматриваемом примере состояние счетного триггера 9 не изменится Наличие инвертированного сигнала переноса на входе элемента И 14 запренала с входа 12 знакового разряда на вход элемента ИЛИ 17 для перевода счетного триггера 9 из нулевого состояния в единичное. Прохождение сигнала переноса чере элемент И 10 запрещается сигналом с единичного выхода счетного триггера и инвертированньм сигналом с входа 1 знакового разряда. На счетных триггерах 5 и 9 сумматора записан код 1, 11, а на входах 8 и 12 разрядов присутствует число 0,11. Присутствие на входах элемента И 10 сигнала переноса, разрешающего си нала с единичного выхода счетного триггера 9, инвертированного сигнала с входа 12 знакового разряда шины фо мирует сигнал на выходе элемента И 1 по которому счетный триггер 9 устанавливается в нулевое состояние. Fla счетных триггерах 5 и 9 сумматора записан код 1, 010....1, а на входах 8 и 12 разрядов присутствует число 1, 10...0. На входы элемента И 10 поступают сигналы, запрещающие на его выходе формирование сигналов для сброса счетного триггера 9 в нулевое состояние. С нулевого вьлхода счетног триггера 9 поступает сигнал, запрещающий прохождение единичного кода с входа 12 знакового разряда на счетный вход триггера 9. Счетный триггер 9 не изменяет единичного состояния. 1а счетных триггерах 5 и 9 сумма..1 тора записан код 1, 11... а на входах 8 и 1, 12 разрядов присут111. Сформиствует число

ровать сигнал для установки из единичного Б нулевое состояние, счетного триггера 9 элементу И 10 запрещает инвертированный сигнал с входа 12 знакового разряда.

Прохождение единичного кода на счетный вход счетного триггера 9 для установки его в нулевое состояние через элемент И 14 запрещается сигналом, поступающим на вход элемента И 14 с нулевого выхода счетного триггера 9,

Формула изобретения

Накапливающий сумматор, каждый разряд мантиссы числа которого содержит счетный триггер, дифференцирую-v щий узел, элемент задержки, два элемента И и два элемента ИЛИ, а знаковый разряд содержит счетный триггер, элемент задержки, два элемента И и два элемента ИЛИ, причем в каждом разряде мантиссы числа единичный выход счетного триггера подключен к первому входу первого элемента- И и Инвертированный сигнал переноса также является сигналом запрета длч прохождения единичной информации с входа 12 знакового разряда через элемент И 14 на счетный вход счетного триггера 9. При работе накапливающего сумматора с кодами на входы элемента И 10 и элемента И 14 по второй управляющей шине 19 подается сигнал запрета. Любая комбинация сигналов, получаемая при работе накапливающего сумматора с кодами, не формирует на выходах элемента И 10 и элемента И 14 сигналов, изменяющих состояние счетного триггера 9. Единичный сигнал, присутствующий на входе 12 знакового разряда при отсутствии сигнала переноса, поступает через элемент ИЛИ 17 на счетный вход счетного триггера 9 и изменяет его состояние. Если при вводе в сумматор счетного слагаемого формируется перенос в знаковый разряд при отсутствии единичного сигнала на входе 12 знакового разряда, то пришедший перенос также не изменяет состояния счетного триггера 9 на противоположный. Предположим, что в счетных триггерах 5 и 9 сумматора записано число 1, 11, к которому прибавляется второе слагаемое 1,11. При этом вырабатывается перенос в знаковый разряд. Единичный сигнал,пришедший с входа 12 знакового разряда, перебрасывает счетный триггер 9 из единичного состояния в нулевое, а задержанный сигнал переноса устанавливает его в единичное состояние, т.е. счетный триггер 9 не изменяет своего единичного состояния после окончания процесса суммирования. Таким образом, предлагаемый сумматор по сравнению с прототипом позволяет получить на одном триггере истинное значение знакового разряда при работе с числами или необходимое значение при работе с кодами. Исключение из знакового разряда одного триггера, элемента ИЛИ, элемента задержки и дифференцирующего узла упрощает схему сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое интегрирующее устройство | 1985 |

|

SU1275483A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для выравнивания порядков чисел | 1982 |

|

SU1030798A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU429423A1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления чисел | 1981 |

|

SU1012241A1 |

| Устройство для выбора среднего по величине числа | 1981 |

|

SU1005336A1 |

Авторы

Даты

1978-12-15—Публикация

1976-06-07—Подача