памяти, первый и второй выходы которого соединены соответственно с первыми входами первого и второго интеграторов, третий выход блока управления подключен к третьим входам первого и второго и второму входу третьего блока памяти, четвертый и пятый выходы блока управления соединены соответственно с первым входом четвертого и первыми входами пятого блоков памяти, первый выход последнего из которых подключен к второму входу четвертого блока памяти, выход которого соединен со вторым входом аналого-цифрового преобразователя, пятый выход первого блока памяти подключен к второму входу первого интегратора, третий вход которого соединен с первым входом третьего блока памяти, выход подключен через блок вычисления экспоненты к первому входу шестого блока памяти и к третьему входу блока управления, второй выход третьего и шестой выход первого блока памяти соединены соответственно со вторым и третьим входами второго интегратора, седьмой выход первого блока памяти подключен к второму входу пятого блока памяти, второй выход которого и выход седьмого блока памяти соединены со входами сумматора, выход которого подключен к третьему входу пятого блока памяти и к четвертым входам блока управления и второго интегратора, выход которого через второй блок вычисления экспоненты соединен с первым входом второго блока сравнения, восьмой выход первого блока памяти через второй блок вычисления коэффициентов подключен к пятому входу блока управления и к первому входу блока деления, выход которого соединен со вторым входом второго блока сравнения и с шеетым входом блока управления, пятый выход которого подключен к второму входу шестого блока памяти, выход которого соединен со вторым входом блока деления, первый и второй выходы второго блока сравнения подключены к седьмому и восьмому входам блока управления, шестой выход которого соединен со входом блока опроса датчиков.

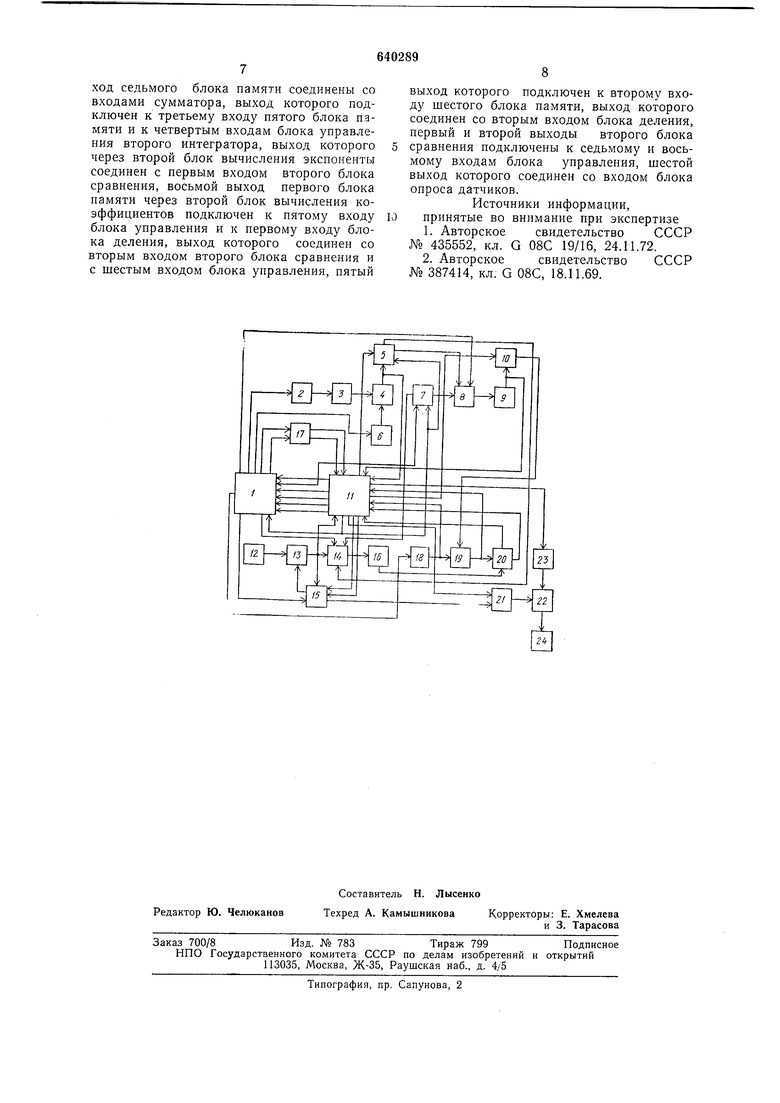

На чертеже представлена блок-схема предлагаемого устройства.

Оно содержит первый блок памяти 1, блок выделения аргумента 2, блок логарифмирования 3, блок умножения 4, второй блок памяти 5, первый блок выделения коэффициентов 6, третий блок памяти 7, первый интегратор 8, блок вычисления экспоненты 9, шестой блок памяти 10, блок управления И, седьмой блок памяти 12, сумматор 13, второй интегратор 14, пятый блок памяти 15, блок вычисления экспоненты 16, первый блок сравнения 17, второй блок вычисления коэффициентов 18, блок деления 19, второй блок сравнения 20, четвертый блок памяти 21, аналого-цифровой преобразователь (АЦП) 22, блок опроса датчиков 23, выходной блок 24.

Устройство работает следующим образом.

Из блока памяти 1, в котором содержатся численные значения функции погрешности на всем диапазоне изменения замеренных сигналов, величина диапазона (xi х), число узлов информационной сетки - 32, последовательности натуральных чисел от 1 до 32, константа 0,5 поступают значения Xi, Xz, Л(х} в блок 2, значения Xi, х. в блок 6 и значения х в блок 15. В блоке 6

рассчитывается значение и там же

Xi

запоминается, в блоке 2 вычисляется значение . , , оно поступает в блок 3 и

Д()

х - х

1п| там вычисляется значение

AW

которое поступает в блок 4, в котором оно умножается на . Одновременно с

.«2 Xi

1

X - KI

передачей значения-In

в

х - х I Д (Jc) блок 5, оно поступает в блок 11, после чего управляющий сигнал из блока И поступает в блок 1, а из блока 1 на вход блока 17 поступает текущее значение А(%) и 0. Если Д(л:)0, то идет вычисление и запоминание следующего численного значения подынтегральной функции для нового значения А(д;), в противном случае блок 11 управляющим импульсом воздействует на блоки 1, 5, 7 так, что при этом из блока 1 на вход интегратора 8 поступают значения нижнего и верхнего предела интегрирования ;Ci и x-i соответственно, из блока 5 - значение подынтегральных функций, из блока 7 - значение приращений к аргументам.

Вычисленное в блоке 8 значение интеграла

1

.2 -

dx

1п

ДМ у

Хг - Х

поступает в блок 9, где вычисляется значение

/ -i-In V-,

J Д(.ДГ)

это значение запоминается в блоке 10 и одновременно оно отправляется в блок 11, управляющий сигнал которого воздействует на блок 1 таким образом, что из него в блок 18 поступают первый член натуральной совокупности (1-32), константы 32 и 0,5 и блок 18 рассчитывает значение

32

г , которое поступает в блок 19 и в

1

блок и, который управляющим импульсом

воздействует на блок 10 и значение эффективной точности поступает на второй вход блока 19, с выхода которого значение g(l-0,5)/32 поступает на вход блока 20 и блок 11, который управляющим импульсом воздействует на блок 15 таким образом, что из блока 15 поступает значение нижнего предела интегрирования Xi на вход блока 13, на второй вход которого постоянно подается маленькое положительное приращение S, размер которого имеет величину

порядка --- . В блоке 13 значения Xi

О

и б суммируются и результат запоминается в блоке 15 вместо старого значения Xi, а также поступает на вход интегратора 14 и на вход блока И, который посылает управляющие импульсы в блоки 1, 5, 7, при этом из блока 1 на вход интегратора 14 поступает значение х, из блока 5 - значение подынтегральной функции, из блока 7 - значения приращения аргумента Ах. Вычисленные значения интеграла поступают в блок 16, где рассчитывается

УЗ

Ini

dx. Д(л)

Xz-Xi

Это значение поступает на второй вход блока сравнения 20, если это значение больше или равно, чем сигнал, поданный на первый вход блока сравнения 20, то в блок 11 поступает сигнал, согласно которому блок 11 посылает управляющие импульсы в блок 1 и в блок 15. При этом из блока 15 значение верхнего предела интеграла пересылается в блок 21, а из блока 1 на оба входа блока 17 подаются значения текущего члена натуральной последовательности (1-32) и константа 32.

Если они совпадают, то блок 11 двумя управляющими импульсами воздействует на блоки 21 и 23 и при этом рассчитанные параметры пересылаются в АЦП 22, а из блока 23 поступают сигналы с датчиков измерений. Эти сигналы кодируются и засылаются в блок выхода 24. Если же сигналы, поданные на вход сравнения 17, не совпали, то блок 11 управляющим сигналом воздействует на блок 1 так, что с выхода его на вход блока 18 поступает следующее значение натуральной последовательности и начинается этап расчета следующего параметра информационной сетки.

Если на выходе блока 20 оказалось, что сигнал от блока 16 меньще сигнала от блока 19, то блок И управляющим импульсом так воздействует на блок 15, что хранящееся там значение верхнего предела интегрирования поступает на вход блока 13 и повторяется этап вычисления нового значения эффективности точности g(y) уже на несколько увеличенном отрезке, i, е. для

Z/ г/пред + б.

В устройстве для сжатия данных высокая точность сжатия достигается при длине кода, равной 8 бит, в предлагаемом - при длине кода, равной 5 бит, что на 37,5% экономит объем запоминающего устройства.

Формула изобретения

Устройство для сжатия данных, содержащее блок управления, первые выходы которого подключены к первым входам первого блока памяти, выход блока опроса датчиков соединен с первым входом аналого-цифрового преобразователя, выход которого подключен к входу выходного блока, блоки памяти и блоки сравнения, отличающееся тем, что, с целью расщирения функциональных возможностей устройства, в него введены блок выделения

аргумента, блоки вычисления коэффициентов, блок логарифмирования, интеграторы, блоки суммирования, блок деления, блоки вычисления экспоненты и блок умножения, первый выход первого блока памяти через

последовательно соединенные блок выделения аргумента и блок логарифмирования подключен к первому входу блока умножения, к второму входу которого через первый блок вычисления коэффициентов подключен второй выход первого блока памяти, третий и четвертый выходы которого через первый блок сравнения соединены с первыми входами блока управления, второй выход которого соединен со вторым

входом первого блока памяти и с первыми входами второго и третьего блоков памяти, выход блока умножения подключен к второму входу блока управления и со вторым входом второго блока памяти, первый

и второй выходы которого соединены соответственно с первыми входами первого и второго интеграторов, третий выход блока управления подключен к третьим входам первого и второго и второму входу третьего

блоков памяти, четвертый и пятый выходы блока управления соединены соответственно с первым входом четвертого и первыми входами пятого блоков памяти, первый выход последнего из которых подключен к

второму входу четвертого блока памяти, выход которого соединен со вторым входом аналого-цифрового преобразователя, пятый выход первого блока памяти подключен к второму входу первого интегратора, третий

вход которого соединен с первым входом третьего блока памяти, выход подключен через первый блок вычисления экспоненты к первому входу щестого блока памяти и к третьему входу блока управления, второй выход третьего и щестой выход первого блока памяти соединены соответственно со вторым и третьим входами второго интегратора, седьмой выход первого блока памяти подключен к второму входу пятого

блока памяти, второй выход которого и выход седьмого блока памяти соединены со входами сумматора, выход которого подключен к третьему входу пятого блока памяти и к четвертым входам блока управления второго интегратора, выход которого через второй блок вычисления экспоненты соединен с первым входом второго блока сравнения, восьмой выход первого блока памяти через второй блок вычисления коэффициентов подключен к пятому входу блока управления и к первому входу блока деления, выход которого соединен со вторым входом второго блока сравнения и с шестым входом блока управления, пятый

выход которого подключен к второму входу шестого блока памяти, выход которого соединен со вторым входом блока деления, первый и второй выходы второго блока

сравнения подключены к седьмому и восьмому входам блока управления, шестой выход которого соединен со входом блока опроса датчиков.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 435552, кл. G 08С 19/16, 24.11.72.

2.Авторское свидетельство СССР № 387414, кл. G 08С, 18.11.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU736130A1 |

| Цифровой интегратор для воспроизведения многомерных функций | 1974 |

|

SU519736A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Система оптимального управления с моделью объектами второго порядка | 1980 |

|

SU888071A1 |

| Устройство для моделирования адаптивного нейрона | 1977 |

|

SU708369A1 |

| Устройство для моделирования удара тела о неподвижную преграду | 1985 |

|

SU1381341A1 |

| Интегрирующее устройство интегрирующей машины последовательного типа | 1974 |

|

SU526927A1 |

| Устройство для контроля параметров конвертерного процесса | 1985 |

|

SU1308633A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

Авторы

Даты

1978-12-30—Публикация

1977-01-24—Подача