1

Изобретение относится к запоминающим устройствам.

Известны запоминающие устройства с самоконтролем.

Одно из известных устройств содержит накопитель, регистр адреса, регистр слова, блоки кодирования и декодирования . Это устройство характеризуется сложностью реализации блоков кодирования и декодирования.

Из известных устройств наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к регистру адреса и регистру слова; соединенного с блоком контроля и блоком кодирования, и блок шравления 2.

Однако в этом запоминающем устройстве требуются большие аппаратурные затраты на реализацию блока кодирования, а также большое число дополнительных разрядов в накопителе для записи контрольных разрядов корректирующего кода.

Целью изобретения является упрощение конструкции и 1повышение информационной емкости устройства. Поставленная цель достигается тем, что устройство содержит регистр отказов и элементы И, входы которых подключены к выходам регистра слова и блока управления, а выходы - к выходам устройства, входы регистра отказов соединены с выходами блока управления, а выходы - со входами регистра слова.

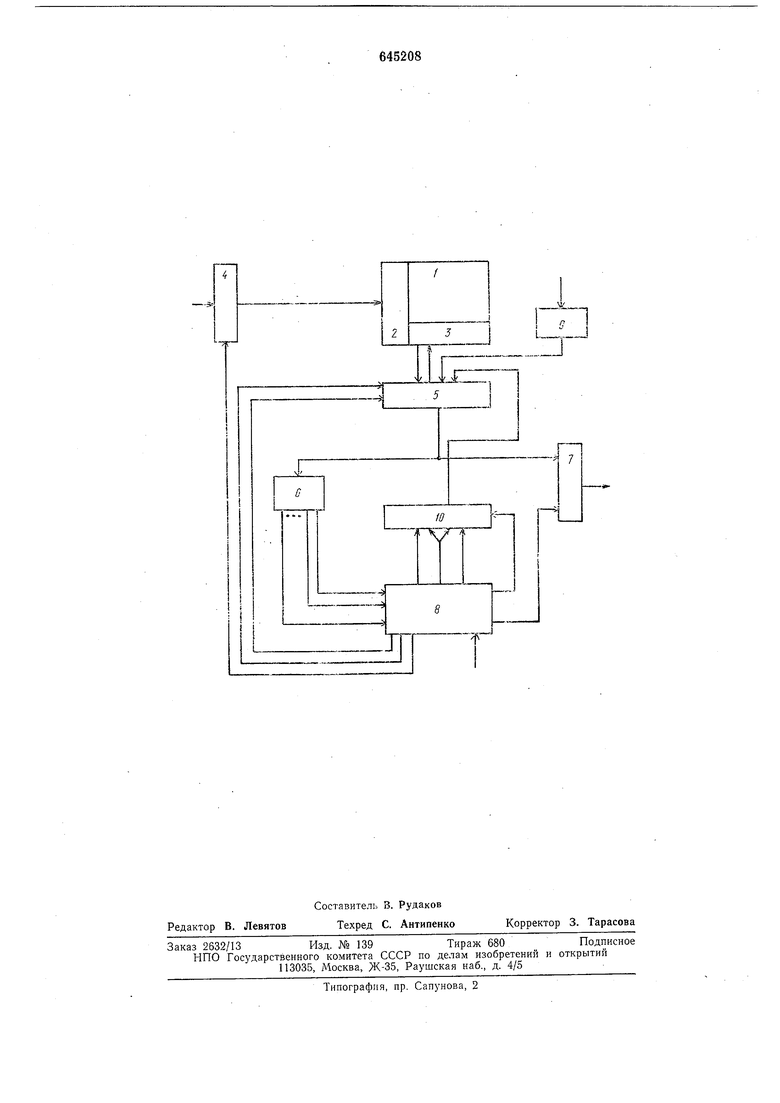

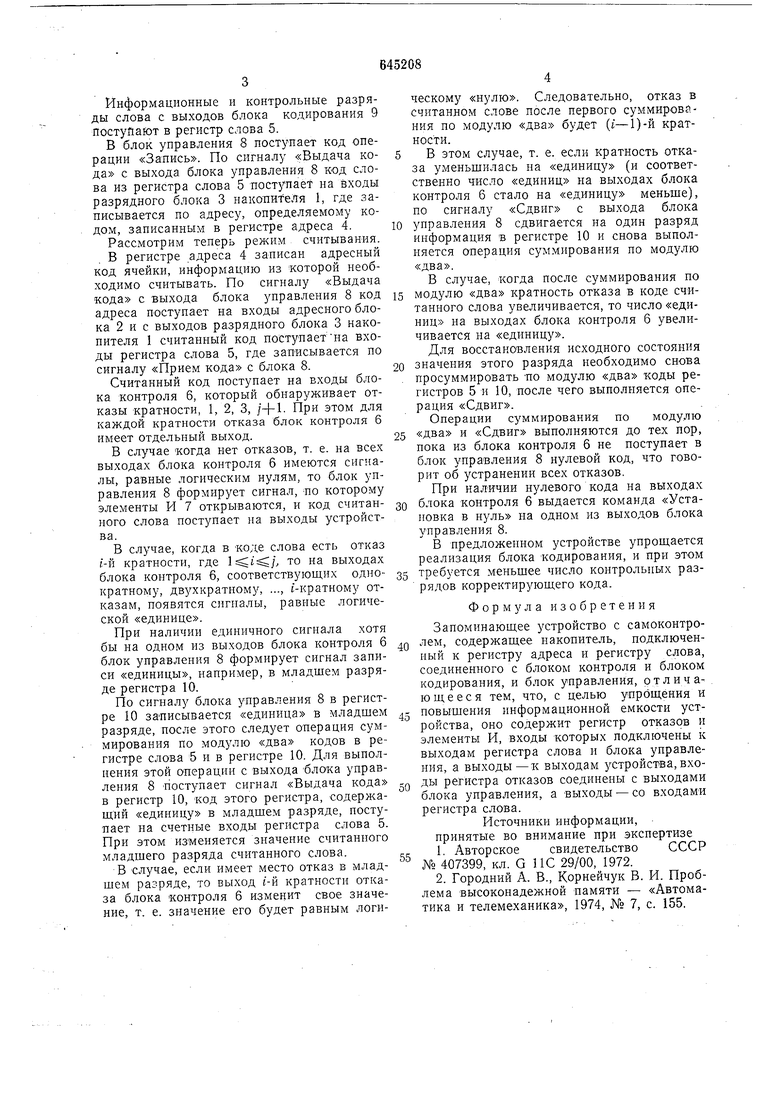

На чертеже изображена блок-схема предложенного устройства.

Устройство содержит накопитель 1, в состав которого входят адресный 2 и разрядный 3 блоки. Устройство также содержит регистр адреса 4, регистр слова 5, блок контроля 6, элементы И 7, блок управления 8, блок кодирования 9 и регистр отказов 10. Входы элементов И 7 подключены к выходам регистра 5 и блока 8, а выходы - к выходам устройства. Входы регистра 10 соединены с выходами блока 8, а выходы - со входами регистра 5.

Предложенное устройство работает следующим образом.

Рассмотрим режим записи. В регистре

адреса 4 записан адресный код ячейки, в

которую необходимо записать код слова,

поступающий на входы блока кодирования 9.

В блоке кодирования 9 формируются контрольные разряды, при помощи которых обнаруживаются отказы /+1-й кратности, где / - некоторое целое число.

Информационные и контрольные разряды слова с выходов блока кодирования 9 поступают в регистр слова 5.

В блок управления 8 поступает код операции «Запись. По сигналу «Выдача кода с выхода блока управления 8 код слова из регистра слова 5 поступает на входы разрядного блока 3 накопителя 1, где записывается по адресу, определяемому кодом, записанным в регистре адреса 4.

Рассмотрим теперь режим считывания.

В регистре адреса 4 записан адресный код ячейки, информацию из которой необходимо считывать. По сигналу «Выдача кода с выхода блока управления 8 код адреса поступает на входы адресного блока 2 и с выходов разрядного блока 3 накопителя 1 считанный код поступаетна входы регистра слова 5, где записывается по сигналу «Прием кода с блока 8.

Считанный код поступает на входы блока контроля 6, который обнаруживает отказы кратности, 1, 2, 3, . При этом для каждой кратности отказа блок контроля 6 имеет отдельный выход.

В случае когда нет отказов, т. е. на всех выходах блока контроля 6 имеются сигналы, равные логическим нулям, то блок управления 8 формирует сигнал, по которому элементы И 7 открываются, н код считанного слова поступает на выходы устройства.

В случае, когда в коде слова есть отказ г-й кратности, где , то на выходах блока контроля 6, соответствующих однократному, двухкратному, ..., t-кратному отказам, появятся сигналы, равные логической «единице.

При наличии единичного сигнала хотя бы на одном из выходов блока контроля 6 блок управления 8 формирует сигнал записи «единицы, например, в младшем разряде регистра 10.

По сигналу блока управления 8 в регистре 10 записывается «единица в младшем разряде, после этого следует операция суммирования по модулю «два кодов в регистре слова 5 и в регистре 10. Для выполнения этой операции с выхода блока управления 8 Поступает сигнал «Выдача кода в регистр 10, КОД этого регистра, содержащий «единицу в младшем разряде, поступает па счетные входы регистра слова 5. При этом изменяется значение считанного младшего разряда считанного слова.

В Случае, если имеет место отказ в младщем разряде, то выход г-й кратности отказа блока контроля 6 изменит свое значение, т. е. значение его будет равным логическому «нулю. Следовательно, отказ в считанном слове после первого суммирования по модулю «два будет (i-1)-й кратности.

В этом случае, т. е. если кратность отказа уменьшилась на «единицу (и соответственно число «единиц на выходах блока контроля 6 стало на «единицу меньше), по сигналу «Сдвиг с выхода блока

управления 8 сдвигается на один разряд информация В регистре 10 и снова выполняется операция суммирования по модулю «два. В случае, Когда после суммирования по

модулю «два кратность отказа в коде считанного слова увеличивается, то число «единиц на выходах блока контроля 6 увеличивается на «единицу. Для восстановления исходного состояния

значения этого разряда необходимо снова просуммировать по модулю «два коды регистров 5 и 10, после чего выполпяется операция «Сдвиг.

Операции суммирования по модулю

«два и «Сдвиг выполняются до тех пор, пока из блока контроля 6 не поступает в блок управления 8 нулевой код, что говорит об устранении всех отказов.

При наличии нулевого кода на выходах

блока контроля 6 выдается команда «Установка в нуль па одном из выходов блока управления 8.

В предложенном устройстве упрощается реализация блока кодирования, и при этом

требуется меньшее число контрольных разрядов корректирующего кода.

Формула изобретения

Запоминающее устройство с самоконтролем, содержащее накопитель, подключенный к регистру адреса и регистру слова, соединенного с блоком контроля и блоком кодирования, и блок управления, отличающееся тем, что, с целью упрощения и

повышения информационной емкости устройства, оно содержит регистр отказов и элементы И, входы которых подключены к выходам регистра слова и блока управления, а выходы-к выходам устройства, входы регистра отказов соединены с выходами блока управления, а выходы - со входамП регистра слова.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 407399, кл. G НС 29/00, 1972.

2. Городний А. В., Корнейчук В. И. Проблема высоконадежной памяти - «Автоматика и телемеханика, 1974, № 7, с. 155.

1

Iw

J

;JZ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU955212A2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU936033A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Оперативное запоминающее устройство с автономным контролем | 1983 |

|

SU1113855A2 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU926726A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1973 |

|

SU374657A1 |

| Запоминающее устройство | 1972 |

|

SU470866A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

-J

-J7

/i

«J

-J

Авторы

Даты

1979-01-30—Публикация

1977-09-28—Подача