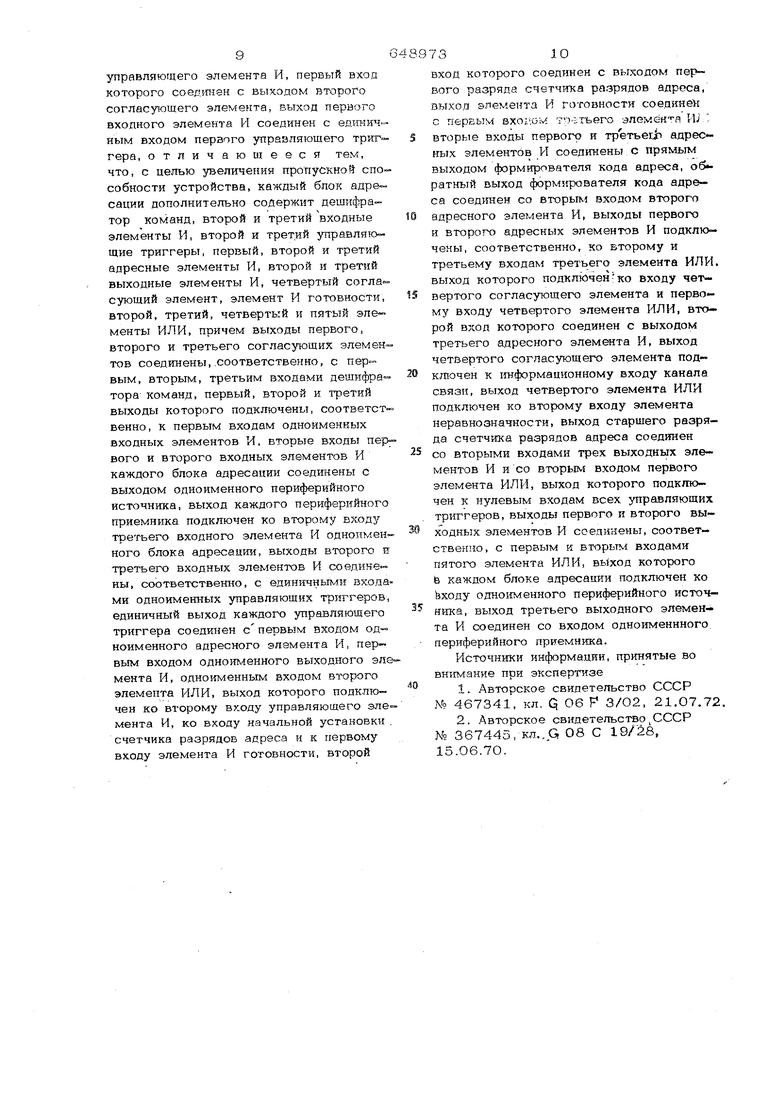

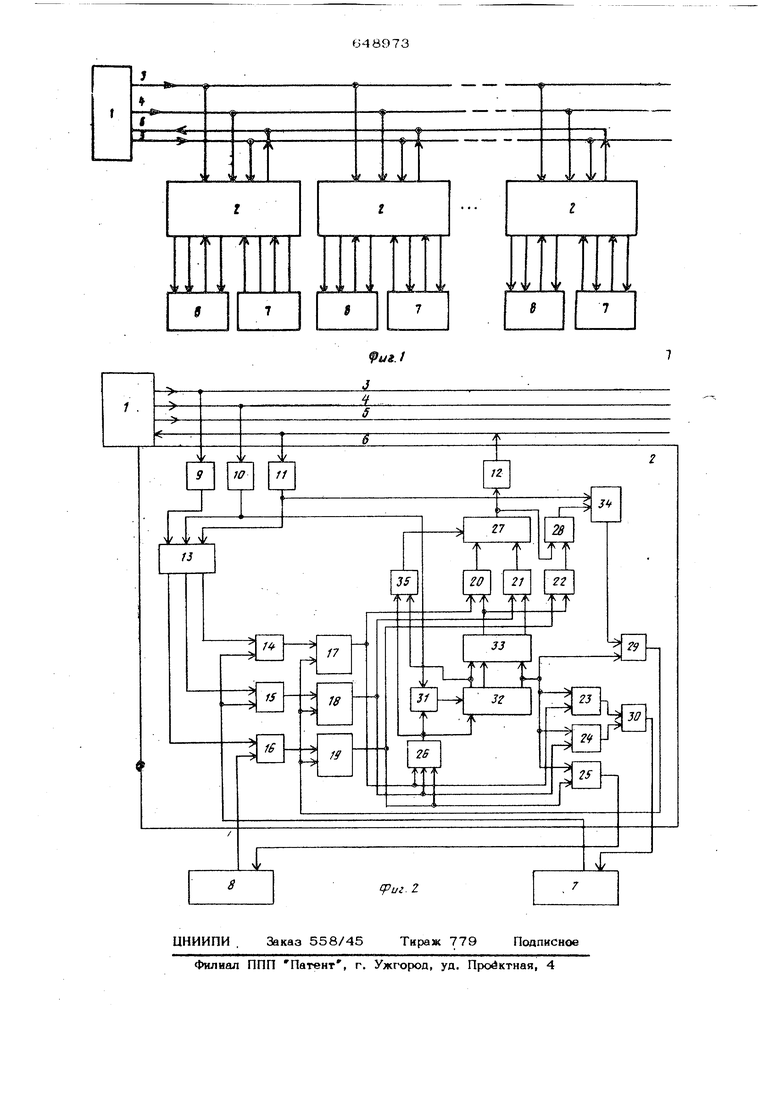

TOBs но не может обеспечить м. вызов. Поэтому данное устройство может при- меняться только для сбора информации, но не может- осуществлять ее вывод на объекты;в известном устройстве отсут ствует возможность выравнивания, приорите-гов. (Принятая в нем система приоритетов (в порядке возрастания адресов неприемлемей для многах характерных, ре жиМЬв функционирования, Например$ при равномерном поступлении информации в неблагоприятных условиах оказьшаются объекты с малыми номерами адресов; время реакции (временной интервал меж ду появлением на объекте информации и -началом передачи, адреса объекта) в известном устройстве соизмеримо с време нем передачи адресной последовательнос ти. Это влечет за собой уменьшение пропускной способности системы в це- лом. Целью предлагаемого устройства является увеличение пропускной способнос ти, Для этого в предлагаемом устройств каждый блок адресации дополнительно содержит дешифратор команд, второй и третий входные элементы И второй и третий управляюнше триггеры, парвьй второй и третий адресные элементыHf второй и третий выходные элементы Иs четвертый согласуюший элементэ эле-мент И готовности,, второй, третий четвертый и пятый элементы ИЛИ, причем выходы первого второго и третьего согласующих элементов соединенЫэ соот ветственнов с первым, вторым, третьим аходами дешифратора команд, первый, второй и третий выходы которого подкл чены, соответственное к первым &ходам одноименных входных элементов И, вто рые аходы первого и второго входных элементов И каждого блока адресадии соединены с выходом одноименного периферийного источника, выход каждого периферийного .приемника подключен ко второму входу третьего входного элеме та И одноименного блока адресации, вы ходы второго и третьего аходных элв М8НТОВ И -совдинень, соответственно с вдянйчньаж входами одноименнык управ лякацих триггеров, единичный выход каждого управлякшего триггера соединен с первым входом одноименного ад- ресйого элемента И первым входом од ноименаого выходного элемента И, одвонмещшм входом второго елемента ШШ, выход кото|и го йодкл.ючен ко вто рому входу управляющего элемента И, ко входу начальной установки счетчика разрядов адреса и к первому входу элемента И готовности второй аход которого соединен с выходом первого разряда счетчика разрядов адреса, выход элемента И готовности соединен с первым аходом третьего элемента ИЛИ, вторые входы первого и третьего адресных элементов И соединены с прямым выходом формирователя кода адреса, обратный выход формирователя кода адреса соединен со вторым входом второ:го адресного элемента И, выходы первого и второго адресных элементов И подключены, соответственно, ко второму и третьему входам третьего элемента ИЛИ, выход которого подключен ко входу четвертого согласующего элемента и первому аходу четвертого элемента ИЛИ, второй вход котораго соединен с выходом третьего адресного элемента И, выход четвертого согласуюшего элемента подключен к информационному входу канала связи, выход четвертого элемента ИЛИ подключен ко второму аходу элемента неравнозначности, выход стар™ шего разряда счетчика разрядов адреса соединен со вторыми входами трех выходных элементов И и со вторым входом первого элемента ИЛИ, вьссод которого подключен к нулевым входам всех управляющих триггеров выходы первого и второго выходных элементов И соединены, соответственно, с первым и вторым входами пятого элемента ИЛИ, выход которого в каждом блоке адресации подключен ко входу одноименного периферийного источника, выход третьего выходного элемента И соединен со аходом одноименного периферийного приемника. На фиГо 1 приведена электрическая ст-руктурная схема устройства; на фиг. 2функциональная схема блока адресации устройства. Устройство содержит канал связи 1, блоки адресации 2, первый управляющий выход 3 канала связи, второй управляющий выход 4 канала связи, информационный выход 5 канала связи, информационный аход 6 канала связи, периферийные источники 7, периферийные приемники 8, Блок адресации 2 содержит-; согласующие элементы 9-12, дешифратор команд 13, входные элементы И 14 , 15 и 16, управляющие триггеры 17, 18 и 19,

апресные вдёменты И 20, 21 и 22, выходные впементы И 23, 24 и 25, элементы ИЛИ 26-ЗО, управляющий элемент И 31, счетч гк 32 разрядов адреса, форьшрователь 33 кода адреса, элемент 34 неравнозначности, элемэнт И 35 готовности.

Блок адресации 2 обеспечивает выполнение следующих функций: передает код адреса объекта периферийного источника при наличии в нем готовой к передаче информации; воспринимает код адреса при вызове объекта периферийного приемника из канала связи.

Набирание периферийного устройства, готового к передаче информации, осуществляется следуюдаим образом. Из канала связи на выходы 3-5 передается команда Избирание с прямым (инверсным адресом. Если ни один из периферийных источников 7 не имеет готовой к передаче информации, то данная комбинация повторяется.

При появлении сигнала Готов на выходе периферийного источника на выход

4канала связи поступает серия синхронизирующих сигналов, которые обеспечивают опрос разрядов формирователей 33 кода адреса всех объектов, имеющих готовую в данный момент к передаче информацию. При опросе формирователя 33 кода адрес объекта передается с выхода

5канала связи. Кроме передачи информации, канал связи участвует в выделении старшего по приоритету объекта. Осуществляется это путем сопоставления каждого разряда адреса объекта с информацией, передаваемой в данный момент на выход 5 из канала связи. Если по каналу связи передается сигнал единицы, а в опращиваемом разряде адреса содержится ноль, то данный объект пр&-; крашает передачу адреса. Например, к передаче готовы объекты с адресами 7 (0111) и 5 (OiOl). При опросе старших двух разрядов передачу адреса ведут оба объекта. При опросе третьего

, разр$ша объект с адресом 5 откл1дчавт ся, так как в данном разряде его адреса содержится ноль, а в канал связи поступила (из устройства номер семь) единица.

Устройство для сопряжения канала

связис периферийными источниками и периферийными приемниками может оперировать прямыми и инверсными адресами объектов. При использовании прямых адресов старшим приоритетом обладает

объект с более высоким номером адреса, а при использовании инверсных адресов с более низким. Например, если к передаче готовы объекты с адресаьш1 (ООО1), 5(OrUl) и 7(0111/, то при прямой адресаций очередность изби- рания объектов будет 7, 5, 1, а при ин версной адресации - 1:, 5, 7 (инверсные коды адресов этих объектов соответственно равны то, 101О, ЮОО).

0

При наличии готовой к передаче информации (при поступлении.сигнала с выхода одного из периферийных источников) команда Набирание с прямым адресом

5 открывает входной элемент И 14, переводит в состояние единица триггер 17, подготавливает элементы 20 и 23. Одновременно через элемент ИЛИ 26, переводится в исходное состояние счетчик

О 32 и открывается управляющий элемент И 31, через который синхронизирующие сигналы с выхода 4 канала связи поступают на счетный вход счетчика 32. Сигнал с первого разряда счетчика 32 (по

5 первому синхронизирующему импульсу) открывает элемент И 35, который передает на вход 6 канала связи (через схему ИЛИ 27) сигнал Готов. Последующие синхронизирующие импульсы, воздей0ствуя на счетчик 32, производят опрос разрядов формирователя 33 кода адреса. С прямого выхода формирователя 33 кода адреса прямой код адреса через адресный элемент И 20 и элемент. ИЛИ

5 27 поступает на вход 6 канала и через элемент ИЛИ 28 - на вход элемента неравнозначности 34, на второй вход которого подается сигнал нз канала связи. В данном случае канал связи

0 выполняет функцию сборки для всех объектов. Если в опращиваемом разряде формирователя кода 33 записаны ноль, а в канале связи сигнал единицы, то элемент неравнозначности 34 выдает сигнал, ко5торый (через схему ИЛИ 29) производит гащение триггера 17. Тем самым переводится в нулевое состояние счетчик 32 и данный объект прекращает передачу адреса до конца текущего цикла

0 связи. Если данный объект осуществляет передачу адреса один или имеет наиболее высокий приоритет, то счетчик 32 завершает свою работу и сигнал с выхода его последнего разряда через выходной элемент 23 и элемент ИЛИ 30 поступает на вход периферийного источника, разрешая тем самым передачу информации. Одновременно через элемент ИЛИ

29 подается сигнал установки нуля на триггер 17.

При поступлении из кйтмла связи ко« манды Набирание с тшерсным алресом открывается эпемент 15, становится в единичное состояние триггер 18 и подготавливаются к работе элементы 21 и 24. Начиная с данного момента, устройство работает аналогично описанному. Отличием является то, что с формирователя 33 кода адреса на вход б канала связи и в элемент неравнозначност-и по-даетсяинверсный код адреса.

Наличие режимов избирания с пря-. мым и инверсным кодами адресов позво лает установить приоритеты в порядке возрастания и убьгаания адресов объектов, а также выравнивать приоритеты устройства.

Выравнивание гфиоритетов объектов осуществляется путем чередования сннХ ронкзирующих последовательностей с прямой и инверсной системой адресования. При этом канал связи чередует меж ду собой команды Набирание с прямым . адресом и Изб1фание с инверсным адресом. При одинаковом количестве синхронизирующих последовательностей с пря мой и инверсной адресацией условия из- бгфания всех объектов становятся; одг-шаковыми, т.е. все они имеют один и тат же (в статистическом смысле) приори-тетный уровень. Вырьируя это соотношение, можно, регулировать условия избирания объектов.

ЕЗызов объекта (для вывода кнформа-ции на канала связи и периферийный приемник 8) осу|дествляется путем посыпки его адреса на выход 5 канала связи, Предваритеяьно канал сзйзи 1 посы--лает на выходы S 5 командзг Езызов На всех обт ектах, готовых к приему информации (сигнал с выхбда периферийно -го приемника), по дайной команде от крыеается элемент 16, переводится в единичное положение триггер 19, oTicpbi™ ваются элементы 22 и 25, переводит.

, ся в исходное состояниесчетчш -32„.

Код адреса объекта передается по выходу 5 канала связи и сопровоздэет-ся по выходу 4 синхронизЕфующими сигналами, которые через эпемент 31 осу« ществляют сдвщ счетчжо 32. При этом прягмой код адреса с ..прямого, выхода форл ирователя 33 кода адреса постз ает через элемент 22 и элемент РШИ 28 на вход элемента 34 неравнозначноти, . сравнивает его с кодом, пе рейаваемь№ { по каналу связи.

Лри несовпадении какого-.-либо разряда кола адреса элемент 34 неравнозначности (путем гашения триггера 16 и счетчт в 32) выключает устройство ад- ресапии.

Если коды адресов совпадают, то через ключ 25 подается сигнал на вход периферийного приемника, подготавливая его к приему информации.

Таким образом, предлагаемое устрой , ство обеспечивает выполнение всех функ

ций, необходШЛых для сопряжения канала связи с периферийными приемниками информации и периферийными источниками информации. Оно осуществляет изби- рание готовых к передаче периферийных источников и вызов их по адресу. При этом обеспечивается гибкое управление системой приоритетов и достаточно малое время реакции, которое не превьгашет двух рабочих тактов.

Экономический эффект предлагаемого устройства заключается в увеличении коэ44)ициента использовштая оборудования (за счет обеспечения режима вывода информации) и в увеличении пропускной способности системы, а следовательно, и чиспа подключаемых объектов (за счет болеегибкой системы приоритетов и укШиьшения времени реакции).

Формула изобретения

.Устройство для сопряжения канала связи с периферийными источниками и пе.риферийнымй приемниками, содержащее П --блоков .адресации, каждый из кото- рых соаержлт первый, второй, третий согяас тощие элементы, элемент неравно значности, счетчик разрядов адреса, фор- .мирователь кода адреса, управляющий элемент И, первый входной элемент И, первый управляющий триггер, выходкой впемент И, первый элемент ИЛИ причем входы первых трех согласующих элементов соединены, соответственно, с первым управляющим, вторым управляющим и информационным выходами канала связи, выход третьего согласующего элемента соединен с первым входом элемента неравнозначности, выход которого соединен с первым входом первого эле-. мента ИЛИ, выходы счетчика разрядов адреса соединены со входами формирователя кода адреса, счетный вход счетчика разрядов адреса соединен с выходом

управляющего элемента И, первый вход которого соединен с выходом второго согласующего элемента, выход первого входного элемента И соединен с единичным входом первого управляющего триггера, отличающееся тем, что, с целью увеличения пропускной способности устройства, каждый блок адресации дополнительно содержит дешифратор команд, второй и третий входные элементы И, второй и третий управляю™ щие триггеры, первый, второй и третий адресные элементы И, второй и третий выходные элементы И, четвертый согласующий элемент, элемент И готовности, второй, третий, четвертый и пятый эле- менты ИЛИ, причем выходы первого, второго и третьего согласующих элементов соединены,,соответственно, с первым, вторым, третьим входами дешифра-тора команд, первый, второй и третий выходы которого подключены, соответственно, к первым входам одноименных входных элементов И, вторые входы первого и второго входных элементов И каждого блока адресации соединены с выходом одноименного периферийного источника, выход каждого периферийного приемника подключен ко второму входу третьего входного элемента И одноименного блока адресации, выходы второго и третьего входных элементов И соедине ны, соответственно, с единичными входами одноименных управляющих триггеров, единичный выход каждого управляющего триггера соединен с первым входом од-« ноименного адресного элемента И, первым входом одноименного выходного элемента И, одноименным входом второго элемента ИЛИ, выход которого подключен ко второму вг.оду управляющего эле мента И, ко входу начальной установки . счетчика разрядов адреса и к первому входу элемента И готовности, второй

ВХОД которого соединен с выходом первого разряда счетчттеа разрядов адреса, выход элемента И готовности соединен с первым Bxouoiv у).;тъего элемен а VIJ вторые входы первого и третьеьЬ адресных элементов И соединены с прямым выходом формирователя кода адреса, об ратный выход форм -фователя кода адре са соед1гаен со вторьп входом второго адресного элемента И, выходы первого и второго адресных элементов И подключены, соответственно, ко второму и третьему входам третьего элемента ИЛИ. выход которого подключен-ко входу чет5вертого согласующего элемента и первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего адресного элемента И, выход четвертого согласующего элемента под0ключен к информационному входу канала связи, выход четвертого элемента ИЛИ подключен ко второму входу элемента неравнозначности, выход старшего разряда счетчика разрядов адреса соединен

5 со вторыми входами трех выходных элеMeHixjB И и со вторым входом первого элемента ИЛИ, выход которого подключен к нулевым входам всех управляющих триггеров, выходы первого и второго выходных элементов И соединены, соответственно, с первым и вторым входами пято) элемента ИЛИ, выход которого b каждом блоке адресации подключен ко Ьходу одноименного периферийного источ5ника, выход третьего выходного элемента И соединен со входом одноименнного. периферийного приемника.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 467341, кл. Q 06 Р 3/О2, 21.07.72.

2.Авторское свидетельство СССР № 367445, KH...Q 08 С 19/28,

15.Об.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для диагностирования периферийных устройств | 1990 |

|

SU1716518A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1829038A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1989 |

|

SU1667090A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

Авторы

Даты

1979-02-25—Публикация

1977-01-03—Подача