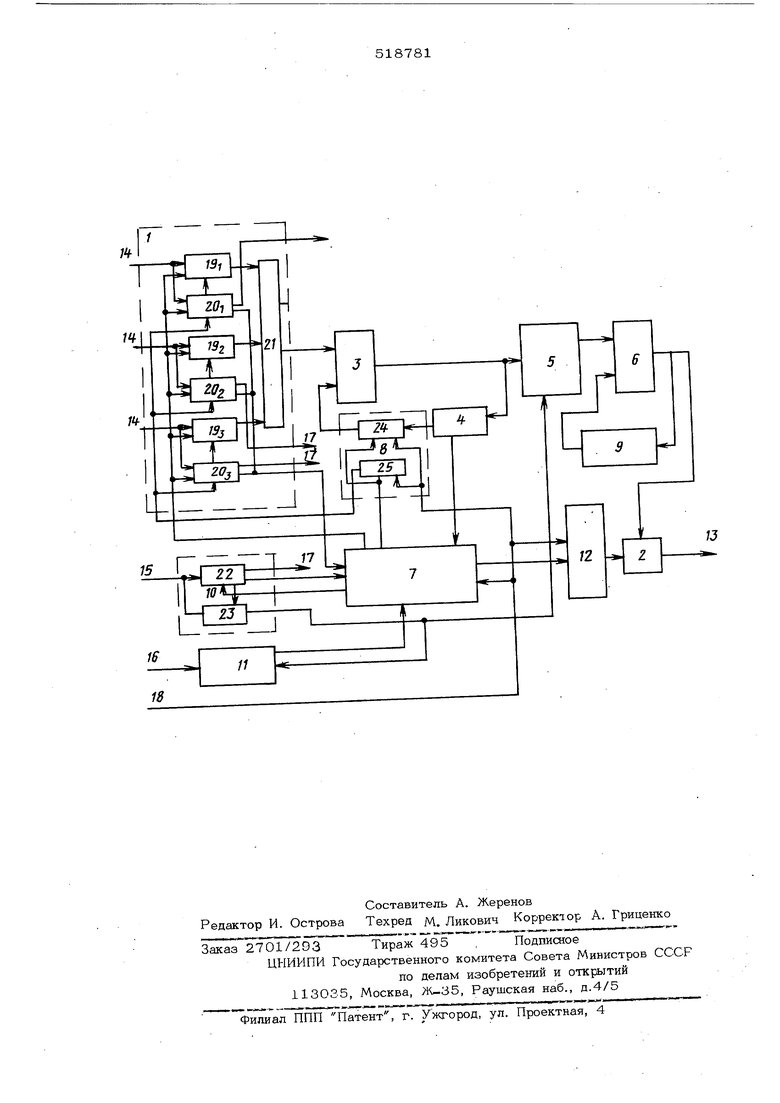

функции и регистры порядков приращений подынтегральной функции, соединенные первыми входами с шшюй приращений подынтегрально функпии, вторые входы регистров мантисс пр решений подьштегральной функции и регистров порядков приращений подьштех альной функции подключены к первому выходу блока ущзавления масштабированием, третьи входы соединены соответственно с первыми выхода регистров Порадков приращений подынтеграпь НрЙ функции, вторые выходы которых ПОДКЛЮ чены к выходной шине обратного масштабного сигнала, третьи выходы - к первому входу блока управления масштабированием и , выходу регистра порадков подьштегральной функпии, первый вход регистра порядков подынтегральной функции соединен с шиной ввода начальных данных, второй вход объединен со вторым входрм регистра мантисс подынтегральной функции и подключен ко вто рому выходу блоке управления масштабированием, входы регистра порядков переменной jiHTerpHjMjBaHHS соединены соответственно с шиной приращений переменной интегрирования и с третьим выходом блока управления масштабированием, выходы - подключ ны соответственно ко второму входу регистра мантисс переменной интегрирования, ко второму входу блока управления масштабированием и к выходной шине обратного мас-« штабного сигнала, входы блока управления масштабированием, начиная с третьего входа, соединены соответственно с первым выходом блока нормализации, с вдиной вводе начальных цвапклк, с выходом блока щжем и хранения обратного масштабного сигнала, а выходы, начиная с четвертого, соединены соответственно с первым входом блока изменения порядка выходных гф ащений и с первым входом блока приема и хранения обратного масштабного сигнала, вход блока нормализации соединен с выходом сумматора подьштегральной функции, второй выход с третьим входом регистра мантисс подынтегральной функции, второй вход блока приема и хранения обратного масштабного сигнала соединен с входной шшюй обратного масштабного сигнала, второй вход блока иаменення порядка выходных приращений сое- дннен с шиной ввода начальных данных, выход подключен к соответЬтвук щему входу блока выделения выходных приращений. Это позволяет повысить точность вбшис. лени и и уменьшить время подготовки задачи к решению. Устройство обеспечивает режим автом тнческого масштабирования, суть которого аа1(Л10шется в том, что каждое вычислитель ное устройство )овой интегрирующей стру туры аместо с выходными приращениями вырабатьшаот Мйсштабныо сигналы, которые ха|.1актвриаукл лзмененно гюря/и ч пуромг- и :ных, изменение масштаба выраГшгЫв-аемь-и пр1фашений и возможные или иеобхлшимькизменения масштабов приращений йходных «величин. Так как при решении конкретных |аадач все устройства связаны между собой IB соответствии со схемой коммутации, то изменение масштабов в одном устройстве за|висит от возможности изменения масштабных (Соотношений в других, связанных с ним устройствах. Автоматическое масштабирование переменных в устройствах цифровой интегр1фуюшей структуры осуществляется выгголнением основных масштабных соотношений: Пу ПагПа,-0, П у п-к-Пу-Мр2 0 где П - порядок подынтегральной функции| порядок приращений переменной интегрирования, nds - порядок выходных приращений, Mtoi - количество сдвигов приращений подынтегральной функции; ridu - порядок приращений подынтегральной функции; Я - количество мантиссы подынтегральной функции; К - количество разрядов приращений подынтегральной функции. На чертеже представлена схема устройства, котсфое содержит блок 1 пр фащений подыягёгральной функции, блок 2 выделения выходных приращений, сумматор 3 подынтегральной функции, блок 4 нормализации, блок 5, умно кения,, сумматор 6 остатка интеграла, блок 7 управления масштабированием, блок 8- хранения подынтегральной функции, регистр 9 хрьнения остатка интеграла, блок J.O приращений переменной интегрирования, блок И приема и хранения обратного масштабного сигнала, блок 12 изменения порядка вьосодных приращений, шину 13 выходных приращений, шину 14 приращений подынтегральной функции, щину 15 приращений переменной интегрирования, входную шину 16 обратного масштабного сигнала, выходную шину 17обратного масштабного сигнала, шину 18ввода начальных данных, В состав блока 1 входят регистры 19j.19j мантисс приращений подынтегральной функции, регистры 2С||-2О, порядков приращений подынтегральной функции и комбинационный сумметор 21, блок ip включает регистр 22 порядков переменной интегрирования и регистр 23 мантисс переменной интегрирования, блок В содержит регистр 24 мантисс пoдынтerpaлIJ.ной функции и регистр 25 порядка подынтегальной функции. .)ii.(;(/r p :4iiBinw М ./жио рлабнть на три n-if-jio/ioHatc3jn,.4btx WJ времлни этапа, УГЛЯ врод, шиле 18 ввода начальных ПЯИНТ.1Х к блок 8 хранения подынтегральной функции заносится мантисса и порядок /Пу/ начального значения подынтегральной функции, а в блок 12 изменения порядка выход;Ных прфашений - порядок выходных прира; щений. После окончания ввода по шине 18 на вход блока 7 поступает сигнал окончания ввода. Блок 7 управления масштабированием выдает в блок 1 приращений подынтегральной функции сигнал /tt - к/ и в блок 8 сигнал разрешаюшйй передачу значения порядка в блок 1. Начальные значения порядков входных приращений определяются по формуле:Мрг п-к-Пу После выполнения ; прямой и обратной передачи масштабных сигналов все устройства включеЯные в задачу, масштабно согласованы между собой при условии, что порядок приращений независимой переменной Hflt paвен нулю. Второй этап - начальное масштабирование. Он заключается в том, чтобы от значения FlAt О перейти к Пд-6- 1 { A.t - заданный шаг решения) На этом этапе работают только блоки, предна31яаченные для автоматического масштабирования. Если входы блока 10 или блока 1 закоммутированы входными шинами 14 или 15 на машинную переменную, то по разрешающим сигналам,, поступающим из блока 7 в течение а шагов начального масштабирования в качестве прямого масштабного си нала поступает сигнал -1, который складывается с порядками приращений блоков 1 и 1О, После а щагов происходит стабилизация порядков и числовой информации. При стабилизации работают все блоки автоматического масштабирования и полностью осу- ществляется. автоматическое масштабировани Третий этап - решение задачи с заданным щагом Устройство осуществляет преобразование информации, представленной в виде квантованных приращений, в соответствии с раэностной системой уравнения. Процесс автоматического масштабирования заключается в обработке масштабных сигна пов, изменении порядков подынтегральной функции Пу , выходных приращений ds н переменной интегрирования Hcix , а также сдвиге мантисс входных приращений, подынтвг()альной функции и выходных приращений В aBTOhmTHfi-CKOK М«Г1|Г ;1б)5(1( .доч; но выделить. Т-рп уровня, На первом уровне отработывй тг-я г- Ivjn /приходящее значение изменения порялкн ичм;. (ращений переменной интегрирования. Кои) порядок приращений переменной пнтегрированийэ хранимый в блоке 10 ггриратцения по, ременной интегрирования, больше .-.яуля, то из блока 10 в блок 7 управления масштабированием поступает соответствуюгций и если из блока 4 нормализации к uepcnojraoния поступает в блок 7 сигнел о том, что мантисса подынтегралЬ||ой функции в блоко 8 не нормализована, то блок 7 выдает управляющие сигналы: в блок 8 храиер-гкя иодынтегральной функции, при котором мантисса подынтегральной функции слвигается влево на один разряд и порядок уменьшается на единицу; в блок 10, при котором значение порядка переменной илтегрпровпния уменьшается на единицу в блок 1, ii) котором порядок входных пр рашепчй иодьттегральной функции увеличиваетсй на однкк цу. Все эти деГа:стБия выполр.яются по тех пор пока значение порядка перемонтгой кн-. тегрирования в блоке 10 не станет равным нулю или пока кз блока 4 поспугьчет си -гал о том, что мантисса подьгнтегральной фун;гции не нормализована. Если из блока 1О в блок 7 поступао-с сигнал о том, что порядок пр15раш. ггероманной интегрирования больше нуля, а из блока 4 в блок 7 поступает сигнел о том, что мантисса подынте1тэальнай функции в блоке 8 нормализовала, то блок 7 выдаетуправляющие сигналы: в блок 12 измепоиия порядка выходных пр1фащений, при котором значение порядка увеличивается на в блок 10, при котором значение порядка переменной интегрирования уменьшается на единицу, в блок 11 приема и хранения обратного масштабного сигнала, при котором значение порядка обратного масштабнопо сигнала увеличивается на единицу. Все эти действия выполняются до тех пор нока из блока 1О в блок 7 поступит сигнал о том, что значение порядка переменной китегрирования в блоке 1О равно нулю. Если из блока 10 в блок 7 поступает сигнал о том, что порядок приращений переменной .ингегрироваяия. меньше нуля, а нэ блока 11 в блок 7 поступает сигнал о том. что значение порядка обратного масштабного сигнала меньше нуля, то блок 7 выдает управляющие С ггналы: в блок &г при кот-орог-.г мантисса подынтегральной функьия сдонт-а;ется вправо на один разряд, а по|:) yr.. |личивается па единицу s блок iOj .- тором значеяпе пор5гдка пе} еменпой и-итогрк рования увеличивается на вдпьниу; п б;н;.к , I Щ)Н котором поряяок входных приращений ио дынтеграяьной функции уменьшается на единицу. Все эти действия выполняются до тех пор пока аначение псчрйдка переменной интег ркрования в блоке 10 не станет равным нул или пока значение порядка обратного масшт а ного сигнала в блоке 11 не станет больше нли рабным нулю, ; Если из блока 10 в бпок 7 поступает сюгнал о том, что п6ря)1ок приращений iieремёкной интегрирования ме1льше нуля, alia блока 11 в ёлок 7 поступает сигнал о том, что аначени© порядка обратного масштабного с$ гнала не меньше нудя, то блок 7 выда ет управляющиесигнапы: в блок 12, при котором значение порядка выходных прираЩй1шй уменьшается на единицу; в блок 10, нря котором зиачеюге порядка переменной интегрирования увели «рвается на единицу в бкт 11, ирй котором значение порядка обратного масштабного сигнала уменьшает Сй на едйШ4цу. Вчсе эти действия повторяются до тех 1юр, акжа КЗ бдока Ю в блок 7 не посту- 8|Я«г сйгнйя о том, что значение порядка п& реме ай:ой интегрирования равно, нулю, Если значение порядка переменной ннте рнрования в блоке 1О равно нулю, то на этом загсанчивается первый уровень автомат Гй юского масштабирования и осуществляет са керехоя ко второкту уровню, на котором Ш1|кжсхояит улучшение режима вычиспешй. В течение всего времени выполнения sToporo уровня из блока 1О в блок 7 посту иает сигнал о том, что значение порядка переменной интегрирования равно нуяю. Если на блока 11 в блок 7 поступает Сигнал о том.что знаЧе1ше порядка обратно го масштабного сигнала меньше нуля, то яз баожа 7 поступают сягнада г: в блок 8, ао которому происходит сдвиг мантиссы йоды гтегральиой функции вправо на один разряд,и увеличение порядка на единицу в блок 1, по которому происходит уменьшен мие значений порядков входных прирашений яодынт-ег-рапьной функций на единицу; в блок 11, по KOTopoivry «роисходит увеличение порядка обра гног масштабного сигнала на единицу, в бпок 12, пoкoгopo Iyпpoиcxoдигyвв пиченне порядка выходных приращений на едини цу.: Этн действия повторяются до Тех пор пока из блока 11 в блок 7 не поступит о том, что значение порядка обрач ного масштабного сигнала равно нулю, Если из блока 11 в блок 7 поступает сигнал о том, что значение обратного мас«п-абного сигнала не меньше нхля и из блока 4 в блок 7 поступает сигнал о том, чгомантнсса подынтегральной функции не иормалязовпаа, из блока 7 поступают лы; в блок 8,; по которому происходит СДЕЛГ мантиссы подынтегральной 4у1шции вяеьо на один разряд и уменьшение поря|ша на дивицу;,в блок 1, по которому происходит увего1чение порядков входных приращений подынтегральной функции в блок 11, по которому происходит уменьшение Порядка обратного масштабного сигнала на еданицу; в блок 12, по которому происходит уменьшение порядка выходны с приращеЭти действия повторяются до тех пор |Пока из блока Ив блок 7 не поступит (Сигнал о том, что значение порядка обратного масштабного сигнала paBiHo нулю. Если изГблока в блок 7 поступает сщ%. нал O:;TOM, что значение обратного масшта& ного сигнала не меньше нуля и из блока 4 в блок 7 поступает сигнал о том, что Maib тисе а подынтегральной функции нормализована, то на этом заканчивается второй уровень автоматического масштабирования, в этом случае нельзя улучшить режим вычиолений. Второй уровень заканчивается также,когда из блока 11 в блок 7 поступает сигнал о Том, что значение обратного масштабного сигнала равно нулю. Третий уровень автоматического масштабирования - это контроль порядков входных приращений подынтегральной функции. Если из блока 1 в блок 7 поступает сигнал о том, что значение порядка входных приращений подынтегральной функции больше ;ЗНачения п-к, т. е, приращения выходят за старшие разряды мантиссы подынтегральной функции, то блок 7 вырабатывает управляющие сигналы, которые поступают; в блок 8, по которому происходит сдвиг мантиссы поДЫ1Ггег альной функции на один разряд вправо и увеличение порядка на единицу; б блок 12, по которому происходит увеличение порядка выходных приращений на единицу; в блок 1, по которому происходит уменьшение порядка входных при1ращений на едини цуТ в блок 11, по которому происходит увеличение хюрядка обратного масштабного сигнала на единицу.. Эти действия повторяются до тех пор, пока значение порядков входных п:рира1цений подынтегральной функции не станет меньше значения (п-к), На этом автоматическое масшабирование заканчивается. Устройство переходит к выполнению вычислительных операций с заданным шагом Форму л а изобретен и Я Вычислительное устройство цифровой и егрируюшей структуры, содержаяюе perHCiv.

9 ры мантисс приращений подынтегральной функции, первые входы которых соединены с шиной приращений подынтегральной функции, выходы через комбинационный сумматор соединены с первым входом сумматора подынтегральной функции, второй вход которого соединен с выходом регистра мантисс подынтегральной функции, первый вход которого соединен с шиной ввода начальных данных, выход сумматора подынтегральной функции соединен с первым входом блока умножения, второй вход которого соединен с выходом реги стра мантисс переменной интегрирования, пе вый вход которого соеаинен с шиной приращ ний переменной интегрирования, выход блока умножения подключен к первому входу сумматора остатка интеграла, второй вход кото рого подключен к выходу регистра хранения остатка интеграла, выход соединен со входами регистра хранения остатка интеграла и блока выделения выходных приращений, подкл ченного к выходу устройства, о т л и чающееся тем, что, с целью повышения точности при работе с фиксированной запято и многоразрядными прираш,ениями и повышения эффективности использования устройства в него введены блоки управления масштабированием, нормализации, приема и хранения обратного масштабного сигнала, изменения порядка выходнь/х приращений, регистр поряд ков переменной интегрирования, регистр порядков подынтегральной функции и регистры порядков приращений подынтегральной функции, соединенные первыми входами с шиной приращений подынтегральной функции, вторые входы регистров мантисс приращений подынтегральной функции и регистров порядков приращений подынтегральной функции подключены к первому выходу блока управления масштабированием, третьи входы соединены соответственно с первыми выходамирегист ров порядков приращений подынтегральной

10 функции, вторые выходы которых подключены к выходной шине обратного масштабного сигнала, третьи выходы - к первому входу блока управления масштабированием и выходу регистра порядков подынтегральной функ-. ции, первый вход регистра порядков подынтегральной функции соединен с шиной ввода начальных данных, второй вход объединен со вторым входом регистра мантисс подынтегральной (функции и подключен ко второму выходу блока управления масштабированием, входы регистра порядков переменной интегрирования соединены соответственно с шиной приращений переменной интегрирования и с третьим выходом блока управления масштабированием, выходы подключены соответственно ко второму входу регистра мантисс переменной интегрирования, ко второму входу блока управления масштабированием и к выходной шине обратного масштабного сигнала, входы блока управления масштабированием.начиная с третьего входа, соединены соответственно с первым выходом блока нормализации, с шиной ввода начальных данных, с выходом блока приема и хранения обратного масштабного сигнала, а выходы, начиная с четвертого, соединены соответственно с первым входом блока изменения порядка выходных приращений и с первым входом блока приема и хранения обратного масштабного сигнала, вход блока нормализации соединен с выходом сумматора подынтегральной функции, второй выход - с третьим входом регистра мантисс подынтегральной функции, второй вход блока приема и хранения обратного масштабного сиг- . нала соединен с входной шиной обратного масштабного сигнала, второй вход блока изменения порядка выходных прираш.ений соединен с тииной ввода начальных данных, выход подключен к соответствующему входу блока выделения выходных приращений.

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Цифровой интегратор с плавающей запятой | 1975 |

|

SU590774A2 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Устройство масштабирования цифрового дифференциального анализатора | 1983 |

|

SU1156069A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Интегрирующее устройство | 1978 |

|

SU781849A1 |

Авторы

Даты

1976-06-25—Публикация

1974-11-25—Подача