при использовании цифровых интегрирующих структур в системах управления. Этот метод неудобен при расширении круга задач, когда от задачи к задаче масштабирование иретерневает большие изменения.

Целесообразным оказывается автоматический расчет начальных значений разностей порядков с помош,ыо самой ОЦИС. Этот расчет осуш ествляется в процессе выравнивания начальных норядков. Суть процесса выравнивания начальных порядков состоит в том, чтобы определить начальные значения разностей порядков в соответствии с порядками Про начальных значений функций, для чего в цифровом интеграторе требуется преобразовать код начального порядка подынтегральной функции Про в ноток одноразрядных прираш,ений, осуш,ествить уравнение этим потоком и формированием приращений порядка подынтегральной функции и начальных значений разностей порядков, не выходящих за пределы допустимых значений.

Целью изобретения является повышение быстродействия.

Поставленная цель достигается тем, что в известное устройство введены блок выравнивания начальных порядков и блок управления выравниванием начальных порядков, причем первый вход блока управления выравнивания начальных порядков соединен со входом переменной интегрирования интегратора, второй - с выходом блока образования приращения порядка подынтегральной функции, выход регистра порядка подынтегральной функции соединен с первым входом блока выравнивания начальных норядков, второй вход которого соединен с первым выходом блока управления выравниванием Ha4av4bHbix порядков, третьими входами реверсивных счетчиков и пятым выходом интегратора, третий - с первым входом приращения подынтегральной функции интегратора и со вторым входом регистра мантиссы подынтегральной функции, выход - с третьим входом блока управления выравниванием начальных порядков, второй выход которого соединен с шестым выходом интегратора, остальные входы блока Злравления выравниванием начальных порядков соединены с третьими выходами блоков анализа состояний счетчиков.

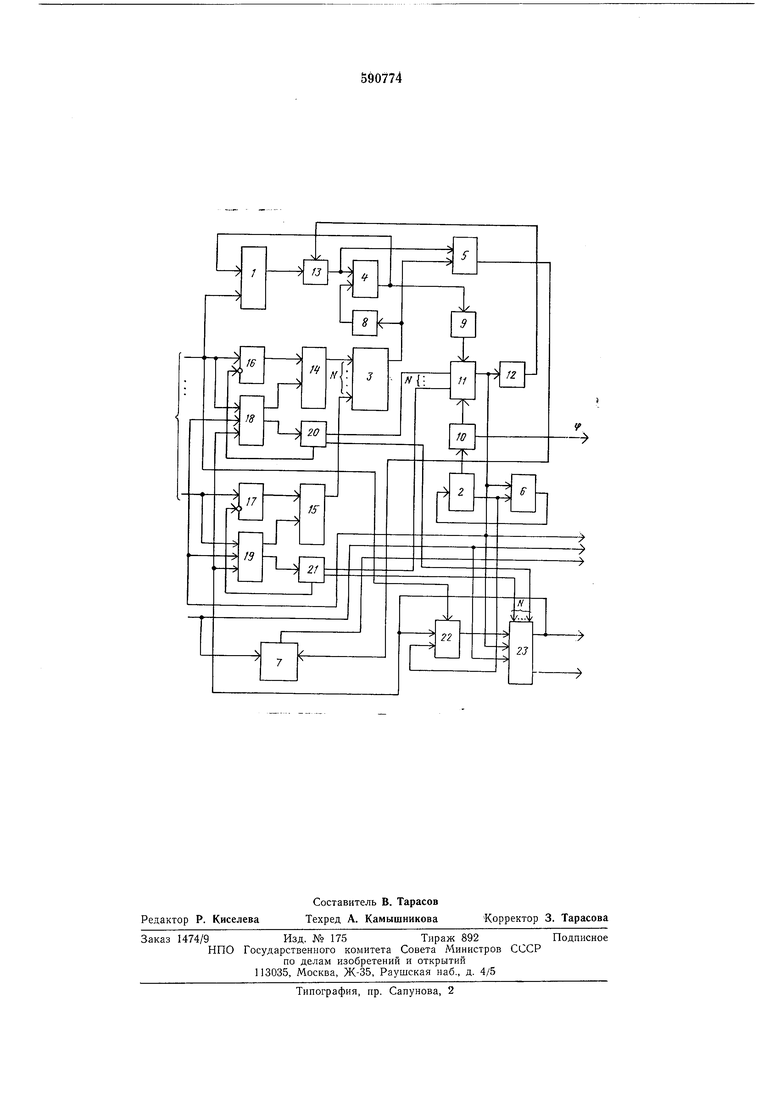

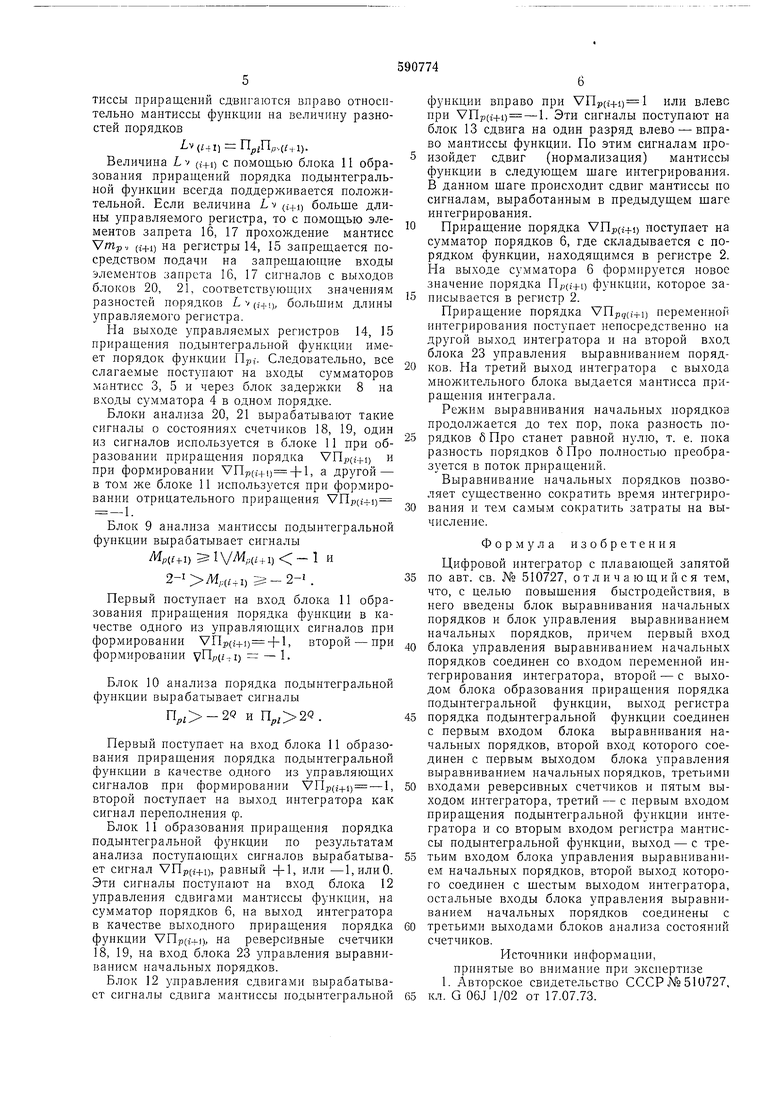

Блок-схема устройства представлена на чертеже.

Схема содержит регистр 1 мантиссы подынтегральной функции длиной п разрядов, регистр 2 порядка подынтегральной функции длиной Q разрядов, сумматор 3 мантисс приращений, сумматоры 4, 5 мантиссы подынтегральной функции, сумматор 6 порядка функции, множительный блок 7, блок 8 задержки, блок 9 анализа мантиссы подынтегральной функции, блок 10 анализа порядка функции, блок 11 образования приращений порядка подынтегральной функции, блок 12 управления сдвигами мантиссы функции, блок 13 сдвига мантиссы функции на один разря/чвлево-вправо, управляемые регистры 14, 15, элементы запрета 16, 17, реверсивные счетчики 18, 19, блоки 20, 21 апализа состояний счетчиков, блок 22 выравнивания начальных порядков, блок 23 управления выравниванием начальных норядков.

Работает интегратор следующим образом.

При вводе начального значения функции по первому входу интегратора в регистр 1 мантиссы подынтегральной функции заносится начальное значение мантиссы Про подынтегральной функции, в блок 22 заносится начальное значение норядка Про подынтеграл1 ной функции. Одновременно из регистра 2 в блок 22 поступает значение порядка подынтегральной функции Пр,-. В блоке 22 образуется разность норядков и Про. После вво/т,а начальных данных, т. е. собственно в процессе выравнивания начальных порядков, в блоке 0 23 управления выравниванием начальных порядков в зависимости от образованной в блоке 22 разности порядков б Про, приращения порядка УПр(г+1) подыптегральной функции, ноступающего с выхода блока 11 образования приращения порядка подынтегральной функции, приращения порядка УПр(г+1) переменной интегрирования, поступающего со входа переменной интегрирования интегратора, формируется приращение порядка У(бПро), ностунающее на вход блока 22, где формируется текущее значение разности порядков б Пр(г+1), на третьи входы счетчиков реверсивных 18, 19 для формнрования начальных значений разностей L ,,„ норядков и на выход интегратора для учета в других интеграторах, и сигнал выравнивания начальных порядков, выдаваемый из цифрового интегратора в устройство управления, для чего в блоках 20, 21 анализа состояний счетчиков образованы дополнительные выходы, которые поступают па ;V входов блока 23 управления выравниванием начальных порядков.

На ( цикле вычислений на входы интегратора поступают приращения подынтегральной функции в виде мантисс Уотр -.(j i), Vmg(t+i) и одноразрядных нриращений порядков

гПр (/М) рд()0 Приращения порядков УПр-;(г+1) приращений нодынтегральной функции поступают на счетчики 18, 19, где образуются новые значения разностей порядков Lv(),B результате чего перестраиваются управляемые регистры

5 14, 15. Па выходе блоков анализа состояний счетчиков 18, 19 появляются потенциалы, соответствующие новым состояниям счетчиков, которые подготавливают элементы запрета 16, 17. При прохождении мантисс приращеПИЙ Vmpv (i+i) через управляемые регистры 14, 15 мантиссы задерл иваются в них на величину (п-Lv(i-fl), онределяемую состоянием счетчпков 18, 19, а мантисса ) подынтегральной функции в это время задерживается

на п разрядов в регистре 1. В результате мантиссы приращений сдвигаются вправо относительно мантиссы функции на величину разностей порядков

V(i4i) ПргПр„(г+1).

Величина L v (i+i) с помощью блока 11 образования приращений порядка подынтегральной функции всегда поддерживается положительной. Если величина L г+ц больще длины управляемого регистра, то с помощью элементов запрета 16, 17 прохождение мантисс V/Пр, (г+1) на регистры 14, 15 запрещается посредством подачи на запрещающие входы элементов запрета 16, 17 сигналов с выходов блоков 20, 21, соответствующих значениям разностей порядков Lv(,-.,) больщим длины управляемого регистра.

На выходе управляемых регистров 14, 15 приращения иодынтегральной функции имеет порядок функции Пр,-. Следовательно, все слагаемые поступают на входы сумматоров мантисс 3, 5 и через блок задержки 8 на входы сумматора 4 в одном порядке.

Блоки анализа 20, 21 вырабатывают такие сигналы о состояниях счетчиков 18, 19, один из сигналов используется в блоке 11 при образовании приращения иорядка Vnp(i+i) и при формировании Vrip(i+i)4-l. а другой - в том же блоке 11 исиользуется при формировании отрицательного приращения УПр()

; 1

Блок 9 аналнза мантиссы подыитегральной функции вырабатывает сигналы

M,l+l),i + и

,(,.1)22-2-.

Первый поступает на вход блока 11 образования приращения порядка функции в качестве одного из унравляющих сигналов при формировании УПр(г+1)-|-1, второй - при формировании уПр() - 1.

Блок 10 анализа порядка подынтегральной функции вырабатывает сигналы

n,-2Q и П,.

Первый поступает на вход блока 11 образования приращения порядка подынтегральной функции в качестве одного из управляющих сигналов при формировании УПр(г+1) - 1, второй поступает на выход интегратора как сигнал переполнения ср.

Блок И образования нриращения порядка подынтегральной функции по результатам анализа ноступающих сигналов вырабатывает сигнал УПр(+1), равный +1. или -1,илиО. Эти сигналы поступают на вход блока 12 управления сдвигами мантиссы функции, на сумматор порядков 6, на выход интегратора в качестве выходного приращения порядка фупкции УПр(г+)), на реверсивные счетчики 18, 19, на вход блока 23 травления выравниванием начальных порядков.

Блок 12 управления сдвигами вырабатывает сигналы сдвига мантиссы подынтегральной

функции вправо при УПр(г+1)1 или влево при УПр(г+1) - 1. Эти сигналы поступают на блок 13 сдвига на один разряд влево - вправо мантиссы функции. По этим сигналам произойдет сдвиг (нормализация) мантиссы функции в следующем щаге интегрирования. В данном щаге происходит сдвиг мантиссы по сигналам, выработанным в предыдущем щаге интегрирования.

Приращение порядка УПр(г+1) поступает на сумматор порядков 6, где складывается с порядком функции, находящимся в регистре 2. На выходе сумматора 6 формируется новое значение иорядка Пр(г+1) функции, которое записывается в регистр 2.

Приращение порядка Vnpg(,+i) переменной интегрирования ноступает непосредственно на другой выход интегратора и на второй вход блока 23 управления выравниванием порядков. На третий выход интегратора с выхода множительного блока выдается мантисса приращения интеграла.

Режим выравнивания начальных норядков продолжается до тех пор, пока разность порядков б Про станет равной нулю, т. е. пока разность порядков б Про полностью преобразуется в поток приращений.

Выравнивание начальных порядков позволяет существенно сократить время интегрирования и тем самым сократить затраты на вычисленне.

Формула изобретения

Цифровой интегратор с плавающей запятой

по авт. св. № 510727, отличающийся тем, что, с целью повыщения быстродействия, в него введены блок выравнивания начальных порядков и блок управления выравниванием начальных порядков, причем первый вход

блока управления выравниванием начальных порядков соединен со входом переменной интегрирования интегратора, второй - с выходом блока образования приращения порядка подынтегральной функции, вы.ход регистра

порядка подынтегральной функции соединен с первым входом блока выравнивания начальных норядков, второй вход которого соединен с первым выходом блока управления выравниванием начальных порядков, третьими

входами реверсивных счетчиков и пятым выходом интегратора, третий - с первым входом приращения подынтегральной функции интегратора и со вторым входом регистра мантиссы подынтегральной функции, выход - с третьим входом блока управлепия выравниванием начальных порядков, второй выход которого соедипен с щестым выходом интегратора, остальные входы блока управления выравниванием начальных порядков соединены с

третьими выходами блоков анализа состояний счетчиков.

Источники информации, принятые во внимание нри экспертизе 1. Авторское свидетельство СССР №510727,

кл. G 06J 1/02 от 17.07.73.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой | 1973 |

|

SU510727A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Цифровой интегратор | 1976 |

|

SU651371A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1974 |

|

SU518781A1 |

| Устройство для автоматического преобразования мантиссы и порядка | 1976 |

|

SU734677A1 |

| Параллельный цифровой интегратор с пла-ВАющЕй зАпяТОй | 1977 |

|

SU828199A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

Авторы

Даты

1978-01-30—Публикация

1975-01-03—Подача