1

Изобретение относится к вычислитель.ной технике, в частности к постоянным запоминающим устройствам..

Извертьы постоянные запоминающие устройства (ПЗУ), одно из которых содержит дешифратор адреса, накопитель, регистр числа, выполненный на триггерах, подключенных к выходам накопителя и шину сброса триггеров. С целью упрощения, повышения надежности работы и быстродействия в накопителях известных постоянных запоминающих устройств разряды с преобладающим количеством единиц представляют в обратном коде l. Наиболее близким к изобретению техническим решением является ПЗУ, содержащее первый дешифратор адреса, выходы которого Соединены со взсодами накопителя, выходы накопителя через эЯёменты НЕ подсоединены .к первым Ёхо- дам первых элементов И, ко вторым входам которых подключены выходы cooiw ветствующих первых элементов ИЛИ выходь первых элементов И соединены с

первыми входами со вётЬтвующих вторыя элементов ИЛИ, выходы которых (подсое- динены ко входам регистра числа 2. Однако в известных постоянных запоминающих устройствах количество элементов связи и число проводов в запоминающих трансформаторах может быть уменьшено не более, чем в два раза. Это не позволяет производить дальнейшее упрощение накопителя, повышение надежности работы и быстродействие устройств на основе метода поразрядного обратного кодирования.

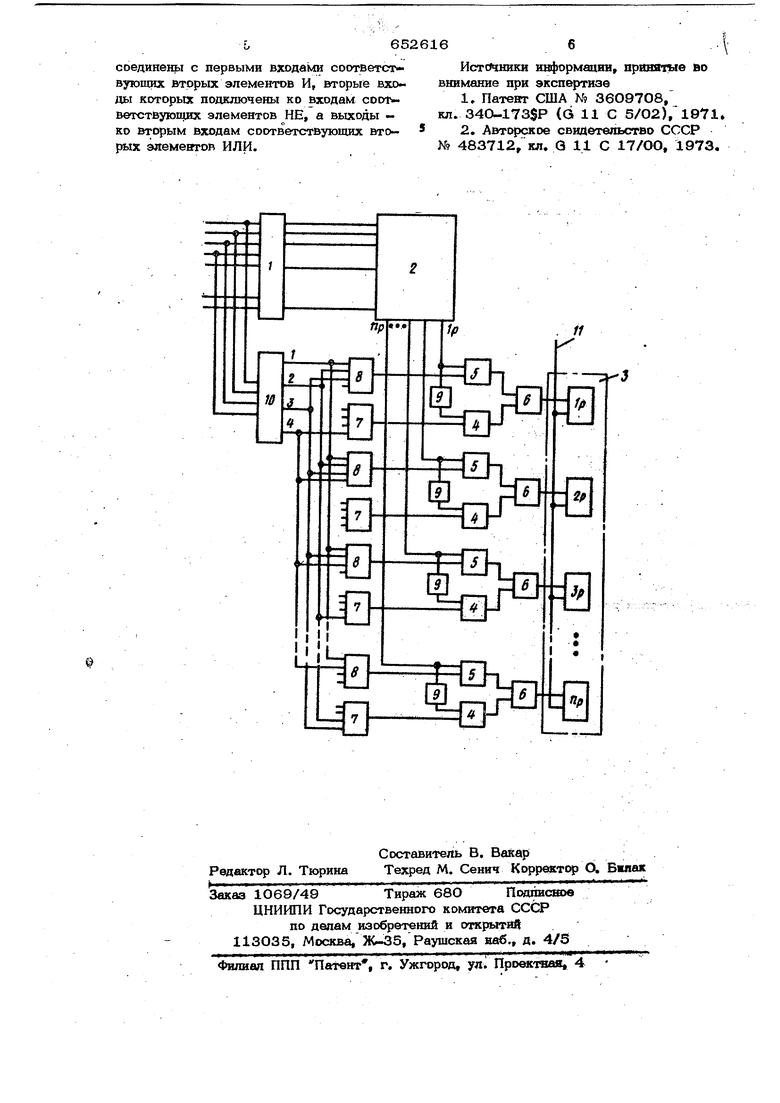

Целью изобретения является повьпиение надежности. В предложенном устройстве это достигается тем, что оно содержит Второй дешифратор адреса, вторые элементы И и третьи элементы ИЛИ по числу выходов накопителя, при этом входы второго дешифратора.адреса соединены с соответствующими входами первого дешифратора адреса, в выходы- со входами первых и третьих элементов ИЛИ, выходы третьих элементов ИЛИ с1 эдйнёны с первыми BXOAakiH соответствукшшх Вторых элементов И . BXI ды кот&рых noflknioMemi ко входам соот ветствукяцих элементов НЕ, а выходы ко вторым ,f XDaaM ссоуветствующих втгорых элементов ИЛИ. На Чертеже представлеиа схема предложенного устройства. Оно содёр(жит первый дешн4чаатор адреса 1, нак«й1 геяь 2t регистр числа 3,.первые эпементы И 4, вторые элементны И 5, первые эл. менты ИЛИ 6, элементы ИЛИ 7, -Еретьи элементы ИЛИ 8, элементы НЕ 9 второй дешифратор адреса Юн шину c6p са И. На чертеже прнЬедёЮ) свази Между узлами устройства для случая, когда вв- формадионный масснв для хранЁ ива в устройстве условно разделен на четыре равные части, например: № числа 1 2 3 п Р Р Р Р 10100 21 О О О В известных устройствах прнмененне поразрядного) обратного кодирования данного массива не дает преимуществ. В предложенном устройстве в каждой части массива разряды с преобладающим количеством единиц в накопителе записан обратным кодом: № числа В соответствии с кодом адреса на входах первого дешифратора адреса 1 из накопителя 2 считывается код числа, например, третьего: О1О...О. Входы второго Дешифратора адреса 1О принимают два старших разряда кода адреса. При выборе третьего числа на втором выходе второго дешифратора адреса 1О устанавливается уровень логической , кото- рьй поступая через соответствуюпдае первые и третьи элементы ИЛИ 6 и 8, разрешает на входах вторых элементов И 5 1-го и 2-го разряда вьадачу мации из накопителя 2 прямым кодом. Информация в 3-м, и Ц-м разрядах выдается обратным кодом, так как уровень логической в этих разрядах поступает на первые элементы И 4, к которым выходы накопителя 2 подключены через элементы НЕ 9. Считанные из накопите ля сигналы далее поступают через первые, элементы ИЛИ 7 на единичные входы триггеров регистра числа 3, предварительно сброшенных в О сигналом сброса на шнне 11. В регистре числа 3 фиксируется исходный код 011,... Примененне предложенной схемы постоянного запоминающего устройства позволяет существенно уменьшить количество элементов связи в полупроводниковых постоянных запоминаюших устройствах и количество кодовых проводов в запоминающих трансформаторах постоянных запоминаюших устройств трансформак торного типа. Упрощенна накопителей повышает надежность работы устройства и его быстродействие. Формула изобретения Постоянное запоминающее устройство содержащее первый дешифратор адреса, выходы которого соединены со входами накопнтеля, вйходы накопителя через элементы НЕ подсоединены к первым входам первых элементов И, ко вторым входам которых подкшочены выходы соответствующих первых элементов ИЛИ, выходы первых элементов И соединены с первыми входами соответствующих вторых элементов ИЛИ, выходы которых подсоединены ко входам регистра числа, отличающееся тем, что, с целью повьпиення надежности устройства оно содержит второй дешифратор адреса, вторые элементы И н третьи эяегленты {ШИ по числу выходов накютителя, при этом входы второго дешифратора адреса соединень с соответствующим входами первого дешифратора адреса, а выходы - 00 входами первых н третьих элементов ИЛИ, вых(Х1Ы третьих элементов ИЛИ

соединень с первыми входаЦи соответствующих вторых элементов И, вторые входы которых подключены ко входам coot, ветствуюших элементов НЕ, а выходы ко вторым входам соответствующих вторых элемеетов ИЛИ.

информации, принятые во внимание при экспертизе

1.Патеет США N9 3609708,

кл. 340-173SP (О И С 5/02)/1071.

2.Авторское свндетельство СССР

№ 483712/кл. Q 11 С 17/ОО, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с исправлением ошибок | 1978 |

|

SU686085A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU972600A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Микропрограмммное устройство управления для цифровой вычислительной машины | 1967 |

|

SU482743A2 |

| Постоянное запоминающее устройство | 1980 |

|

SU1080214A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Запоминающее устройство с автономным контролем | 1978 |

|

SU780049A1 |

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841061A1 |

| Запоминающее устройство | 1975 |

|

SU639016A1 |

| Полупостоянное запоминающее устройство | 1976 |

|

SU690562A1 |

f

Авторы

Даты

1979-03-15—Публикация

1976-11-04—Подача