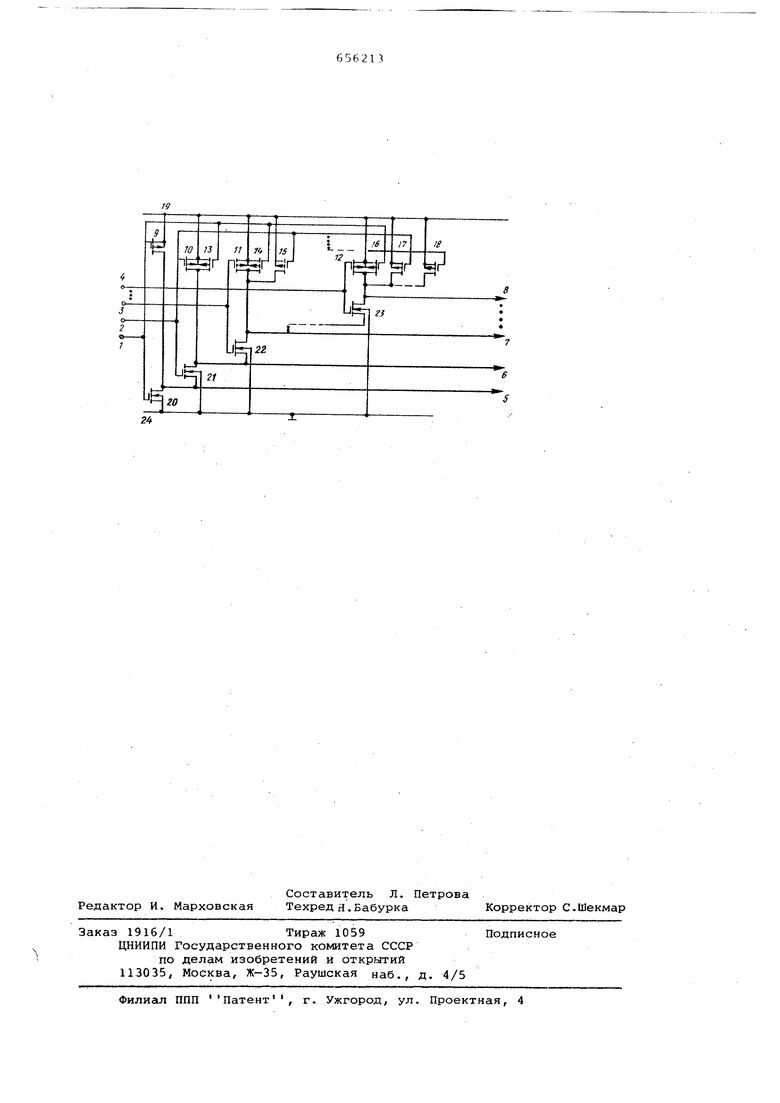

Изобретение относится к вычислительной технике, электротехнике, авт матике и, в частности, может исполь зоваться в интегральных схемах и БИС на дополняющих МДП-транзисторах. Известны логические элементы И-НЕ на дополняющих МДП-транзисторах, содержащие пары дополняющих Пи рканальных транзисторов, в которых сток п-канального транзистора подключен к стоку р-канального транзистора и к логическому выходу элемента, затвор п-канального транзистора подключен к затвору р-канально ного транзистора и к логическому вхо ду элемента, истоки и подложки Р канальных транзисторов всех пар подключены к шине питания, истоки и подложка П-канального транзистора первой пары и подложки п-канальных транзисторов остальных пар подключены к общей шине, истоки И-каналь ных транзисторов второй и последующих пар подключены к выходу предыдущей пары И. Недостатком известных элементов является искажение передачи уровня напряжения логической единицы при некоторых наборах входных переменных Известен элемент И-НЕ, содержащий пары дополняющих Пи р-канальных транзисторов, число которых равно числу входных логических переменных, в каждой паре исток и подложка р-канального транзистора подключены к шине питания, сток р-канального транзистора подключен к стоку Пканального транзистора и к соответствующему логическому выходу элемента; затвор р-канального транзистора подключен к затвору п-канального транзистора и к соответствующему логическому входу элемента: исток и подложка П-каиального транзистора первой пары и подложки и-канальных транзисторов остальных пар подключены к Общей шине, истоки ц-канальных транзисторов второй и последующих пар подключены к логическому выходу предыдущей пары. Элемент содержит дополнительные транзисторы, подключенные между выходом данной пары и выходом последующей пары, причем число дополнительных параллельно включенных транзисторов соответствует номеру данной пары, затвор первого и каждого из последующих дополнительных, параллельно включенных транзисторов подключен к логическому входу первой и последующих пар дополняющих транзисторов, предшествующих данной паре. Дополнительные транзисторы предназначены для улучшения передачи уровни напряжения логической единицы при некоторых наборах входных переменных 2). Недостаток элемента в том,, что до полнительные транзисторы образуют по следовательную цепь при передаче уровня напряжения и , что требует увеличения размеров дополнительных транзисторов при интегральном исполнении элементов пропорционально числу логических входов. Это приводит . к увеличению площади, занимаемой элементом на кристалле, и снижению быстродействия. Цель изобретения - уменьшение пло щади элемента при интегральном испол нении и повышение быстродействия. Для достижения .поставленной цели вЛогическом элементе И-НЕ, содержащем пары дополняющих П.и р-канальных транзисторов, число которых равно числу входных логических переменных, в каждой паре исток и подложка р-канального транзистора подключены к шине питания, сток рканального транзистора подключен к стоку П-канального транзистора и к соответсЭ-вующему логическому ЁГЫХО ду элемента, затвор /р-канального транзистора подключён к затвору П канального транзистора и к соответствующему логическому входу элемент исток и подложка h-канального тран зистора первой пары и подложки Цканальных транзисторов остальных па подключены к. общей шине, истоки И канальных транзистороввторой и последующих пар подключены к логическому выходу предыдуб1ей пары, а также содержащий дополнительные .Р канальные тран1зисторы в каждой паре начиная со второй, число которых равно числу пар дополняющих транзисторов, предшествующих данной,. затЁор первого и каждого :, следующе дополнительного транзистора подключен соответственно к логическому входу первой я последующих пар допо няющих транзисторов, предшествук)щих данной паре, истоки и подложки до полнительных р-канальных транзисто ров подключены к шине питания, а стоки - к логическому выходу, соответствующему данной паре дополняющих транзисторов, . На чертеже представлена элЬктрическая принципиальная схема элемента И-НЕ.. Устройство содержит логические входы 1--4 элемента, логические выхо 5-8 элемента.ЧИСУ1О входов и выходов элемента соответствует числу пар до папняаощих Пир -канальных транзист ров и равно т.Истоки и подложки дополняющих р-канальных транзисторов 9-12, соответственно,первой, второй, третьей и Гп-ой пары и истоки и подложки дополнительных Р-канальных транзисторов 13-13 подключены к шине 19 питания, сток транзистора 9 подключен к стоку дополняющего Пканального транзистора 20 первой пары, к выходу 5 и к истоку дополняющего П-канального транзистора 21 второй пары, сток транзистора 10 подключен к стокам транзисторов 13 и 21, к выходу б и истоку дополняющего П-канального транзистора 22 третьей пары, сток которого подключен к стокам транзисторов 11, 14, 15, к выходу 7 и к истоку дополняющего П-канального транзистора последующей пары (при m 4 к истоку транзистЬра 23 m -ой пары). Сток дополняющего П-канального транзистора 23 т-ой пары подключен к выходу 8 и к стокам транзисторов 12,1б-18у Исток и подложка транзистора 20 первой пары и подложки транзисторов 21-23 остальных пар подключены к общей шине 24. В каждой .паре затворы дополняющих Ц и р-канальных транзисторов (20 и 9, 21 и 10, 22 и 11, 23 и 12) подключены, соответственно, к логическим входам 1-4, Затворы дополнительных тгранзисторов 13,14, 16 подключены к логическому входу 1, затворытранзисторов 15, 17 - к логическому входу 2, затвор транзистора 18 подключен к логическому входу предшествующей ( пары. Устройство работает следукицим образом, На каждом из выходов 5-8 последовательно выполняются функции YI, от соответствующих входных /логических переменных Хт , где i- 1.2,3,. га. V S Xj ; V i . V V - ч ( ГЧ Ч . I «2 , зд Особенность работы элемента состоит в следующем. Если бы отсутст-. вовали дополнительные транзисторы, например, отсутствовал бы транзистор 13, то при йоступлении на вход 1 напряжения логического нуля U° , а на вход 2 напряжения логической единицы U - на выходе 6 второй пары должен был бы .установиться уровень напряжения U , близкий по величине к потенциалу шины питания. Однако, на выходе б напряжение будет меньше напряжения питания на величину порогового напряжения транзистора 21, через который уровень напряжения логической единицы с выхода 5 поступает на выход б. Очевидно, если элемент имеет m входов, то при поступлении напряжения логического нуля на первый логический вход и напряжения логической единицы на остальные (га -1) входы, (т -1) П-канальных транзисторов окажутся

включенными последовательно между выходами первой и т-ой пары. Поэтому напряжение на выходе m -ой пары будет отличаться от напряжения на выходе первбй пары на величину (т -1) U пор. П, где и пор. г-пороговое напряжение ц-канального транзистора. Если предположить, что на выходе 5 напряжение равно напряжению питания Е, то на выходе 8

.п. Если Ugbin-}- допустимому минимальному уровню напряжения логическо единицы, то предельное число входов логического элемента Из (1) следует, что, если/Е-идопК XUnop.h то практически построить логическую схему нельзя. Чтобы устранить этот недостаток,включены дополнительные транзисторы . Например, если на входе 1 напряжение и°, а на вгсоде 2-и , то открывается, р канальный транзистор 13 и на выходе 6устанавливается уровень напряжения логической единицы такой же, как и н выходе 5. Отметим, что время установления на выходах 6 и 5 будет прак тически одинаковым, если транзисторы 9 и 13 имеют одинаковые размеры и к выходам 5 и б подключены одинаковые емкостные нагрузки. Так как транзистор 13 предназначе для установления на выходе б уровня напряжения U при одной кoмбинaцF и входных сигналов, то этот транзистор может иметь минимальные размеры Аналогичные функции выполняют и дополнительные транзисторы, подключенные к выходам других пар. Например, транзистор 14 обеспечивает уровень напряжения и на выходе 7при , ивч5 и, транз,истор 15 --при и° и Иа конец, оба транзистора 14 и 15 откры ты при Ug Ug j JTsce дополнительные транзисторы могут иметь минималь ные размеры, так какбыстродействие элемента будет ограничено только вре менем установления уровня напряжения и° на выходе 8 при переключениия напряжения на входе 1 из состояния и в состояние U и при уровне напр жения, равном и на всех остальных входах.

Таким образом, все дополнительные транзисторы в предложенном элементе имеют при интегральной реализации значительно меньшие размеры, так как на них не накладываются никакие дополнительные ограничения. Предложенное включение дополнительных транзисторов обеспечивает повышение быстродействия элемента при усзтановлении на выходах уровня напряжения логической единицы. изобретения Логический элемент И-НЕ, содержащий пары дополняющих ц и р -канальных транзисторов, число которых равно числу входных логических пере 5енных, в казвдой паре исток и подложка р-канального транзистора подключены к шине питания, сток р канального транзистора подключен к стоку п-канального транзистора .и к соответствующему логическому выходу элемента, затвор р-канального транзистора подключен к затвору Цканального .транзистора и к соответствующему логическому входу элемента, исток и подложка И-канального транзистора первой пары и подложки П-канальных транзисторов остальных пар подключены к ое,(- шине, истоки пканальных транзисторов второй и последующих пар подключены соответственно к логичес ому выходу предыдущей пары, а также, содержащий дополнительные р-канальные транзисторы в каждой паре, начиная со второй, число которых разно числу пар дополняккаих транзисторов, предшествующих данной, затвор первого и каждого следующего дополнительного транзистора подключен соответственно к логическому входу первой и последующих пар дополнительных транзисторов, предшествующих данной паре, отличающийся тем, что, с целью уменьшения площади при интегральном исполнении и повышении быстродействия, .. истоки и подложки дополнительных р-канальных транзисторов подключены к шине питания, а :токи - к логическому выходу, соответствующему данной паре дополняющих транзисторов. Источники информации, принятые во внимание при экспертизе 1.Патент США 3769523, кл. 307-205, 1971. 2.Патент Великобритании 1300495, кл. Н 3 Т, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент | 1977 |

|

SU627593A1 |

| Логический элемент или-не | 1977 |

|

SU656214A1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Логический элемент | 1977 |

|

SU627594A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU1005185A1 |

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Микромощный инвертор на дополняющих мдп-транзисторах | 1980 |

|

SU898620A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1089761A1 |

Авторы

Даты

1979-04-05—Публикация

1977-12-14—Подача