подключенные между выходом данной пары и выходом последующей пары, причем число дополнительных параллельно включенных транзисторов соответствует номеру данной пары. Затвор первого и каждого из последующих дополнительных параллельно включенных транзисторов подклк чен, соответственно, к логическому входу первой и последующ{к пар дополняющих транзисторов, предшествующих данной паре. Дополнительные транзисторы предназначены для улучшения передачи уровня напряжения логического нуля -И - при некоторых наборах входных переменных |2 Недостаток элемента в том, что дополнительные транзисторы образуют последовательную цепь при передаче уровня напряжения логического нуля, причем размеры дополнительных транзисторов при интегральном исполнении элемента увеличиваются пропорционально числу последовательно соединенных транзисторов, т.е. пропорционально числу входов элемен та. Это приводит к увеличению площади элемента на кристалле и снижению бьютродействия.

Цель изобретения - уменьщение площа ди при интегральном исполнении и повышение быстродействия.

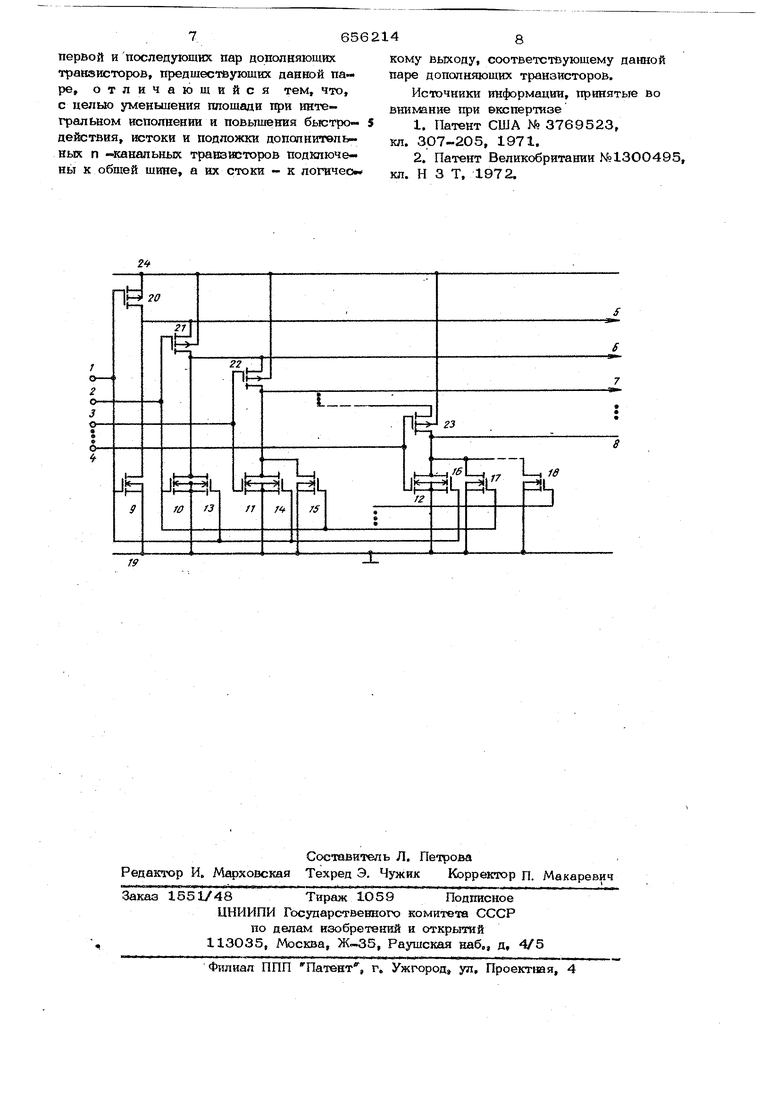

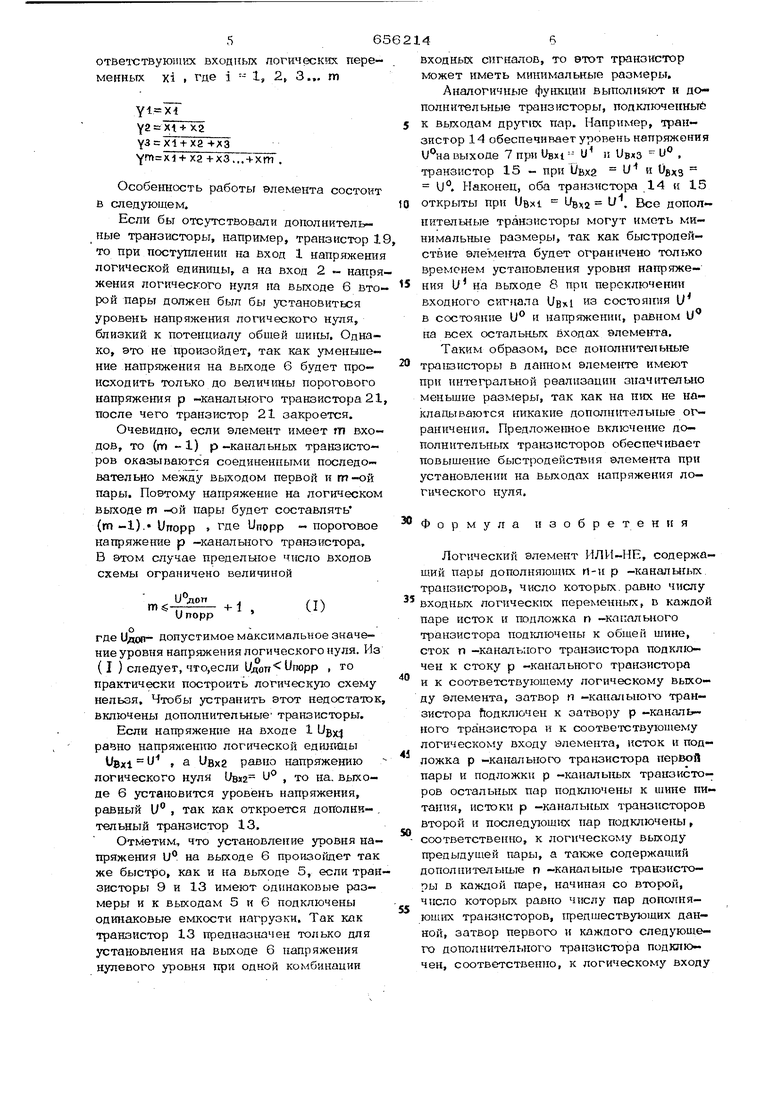

Для достижения поставленной цели в логическом элементе ИЛИ-НЕ, содержащем пары дополняющих пир -канальных транзисторов, число которьгх равно числу входных логических переменных, в каждой паре исток и подложка п -канального транзистора подключены к общей щине, сток п -каналытого транзистора подключен к стоку р -канального транзистора и к соответствующему выходу элемента, затвор г -канального трагезистора подключен к затвору р -канального транзистора и к соответствующему логическому входу элемента, исток и подложка р -канального транзистора первой пары и подложки р -канальных транзисторов остальных пар подключены к шине питания, истоки р -канальных транзисторов второй И последующих пар подключены, соответственно, к логическому выходу пре- дыдушей пары, а также содержащем дополнительные п -канальные транзисторы, под1шюченные к выходу каждой пары, tra- Чйная со второй, число которых равно числу пар дополняющих транзисторов, предшествующих данной, затвор первого и каждого следующего дополнительного транзистора, подключен, соответственно, к логическому входу первой и поеледуюняющего р -канального транзистора 21 второй пары, сток траюистора 1О подключен к стокам транзтеторов 13 и 21, к выходу 6 и к истоку дополняющего р -канального транзистора 22 третьей пары сток которого подключен к стокам транзисторов 11, 14, 15, к выходу Тик истоку дополняющего р -канального транзистора последующей пары (при m 4 к истоку транзистора 23 m -ой пары). Сток дошлняющего р -канального транзистора 23 in -ой пары подключен к Выходу 8 и к стокам транзисторов 12, 16-18. Исток и подложка транзистора 2О первой пары и подложки транзисторов 21- 23 остальных пар подтшючены к шине 24 пигания. В каждой паре затворы дополняющих п-и р -канальных транзисторов (9 и 2О, 10 и 21, 11 и 22, 12 и 23) подключены, соответственно, к логическим входам 1-4. Затворы дополнительных транзисторов 13,14,16 подключены к логическому входу 1, затворы транзисторов IS, 17 - к логическому входу 2, затвор транзистора 18 подключен к логическому входу предшествующей (т -1)-ой пары.

Устройство работает следующим образом

На каждом из выходов 5-8 последователкю выполшпотся фушшии yi от со- щих пар дополняющих транзисторов, предществующих данной паре, истоки и подложки дополнительных п -канальных транзисторов подключены к общей щине, а их стоки - к логическому выходу, соответствующему данной паре дополняющих транзисторов. На чертеже представлена электрическая принципиальная схема предложенного элемента ИЛИ-НЕ. Логический элемент ИЛИ-НЕ имеет .логические входы 1-4 элемента, логические выходы 5-8 элемента. Число входов и выходов элемента соответствует числу пар допопняюших п-и р -канальных транзисторов и равно m . Истоки и подложки дополняющих п -канальных транзисторов 9-12, соответственно, первой, второй, третьей к т -он пары и истоки и подложки дополи ительньк л -1санальных транзисторов 13-18 подключены к общей щине 19, сток транзистора 9 подключен к стоку дополняющего р -канального транзистора 20 первой пары, к выходу 5 и к истоку дополOTBeiCTByroniKx входных логических пере где i 1, 2, 3.„ m менных xi уг хГГхг Y-3 X1-fX2 -t-ХЗ хз+хз... + xm . Особенность работы элемента состои в следующем. Если бы отсутствовали дополнитель, ные транзисторы, например, транзистор то при поступлении на Вход 1 напряжен логической единицы, а на вход 2 напр жения логического нуля iia выходе 6 вт рой пары должен был бы установиться уровень напряжения логического нуля, близкий к потенциалу обшей шины. Одна ко, это не произойдет, так как уменыие ние напряжения на выходе 6 будет происходить только до величины порогового иапряжего1я р -канального транзистора 2 после чего транзистор 21 закроется. Очевидно, если элемент имеет m вхо дов, то (т - 1) р-канальных транзисторов оказываются соединенными последовательно между выходом первой и т-ой пары. Поэтому напряжение на логическо Выходе m -ей пары будет составлять (т -1).« Unopp тое Unopp - пороговое напряжение р -канального транзистора, В этом случае предельное число входов схемы ограничено величиной где Цдоп- допустимое максимальное значение уровня напряжения логического нуля. Из (I ) следует, что,если идотт Unopp , то практически построить логическую схему нельзя. Чтобы устранить этот недостато включены дополнительные транзисторы, Если напряжение на входе 1 Ugx-j равно напрямсештю логической единицы вх и , а Uflxa равно напряжению логического нуля UB« , то на, выходе 6 установится уровень напряжения, равный и , так как откроется дополнительный транзистор 13. Отметим, что установление уровня на пряжения и на выходе 6 произойдет так же быстро, как и на выходе 5, если тран зисторы 9 и 13 имеют одинаковые размеры и к выходам 5 и 6 подключены одинаковые емкости нагрузки. Так как транзистор 13 предназначен только для установления на выходе 6 напряжения нулевого уровня при одной комбинации входных ст1гналов, то этот транзистор может иметь минимальные размеры. Аналогичные функции выполняют и дополнительные транзисторы, подключенный к вьгходам других пар. Например, транзистор 14 обеспечивает уровень напряжения выходе 7 при U н Увхз U . транзистор 15 - при Овха U и Овхз и°. Наконец, оба транзистора 14 и 15 открыты при UBXI L/Bxa . Все дополнительные транзисторы могут иметь минимальные размеры, так как быстродействие элемента будет ограничено только временем установления уровня напряжения и на выходе 8 при переключении входного сигнала из состоя1гля U в состояние U и напряжении, равном U на всех остальных Входах элемента. Таким образом, все дополнительные транзисторы в да1гаом элементе имеют при ин1егральной реализации значительно меньшие размеры, так как на них не накладываются никакие дополнительные oi раничения. Предложега ое включение дополнительных транзисторов обеспечивает повышение быстродействия элемента при установлении на выходах напряжения логического нуля. Формула изобретения Логический элемент ИЛИ-НЕ, содержащий пары дополняющих п-и р -канальных транзисторов, число которых.равно числу входных логических переменных, в каждой паре исток и подложка п -канального транзистора подключены к общей шине, сток п -канального транзистора подключен к стоку р -каначьного транзистора и к соответствующему логическому выходу элемента, затвор п -канального транзистора йодключен к затвору р -канального транзистора и к соответствующему логическому входу элемента, исток и подложка р -канальносх) транзистора первой пары и подложки р -канальных транзисторов остальных пар подключены к иише питания, истоки р -канальных транзисторов второй и последутоших пар подключены, соответственно, к логическому выходу предыдущей пары, а также содержащий дополнителы1ые п -канальные транзисторы в каждой паре, начиная со второй, число которых равно числу пар дополняющих транзисторов, предшествующих данной, затвор первого и каждого следующего дополнительного транзистора подключен, соответственно, к логическому входу 765 первой и последующих пар дополняющих транзисторов, предшествующих данной паре, отличающийся тем, что, с целью 5гменьшения площади при инте гральном исполнении и повыщения бьютродействия, истоки и подложки дополнительных п -канальных травзисторов подключены к общей щине, а их стоки - к логичес 4 кому выходу, соответствующему данной паре дополняющих транзисторов. Источники информации, принятые во внимание при вкспертизе 1.Патент США № 3769523, кл. 307-205, 1971. 2.Патент Великобритании №13О0495, кл. Н 3 Т, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический элемент и-не | 1977 |

|

SU656213A1 |

| Логический элемент | 1977 |

|

SU680173A1 |

| Логический элемент | 1977 |

|

SU627593A1 |

| Формирователь с тремя состояниями на выходе | 1983 |

|

SU1149399A1 |

| Логический элемент | 1977 |

|

SU627594A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| Логический элемент или-не- на мдптранзисторах | 1977 |

|

SU692089A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Преобразователь уровней напряжения | 1984 |

|

SU1167725A1 |

| Элемент с тремя состояниями | 1981 |

|

SU1003349A1 |

Авторы

Даты

1979-04-05—Публикация

1977-12-14—Подача