(54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ | 1992 |

|

RU2041563C1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| Делитель частоты с регулируемым коэффициентом деления | 1982 |

|

SU1051732A1 |

| Программируемый делитель частоты следования импульсов | 1981 |

|

SU993481A1 |

| Синтезатор частот | 1986 |

|

SU1394434A1 |

| Датчик сигнала ошибки | 1984 |

|

SU1210201A1 |

| Делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1054905A1 |

| Цифровой синтезатор изменяющейся частоты | 1985 |

|

SU1298836A1 |

| Цифровой синтезатор частоты | 1987 |

|

SU1515364A1 |

| Делитель частоты с переменным коэффициентом деления | 1975 |

|

SU660262A1 |

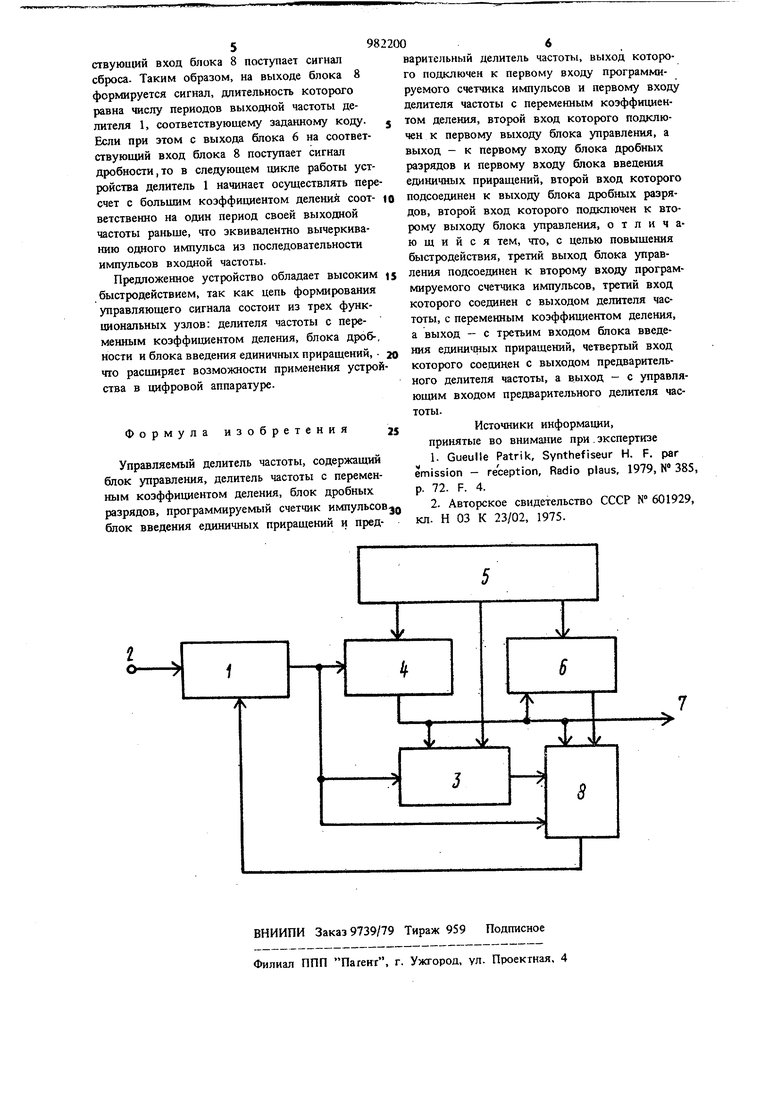

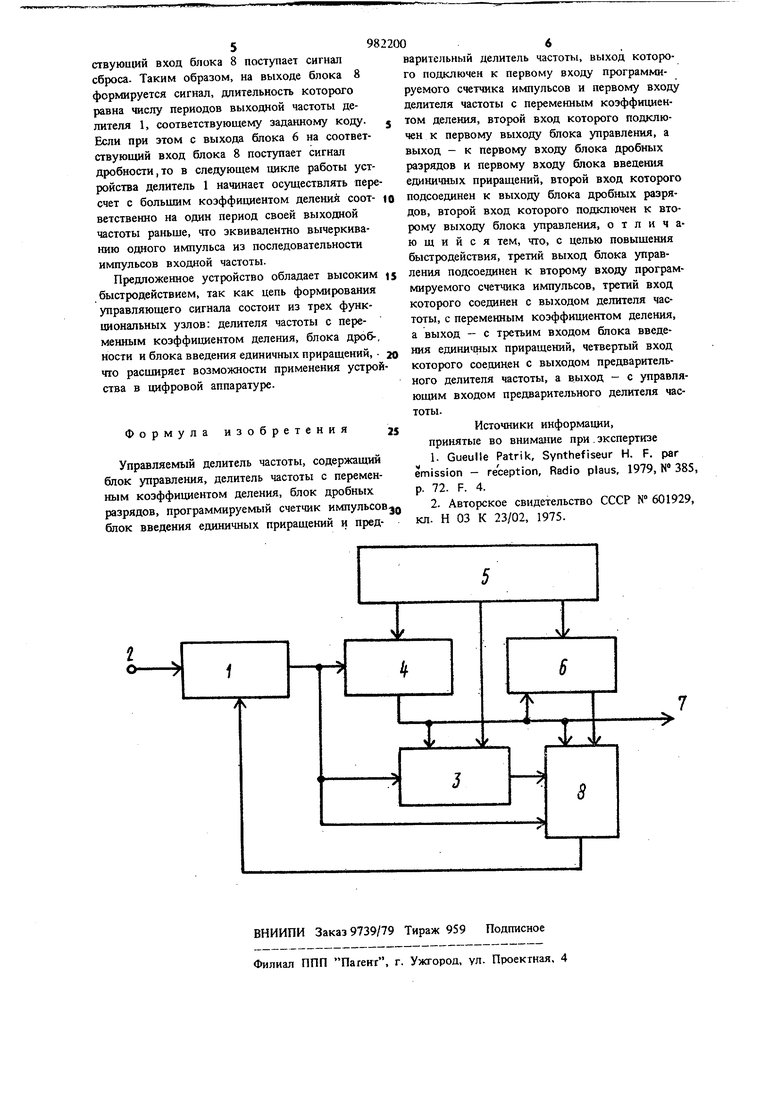

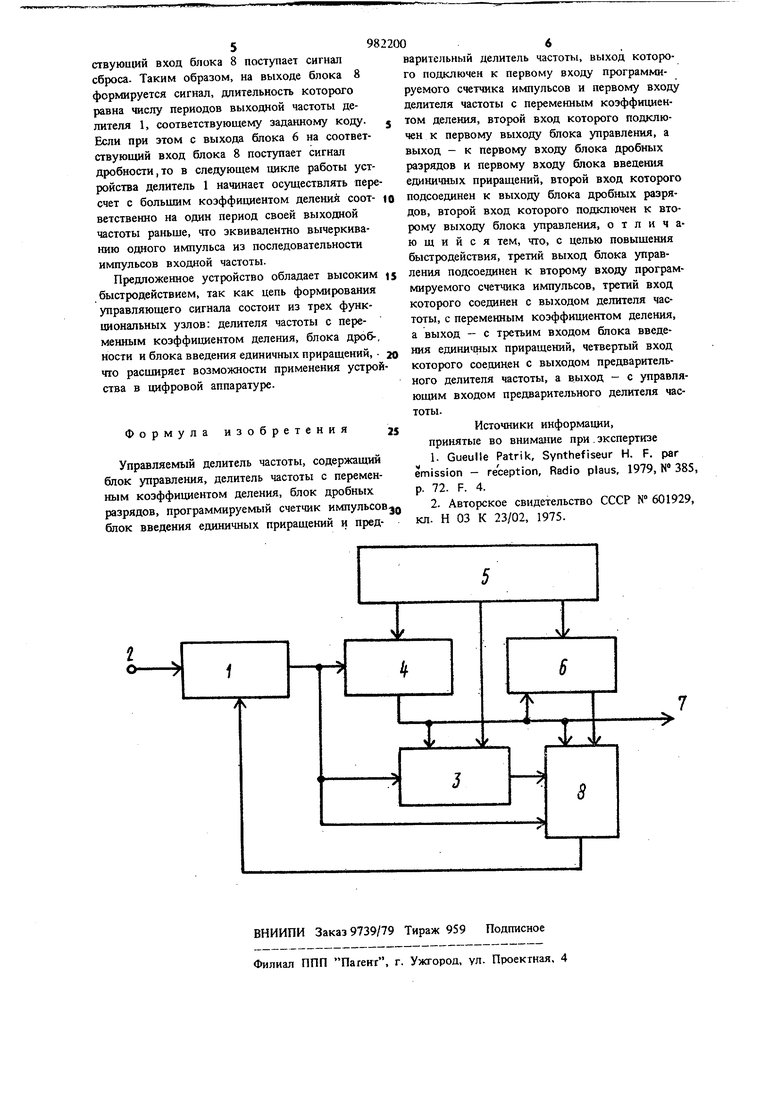

Изобретение относится к импульсной технике и предназначено для использования в устройствах цифросинтеза частот. Известен управляемьш делитель частоты, содержащий предвартпге;аный делитель частоты вход которого является входом устройства, а выход соединен с первыми входами програ мирующего счетчика и делитель частоты с переменным коэффициентом деления, вторые входы которых подключены к кодирующим шинам, вход делителя частоты с переменным козффициентом деления соединен с выходом устройства и третьим входом программирую щего счетчика, выход которого соединен с управляющим входом предварительного делителяг частоты Ц. Недостатком зтого устройства являются низкие функциональные возможности, так ка оно не позволяет получать дробный коэффициент деления. Наиболее блнзким к предлагаемому по технической сущности является делитель частоты, содержащий предварительнь1Й целитель частоты, выход которого соединен с первыми входами П{юграммирую1цего счетчика и делителя частоты с переменным коэффициентом деления, второй вход которого подключен к первому выходу блока управления, второй выход блока управления соединен с первым входом блока Дробных разрядов, второй вход которого соединен с выходом делителя частоты с переменным козффициентом деления, выходом блока дробных разрядов соединен с первым входом блока введения единичных приращений, второй вход которого подаслю«йн к выходу делителя часто1ы с переменным коэффициентом деления, кроме того, третий вход блока введения единичных П}жращений подключен к третьему выходу блока управления, а выход соединен с вторым входом программируемого счетчика, выход которого соединен с управляющим входом предварттельного делителя частоты 2. Недостатком известного устройства является гизкое быстродействие, так как цепь, формирующая управляющий сигнал для реализации рробаал части коэффициента деления, состоит из- четырех последовательно соединен39ных функциональных узлов: делителя частоты с переменным коэффициентом деления, блока дробных разрядов, блока введения единичных приращений и программируемого счетчика. Цель изобретения - повышение быстродействня устройства. Поставленная цель достигается тем, что в управляемом делителе частоты, содержащем блок управления делитель частоты с перемен ным коэффициентом деления, блок дробных разрядов, программируемый счетчик импульсо блок введения единичных приращений и пред варительный делитель частоты, выход которого подключен к первому входу программи емого счетчика импульсов и первому входу делителя частоты с переменным козффициен том деления, второй вход которого подключен к первому выходу блока управления, а выход - к первому входу блока дробных разрядов и первому входу блока введения единичных приращений, второй вход которого подсоединен к выходу блока дробных разрядов, второй вход которого подключен к второму выходу блока управления, третий выход блока зшравления подсоединен к второму входу программируемого счетчика импул сов, третий вход которого соединен с выходом делителя частоты с переменным коэффициентом деления, а выход - с третьим входом блока введения единичных приращени четвертый вход которого соединен с выходом предварительного делителя частоты, а выход - с управляющим входом предварител ного делителя частоты. На чертеже представлена структурная схема управляемого делителя частоты. Управляемый делитель частоты содержит предварительный делитель частоты I, вход 2 устройства, программируемый счетчик 3 импульсов, делитель частоты 4 с переменным коэффициентом деления, блок 5 управления, блок 6 дробных разрядов, выход устройства 7, блок 8 введения единичных приращений. Блок 8 введения единичных- приращений пред ставляет собой триггер с логикой стробирования на входе. Управляемый : делитель частоты работает следующим образом. Импульсы входной частоты поступают через вход 2 устройства на вход предварительного делителя 1 с двумя коэффициентами деления выходной сигнал делителя 1 частоты служит для тактирования счетчика 3, делителя 4 и блока 8. Выходной сигнал делителя 4 поступает на выход 7 устройства, на вход счетчика 3, для установки исходного состояния, на вход блока 6 для формирования сигнала дробности в следующем цикле деления и, наконец. на вход блока 8 для его запуска в случае наличия сигнала дробности, поступившего от блока 6 в предьщущем цикле работы устройства. Выходной сигнал счетчика 3, возникающий после установки счетчика в состояние, отличное от нуля, поступает на соответствующий вход блока 8 для его запуска в случае отсутствия сигнала дробности, либо для подтверждения запуска в случае наличия сигнала дробности. Выходной сигнал блока 8 определяет режим работы делителя 1 с меньшим коэффициентом деления либо с коэффициентом пересчета на единицу большим. С выхода блока 5 управления поступают коды: на соответствующий вход счетчика 3 - код младших разрядов целой части заданного коэффициента деления устройства, на вход делителя 4 код старших разрядов целой части коэффициента деления, на вход блока 6 - код дробной части коэффициента деления устройства. Если в соответствии с заданным коэффициентом : деле1шя устройства младшие разряды целой части коэффициента деления равны нулю, а значит и код, поступающий на вход счетчика 3, равен нулю, то блок 8 не запускается и делитель 1 постоянно работает с меньшим коэффициентом деления. Если при этом с выхода блока 6 в некотором текущем цикле деления поступает сигнал дробности, то с приходом последнего выходного импульса делителя 1 текущего цикла деления устройства запускается блок 8 и на его выходе формируется сигнал, длительность которого равна одному периоду выходной частоты делителя 1. В результате в следующем цикле деления делитель 1 работает в течение первого периода своей выходной частоты с большим коэффициентом деления, что эквивалентно вычеркиванию одного импульса из последовательности импульсов входной частоты. Если в соответствии с заданным коэффициентом деления младшие разряды целой части коэффициента деления не равны нулю, а значит и код, поступающий на вход счетчика 3, не равен нулю, то выходной импульс делителя 4, совпадающий по времени с последним импульсом делителя 1 соответствующего цикла деления устройства, устанавливает счетчик 3 в исходное ненулевое состояние и на его выходе возникает сигнал разрешения запуска блока 8. Первый выходной импульс делителя 1 следующего цикла деления запускает блок 8. Через число выходных импульсов делителя 1, равное коду младщего разряда целой части заданного коэффициента деления, счетчик 3 устанавливается в нулевое состояние и с его выхода на соответ

Авторы

Даты

1982-12-15—Публикация

1981-05-19—Подача