Изобретение относится к запоминакхдим устройствам.

Известна ячейка памяти для буферного регистра, построенная на основе трехстабильного триггера на элементах И-2ИЛИ-НЕ, причем в этой схеме входы первого элемента И каждого из трех элементов И-2ИЛИ-НЕ соединены с выходами двух других элементов И-2ИЛИ-НЕ 11.

Недостатком этой ячейки является невысокое быстродействие.

Наиболее близким техническим решением к данному изобретению является ячейка памяти для буферного регистра, содержащая три элемента И-ИЛИ-НЕ, включенные по схеме трехстабильного триггера так, что входы первого элемента И кгокдого элемента И-ИЛИ-НЕ соединены с выходами двух других элементов И-ИЛИ-НЕj и шесть входных шин, причем первая шина соединена с входами первого и третьего элементов И-ИЛИ-НЕ, вторая - с входами первого и второго, третья - с входом первого, а остальные шины с входами второго и третьего элементов И-ИЛИ-НЕ 2.

. Однако в буферном регистре, собранном из ячеек памяти указанного

типа каждая порция информации продвигается от первой ячейки к последней, причем время, через которое информация появляется на выходе регистра, зависит как от собственных (реальных) Задержек элементов последнего, так и от его заполнения информацией, что делает невозможной параллельную запись информации в регистр, так как

10 одновременно с записью информации в какую-либо ячейку по шинам параллельной записи в ту же ячейку может поступить порция информации по шинам сдвига из предыдущей ячейки,

15 что нарушает правильность работы регистра. Отсутствие возможности параллельной записи в ячейку ограничивает область ее применения.

Цель изобретения - расширение об20ласти применения ячейки памяти за счет обеспечения возможности параллельной записи информации.

Поставленная цель достигается тем, что в ячейку памяти для буферного

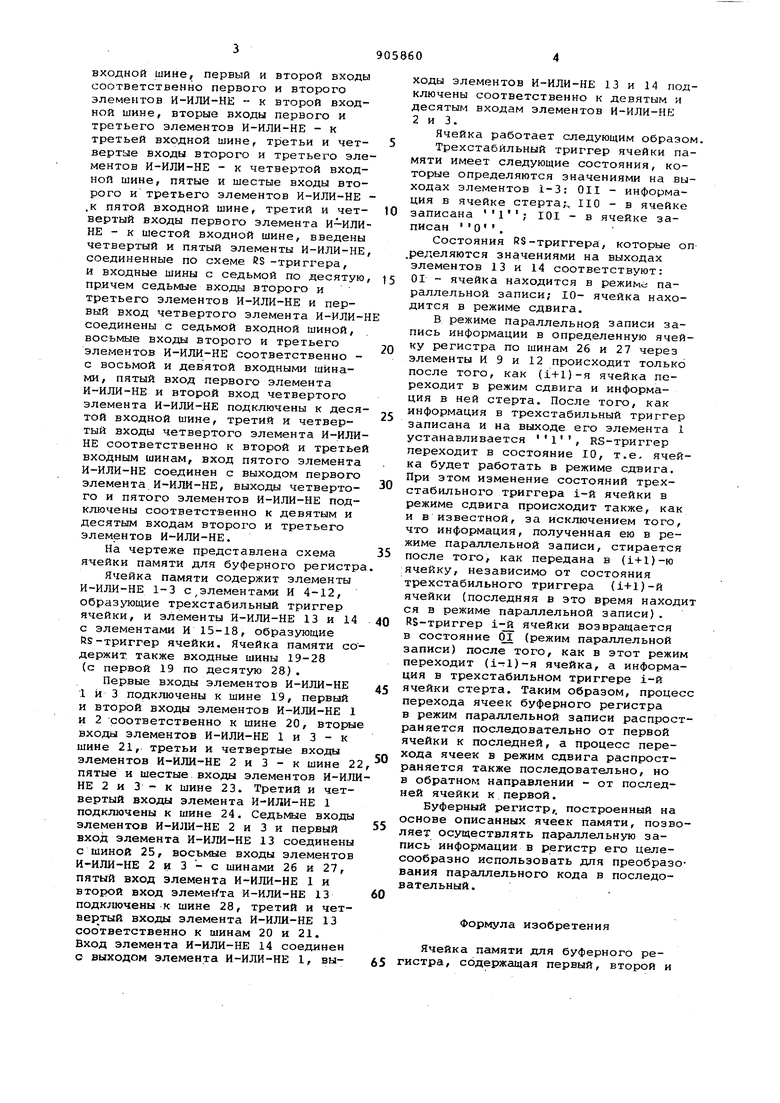

25 регистра, содержащую первый, второй и третий элементы И-ИЛИ-НЕ, соединенные по схеме трехстабильного триггера, входные шины, причем первые входы втоЕЮго и третьего элемен30тов И-И.ГМ-НЕ подключены к первой входной шине, первый и второй входы соответственно первого и второго элементов И-ИЛИ-НЕ к второй входной шине, вторые входы первого и третьего элементов И-ИЛИ-НЕ - к третьей входной шине, третьи и четвертые входы второго и третьего эле ментов И-ИЛИ-НЕ - к четвертой входной шине, пятые и шестые входы второго и третьего элементов И-ИЛИ-НЕ .к пятой входной шине, третий и четвертый входы первого элемента И-ИЛИ НЕ - к шестой входной шине, введены четвертый и пятый элементы И-ИЛИ-НЕ соединенные по схеме CS -триггера, и входные шины с седьмой по десятую причем седьмые входы второго и третьего элементов И-ИЛИ-НЕ и первый вход четвертого элемента И-ИЛИсоединены с седьмой входной шиной, восьмые входы второго и третьего элементов И-ИЛИ-НЕ соответственно с восьмой и девятой входными шинами, пятый вход первого элемента И-ИЛИ-НЕ и второй вход четвертого элемента И-ИЛИ-НЕ подключены к деся той входной шине, третий и четвертый входы четвертого элемента И-ИЛИ НЕ соответственно к второй и третье входным шинам, вход пятого элемента И-ИЛИ-НЕ соединен с выходом первого элемента И-ИЛИ-НЕ, выходы четвертого и пятого элементов И-ИЛИ-НЕ подключены соответственно к девятым и десятым входам второго и третьего элементов И-ИЛИ-НЕ. На чертеже представлена схема ячейки памяти для буферного регистр Ячейка памяти содержит элементы И-ИЛИ-НЕ 1-3 с элементами И 4-12, образующие трехстабильный триггер ячейки, и элементы И-ИЛИ-НЕ 13 и 14 с элементами И 15-18, образующие RS-триггер ячейки. Ячейка памяти со держит, также входные шины 19-28 (с первой 19 по десятую 28). Первые входы элементов И-ИЛИ-НЕ 1 ИЗ подключены к шине 19, первый и второй входы элементов И-ИЛИ-НЕ 1 и 2 соответственно к шине 20, вторы входы элементов И-ИЛИ-НЕ 1 и 3 - к шине 21, третьи и четвертые входы элементов И-ИЛИ-НЕ 2 и 3 - к шине 2 пятые и шестые.входы элементов И-ИЛ НЕ 2 и 3 - к шине 23. Третий и четвертый входы элемента И-ИЛИ-НЕ 1 подключены к шине 24. Седьмые входы элементов И-И;Ш-НЕ 2 и 3 и первый вход элемента И-ИЛИ-НЕ 13 соединены с шиной 25, восьмые входы элементов И-ИЛИ-НЕ 2 и 3 - с шинами 26 и 27, пятый вход элемента И-ИЛИ-НЕ 1 и второй вход элемента И-ИЛИ-НЕ 13 подключены к шине 28, третий и четвер тый входы элемента И-ИЛИ-НЕ 13 соответственно к шинам 20 и 21. Вход элемента И-ИЛИ-НЕ 14 соединен с выходом элемента И-ИЛИ-НЕ 1, выходы элементов И-ИЛИ-НЕ 13 и 14 подключены соответственно к девятым и десятым входам элементов И-ИЛИ-НЕ 2 и 3. Ячейка работает следующим образом. Трехстабильный триггер ячейки памяти имеет следующие состояния, которые определяются значениями на выходах элементов 1-3: ОН - информация в ячейке стерта;,, НО - в ячейке записана Ч; 101 - в ячейке записан О . Состояния RS-триггера, которые оп ределяются значениями на выходах элементов 13 и 14 соответствуют: ОГ - ячейка находится в режиме параллельной записи; 10- ячейка находится в режиме сдвига. В режиме параллельной записи запись информации в определенную ячейку регистра по шинам 26 и 27 через элементы И 9 и 12 происходит только после того, как (1+1)-я ячейка переходит в режим сдвига и информация в ней стерта. После того, как информация в трехстабильный триггер записана и на выходе его элемента 1 устанавливается , RS-триггер переходит в состояние 10, т.е, ячейка будет работать в режиме сдвига. При этом изменение состояний трехстабильного триггера 1-й ячейки в режиме сдвига происходит также, как и в известной, за исключением того, что информация, полученная ею в режиме параллельной записи, стирается после того, как передана в {1+1)-ю ячейку, независимо от состояния трехстабильного триггера (1+1)-й ячейки (последняя в это время находит ся в режиме параллельной записи). RS-триггер 1-й ячейки возвращается в состояние 01 (режим параллельной записи) после того, как в этот режим переходит (i-rl)-я ячейка, а информация в трехстабильном триггере i-й ячейки стерта. Таким образом, процесс перехода ячеек буферного регистра в режим параллельной записи распространяется последовательно от первой ячейки к последней, а процесс перехода ячеек в режим сдвига распространяется также последовательно, но в обратном направлении - от последней ячейки к первой. Буферный регистр,, построенный на основе описанных ячеек памяти, позволяет осуществлять параллельную запись информации в регистр его целесообразно использовать для преобразования параллельного кода в последовательный. Формула изобретения Ячейка памяти для буферного регистра, содержащая первый, второй и

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для буферногоРЕгиСТРА | 1979 |

|

SU799010A2 |

| Ячейка памяти для буферного регистра | 1980 |

|

SU928417A2 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

| Асинхронный регистр сдвига | 1985 |

|

SU1251182A1 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1076951A2 |

| Способ записи - воспроизведения цифровой информации и устройство для его осуществления | 1990 |

|

SU1721630A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Авторы

Даты

1982-02-15—Публикация

1980-04-11—Подача