Устройство огносигся к области вычислительной техники и может &1ть исйользовано в устройствах ввода и вывода инфор мации ЦВМ, в системах программного управления и автоматического регулирования в частиости может бьггь использовано в системах п вичной обработки информации, выводимой из масс-спектрометров, а также при автоматическом управлении магнитным полем масс-спектрометра. Известны устройства для пересчета и возведения в квадрат импульсных сигналов, содержащие л - разрядный счетчик импульсов, 2л- разрядный сумматор, линии задержки и вентили, выполненные на импульсно-потенциальных схемах. Эти устройства обладают низким быстродействием и ограниченными функциональными возможностями. Низкое быстродействие их связано с применением сумматоров, в которых запоминание единиц пере носа между разрядами вьшолняется с АО- мошью линий задержки или на триггерах запоминания переноса. Ограниченность функциональных воэмоЖНостей заключена В отсутствии возможйости реверсиюто наменять значение функции на выходе уст ройства, что особенно важно для сксг&л автоматического управления и регул1фования. Наиболее блишсим техническим реш&нйем к да1шому изобретению является квадратор, сопержшиий основной п -разрядный счетчик, суммяруияцее 2п -разрядное устройство, rt блоков формировав, ния суммы и переноса состоящих, начи-: ная со второго блока, из двух групп элементов И, по три в каждой rpjnme, трех элементов ИЛИ, допоянительного элемента ИЛИ во втором блоке, при этом в каждом 4 -ом, начиная со второго, блока формирования суммы я перен(х;а входы не5)вогс, второго, третьего, четве1 того, пятсго и шестого элементов Исоедннены соответственно с есиничн1ым и нулевым выходами триггера 4 -го разряда Л -разрядного счетчика, вторые вхощл второго, четвертого, третьего н шестого

9лемеятов 1-1 соединейь соответственно с единичным и нулевым выходами триггера О +1 )-го разряда суммирующего 2п-раэрядногр устройства, выходы первого и пятого элементов И связаны с первыми входами соответственно первого и второго элементов ИЛИ, выходы второго ,-третьего, четвертого и шестого элементов И сбедйнёны со входами третьего алё- мента ИЛИ, выход которого связан со счетным входом триггера (i +l)-ro pas ряда суммирующего 2п разрядного устройства, выходь перврго и второго элементов ИЛИ второго блока формирования суммы и переноса соединены с входами дэполнительного элемента ИЛИ, выход первого элемента ИЛИ каждого ( i -l)-ro разряда соединен с вторым входом первого элемента И и с третьими входами четвертого и шестого элементов И каждого Г-го разряда, а выход второго элемента ИЛИ (t -l)-ro разряда соединен с вторым Входом пятого элемента И и с третьими входами второго и третьего элементов И каждого 1 -го разряда.

Однако рассматриваемое устройство ограничено в функциональных возможносгйх, поскольку оно не может реверснвно изменять значение функции на выходе устройства. Наличие такой возможности особенно важно для систем автоматического управления и регулирования.

Целью изобретения является расширение функциональных возможностей за счет реверсйвного изменения значения выходной функции. цель fldcT№aeTCfl feKi, что в квадратор введен блок управления, состоящий из управляющего триггера, шести элементов И, двух элементов; И-НЕ, элемента ИЛИ и элемента задержки, основной ft -разрядный счетчик выполнен реверсив ным, суммирующее 2 ш -разрядное устройство состоит из (п+1)-ра яййого параллельного сумматора со сквозным переносом/ Евыход которого через соединительный элемент ИЛИ подключен к входу реверсивного (п -l)-разрядного счетчика, первые входы первого и вто|)ого элементов К блока управления соедкне)Н11 С $отьетстйённо с входшз1мй шинами сложения 1Г1ы 1Й аний, ferdpbie пдшшючёны к выходам первого и второго элементов И-НЕ блока, входы которых соединены со- отве-гственно с единичными и нулевыми вь1 ходами триггеров разрядов П-разрядного (:гчге зйй:а1 выходы первого и второго элемштов И блока управления св51зани соответственно с единичным и йупеёйм входами

G74O15

управлякмиего триггера и с первым и вторым входами элемента ИЛИ, выход которого соединен с входом элемента задержки блока, единичный выход управлятощего триггера соединен с первыми входами третьего и четвертого элементов И, а нулевой выход - с первыми входами пятого и шестого элементов И блока управления, вторые вхоДы третьего и пятого:

элементов И блока управления связаны с выходом дополнительного элемента ИЛИ блока формирования суммы и переноса второго разряда и с суммирующим входом суммирующего 2п -разрядного устройст.

ва, выходы третьего и пятого элементов И блока управления соединены соответственно с суммирующим и вьтчитающим входами основного П -разрядного счетчика, вторые входы четвертого и шестого элементов И

блока управления связаны с выходом вого элемента ИЛИ блока формирования суммы и переноса п -го разряда, ш тходы шестого и четвертого элементов И блока управления соединены соответственно с;

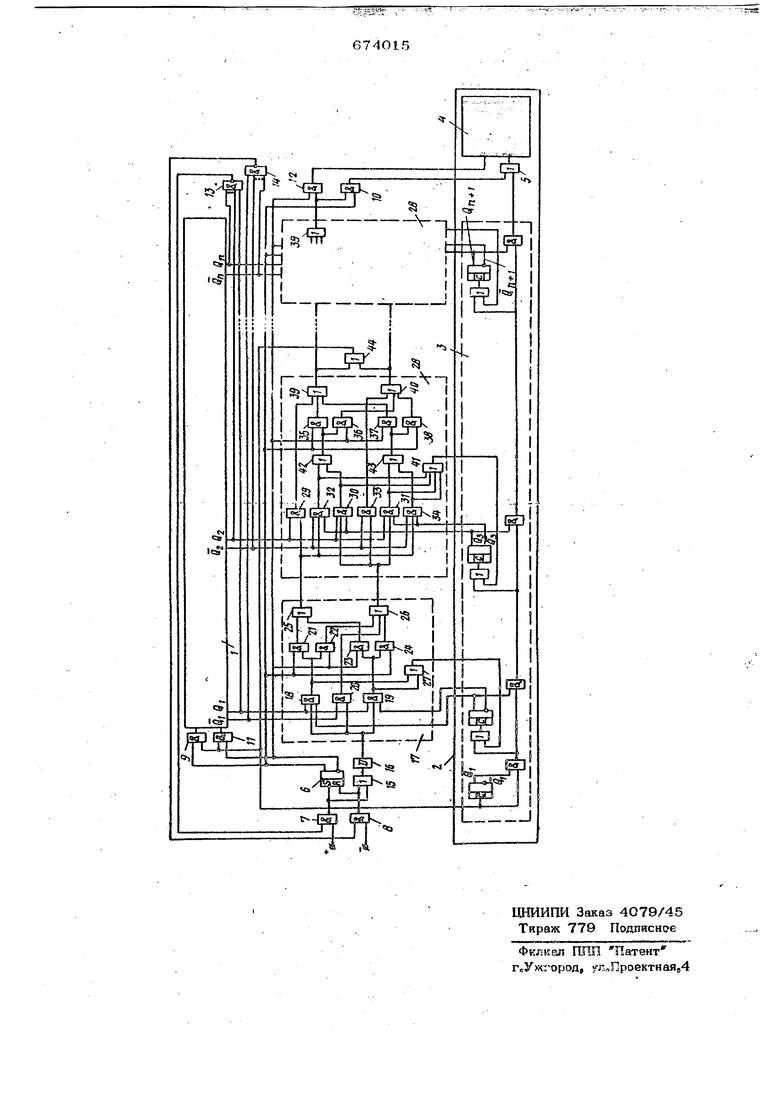

вычитающим и через соединительный эле.мент ИЛИ с суммирующим входами (rt-l)разрядного счетчика суммирующего 2п разрядного устройства, блок формирования и переноса первого разряда выполнен на семи элементах И и трех элемен тах ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с выходом элемента задержки блока управления, вторые входы первого и второго элементов И соединены с .единичным, а третьего элемента И - с нулевым выходами триггера первого разряда основного tl -разрядного счетчика, третьи входы первого и второго элементов И соединены. соответственно с единичным и нулевым выходами триггера второго разряда сум«. мирукяяего 2п -разрядного устройства, выход первого элемента И соединен с первыми входами четвертого и пятого эл©ментов И, выходы которых соединешл с первыми входакга соответственно первого и второго элементов ИЛИ, выход второго элемента И соединен с пери.1ми входами шестого и седьмого элементов И, ЁЙЬТХОДЫ которых связаны со вторыми вхог дамй первого и второго элементов ИЛИ соответстванно, выход третьего элемента И связан с третьим входом второго эле мента ИЛИ, акоды третьего элемента ИЛИ подключены к выходам первого и второго элементов И, а выход «через элемент ИЛИ к счетному взшду триггера второго раэряд® суммирующего 2п -разрядного yciw ройства, вторые входы четвертого, седьмого, пятого и шестого элеменгов И сое пинены соответственно с единичным и ну левым выходам управляющего триггера, каждый блок формирования суммы к пере носа, начиная со второго, содержит седь мой, восьмой, девятый и десятый элемен ты И, четвертый, пятый элементы ИЛИ, причем входы четвертого элемента ИЛИ соединены с выходами второго и че-гаертого эя« 1ентов И, а входы пятого элеме та ИЛИ - с выходами третьего и шестого элементов И, выход четвертого элемен та ИЛИ связан с первыми входами седь мого и восьмого эпементов И, а выход пятого элемента ИЛИ -с первыми входами девятого и десятого элементов И, вто рые входы седьмого, десятого элементов И соединены с единичным, а восьмого, девятого эл ентов И - с нулевым вько дами управляющего триггера, выходы седь мого и девятого элементов И связаны со вторым и третьим входами первого элемента ИЛИ, а шлхрды восьмого « дёсятого эяеме1йтов И - со вторым и третьим входами второго элемента ИЛИ. На чертеже представлена функциональная схема предлегаемого квадратора. Квадратор содержит основной О -разрядный счетчик 1, выполненный реверсивным, суммирукшее 2 п -разрядное уст-f ройство 2, состоящее из (п+1)-разрядного параллельного сумматора 3 со сквоэ ным переносом и реверсивного (п -l)разрядного счетчика 4, соединенных между собой соединительным элементом ИЛИ 5, блок управления, состоящий из управл ющего триггера 6, элв14ентов И 7-12, элементов И-НЕ 13,14, элемента ИЛИ 15 и элемента задержки 16, п блоков формирования суммы и переноса, первый разряд 17 которого состоит из элементов И 18-24, элементов ИЛИ 25-27, и все последукицие. разряды 28 . состоят из елемет тов И 29-38, элементов ИЛИ 39-43, дополнительного элемента ИЛИ 44 во втором разряде. Работа предлагаемого устройства основана на реализации известного алгебраического соотношения 91 (где (а +l) Н - разность между количеством импульсов, поступающихна вход устройства по шинам сяожеиия в вычитания. Согласно реализуемой зависимости каж дый импульс, поступающий по шине еложения (м.читания) на вход реверсивного счетчика 1, прибавляет (вычитает) к ранее записанному в суммирующем устройстве 2 числу предыдущее значение числа в счетчике 1, увеличенное в два раза за счет соедйнейия разрядов 1 и уст ройства 2 со сдвигом вправо на один разряд, после чего импульс поступает на пересчет в П -разрядный счетчик 1 и добавляет единицу в суммирующее 2п -разрядное устройство 2. В исходном Состоянии п-разрядный ;счетчик 1 и суммирующее 2п -разрядное устройство 2 находятся в HyrteBCM положении, при этом с нулевых №1ходов всех триггеров счетчика 1 -подаются положительные потенциалы на все входы логического элемента Й-Н1Е 14 блока управления. На выходе И-НЕ 14 формируется нулевой запрещающий потенциал, поступающий на вход И 8 блока управления. Спеаовательно, при нулевом состоянии реверсивного п -разрйдного счетчика 1 невозможно поступление на вход устройства импульсов, следующих по шине вычитания. Тогда при поступлении импульса по шине сложения он проходит через эл&мент И 7 ( на ее входе присутствует разрешающий положительный потенциал) и поступает далее на единичный установочный вход управляюще1ч триггера 6 и устанавливает его в ешничное состояние, при этом с единичного выхода триггера 6 положительный разреша1рщнй нотеициая поступает на первые входы элементов И :9, 10 блока управления, элёмент в И 21, 24 блока формир жання суммь и перено. са первого разряда элеменгов И 35, 38 блоков остальных разршов, а запрещающий нулевой потенциал поступает Hia nepiвые входы элементов И 11, 12 блока управления, элемёнтоб И 22, 23 блока формирования суммы и переноса нервога разряда, элементов И 36, 37 блоков всех остальных разрядов. С выхода элементов И 7 блока управления импульс поступает также через элемент ИЛИ 15 навх611элШента задержки 16 (величина времени элемента задержки 1б равна времени переброса управляющего триггера 6 из одного состояния в другое). С вькода элемента 16 импульс подступает на входы элементов И 18-20 блока формирования сум.мьг и переноса первого разряда. Поскольку триггер первого разряда счетчика 1 находится в нулевом состоянии, то импульс проходит Через элемент И 20 (на его входе присутх;гвуег разрешающий положительньгй погенциал) и через элемент ИЛИ 26 посгупает на входы элементов И 30, 31 и 33 блока формирования суммы и переноса второго разряда. Поскольку все триггеры и П -разрядного счетчика.1 и суммирующего 2п-разрядного устройства 2 находятся в нулевых состояниях, то во всех разрядах блока формирова тя суммы и переноса импульс проходит через элемент И 33, ИЛИ 4О, не изменяя состояния суммирующего 2п разрядного устройства 2. С выхода элемента ИЛИ 40 блока фор« мирования суммы и переноса второго разряда HMHWbc через дополнительный еле- мент ИЛИ 44 поступает на входы элементов И 9. 11 блока управления н на сум. „ мирующий вход суммирующего 2 - разрядного устройства 2. Так как на входе элемента И 9 блока управления присутствует разрешакшшй по ложитеяьный потенциал, то поступает на суммируюший вход счетчика 1. Этой шераиией добавляется 1 чик 1 и в устройство 2. Поскопьку в исходном состоянии счетчик 1 и устройство 2 находятся в нулевом положении, то в итоге в них записывается число (о... 001), т.е. . При поступлении по шине сложения сяедукндего импульса он проходит через эпементы И 7, ИЛИ 15, элемент задерж, .,„ « «« х°«Ь1 элементов И 18-20 блока формирования суммы и переноса первого разряда. Так как в первом разряде счетчика 1 записывается , а триггер второго разряда устройства 2 находится в нулевом состоянии, то по1южитвпьнь й ра&реша4ощий потенциал присутствует на элементе И 19 блока формирования суммы и переноса первого разряда. Импульс с выхода элемента задержки 16 проходит через элемент И 19 и -через элемент ИЛИ 27 поступает на счетный вход триггера второго разряда суммирукЕцего 21; -разрядного устройства 2, и устанавливает его в ешшичное состояние. Одновременно поступает на входы элементов И 23, 24 бпока формирования суммы и переноса первето разряда и, поскольку на входе эл& мента И 24 присутствует положительный разрешакяций потендаал, поступает через элементы И 24 и ИЛИ 26 на входы элементов И 30, 31 и 33 блока формирования сумкы и переноса второго разряда. Поскольку все тригреры, начиная со второго разряда, счетчика 1, и, начиная с третьего разряда, устройства 2 нахо дятся в нулешзгх состояниях, то импульс во всех разрядах, начиная со второго, бцоков форм1фования суммы и переноса проходит через элементы И 33 и ИЛИ 40, не изменяя состояния триггеров последующих разрядов устройства 2, при этом с Вьгхода элемента ИЛИ 40 второго разряда блока ффмтфования суммы и переноса импульса проходит через дополнительный элемент ИЛИ 44 и поступает на суммирующке входы 1 и устройства 2. В результате в счетчике 1 записывается ., (О....О01О). а в устройстве 2 - число 4 (О. . . О1ОО), т. е. . „ « поступлении на шину сложения , счетчике 1 фиксируется их количество, а в устройстве 2 - импульсов, записанных в счетчике 1. п х-,. избежание сброса в нояь счетчика переполнении на все входы элементов И-НЕ 13 при запошении сче поступают пояожи1 ьньте потен,, . эпе ентаИ НЕ 13 формируется нулевой запрещающий потенциал, который подается на вход элемента И 7 блока управления, препятствуя дальнейшему поступлению импупьсов на вход устройства по щине сложения. При йоступлешщ на вход устройства импульсов по шине вычитания импульс проходит через элемент И 8, поступает тановочный вход триггера 6 и одновременно через элемент ИЛИ 15на вход элемента задержки 16. Триггер 6 устанавливается в нулевое состояние, при этом с единичного выхода триггера 6 нулевой запрещающий потенциал постудает на входы элементов И 9, 10 блока управления,, на входы элементов И 21, 24 блока формирования суммы и переноса., первого) разряда и на входы элементов И 35, 38 блоков формирования суммы и переноса всех остальных . Положительный разрешающий потенциал поступает на входы элементов И 11, 12 блока управления и одновременно на входы элементов И 22, 23 блока формирования суммы и переноса первого разряда и на входы элементов И 36, 37 блоков формирования суммы и переноса всех остальных разрядов. Пусть, например, при поступлении импульса по. шине вычитания 6 счетчике 1 ааписьЬаётся число 2 (О. . . О010), а в устройстве 2 - соответственно квадрат этого числ т.е. 4 (О...0100). Входной импупьс, пройдя через элементы , ИЛИ 15 и элемент задержки 16, поступает на-входы элементов И 18-20 блока формирования суммы и переноса первого разряда. Так как триггер первого разряда счетчика 1 находится в нулевом состоянии, то импульс проходит через элемент И 20(на его входе находится положительный разрешающий потенциал) и через элемент ИЛИ 26 поступает на входы эпементсв И 30, 31 и 33 блока формиро вания суммы и переноса второго разряда Так как триггеры второго разряда счетчика 1 и-третьего разряда устройств ва 2 находятся в единичном состоянии, то импульс проходит через элёмедтьт И 30 (на его входе находится положительный разрешающий потенциал) и через элемент ИЛИ 41 поступает на счетный вход триггера третьего разряда устройства 2 и сбрасывает его в ноль. Одновременно . импульс проходит через элемент ИЛИ 42 и поступает на оды элементов И 35, 36. Поскольку иа входе элемента И 36 присутствует положительный разрешакшшй потенциал, то ямпу71ЬС, пройдя через эл иенты И 36 и ИЛИ 4О, поступает на входы элементов И ЗО, 31 и 33 блока формировесшя суммы в tiep&i носа следукинего разряда. Так как в осталыш1х разрядах счетчика 1 и устройства 2 TpHrreja i находятся в нулевых состояниях, то во всех последукянчх разряяак блоков формирования суьлмьг и неревоса импульр проходит через бпементу И 33 и ИЛИ 40, не изменяя состояния триггеров следуклних разрядов в устройстве 2. Во втором разряде блока формирования суммы и переноса импульс с илхода элемента ИЛИ 40 поступает через, эле мент ИЛИ 44 на суммирующий вход устройства 2 и на вычитающий вход счетчика 1, в результате в счетчике 1 и ycntvройст&э 2 запишется число 1 (О...ОО1) т.е. 1 1. Таким образом можно реверсивно менять значение функции на выходе устройства во всем диапазоне его работы. Использование предлагаемого устройства в схемах ввода и вывода информации ЦВМ, в системах программного управления и автоматического регулирования повышает эффективность их работы. Использование устройства в системах первкчной обработки информации, выводимой из масс спектрометров, и автоматического управления магнитным полем масс-спектрометров автоматизирует работу масс-спектрометров и, следовательно, повышает эффективность их рй5оты. Форм у л а изобретения Ква{фатор, содержаший основной п- разрядный счетчик, суммируюшее 2 и разрядное устройство, п -блоков формирования суммы и переноса, состоящих, начиная со второго блока, их двух групп элементов И, по три в каждой группе, трех элементов ИЛИ, дополнительного элемента ИЛИ во втором блсже, при этом в каждом i -ом, начиная со второго, бло;ке формирования суммы и переноса nejnвые вхощл первого, второго, третьего, четвертого, nsrroro и шестого элементов И соединены соответственно с единичным и нул ешз1м выходами триггера 1-го разряда п - разрядного счётчика, вторые входы второго, четвертого, третьего и шестого элементов И соединены соответственно с единичным и нулевым выходами трнггера{ t-l)-ro разряда суммирующего 2празрядного устройства, выходы первого и пятого элементов И связаны с первыми входами соответственно первого и второго элементов ИЛИ. выходал второго, третьего, четвертого и шестого элементов И соединены с входами третьего элемента ИЛИ, выход которого связан с счеТным входом триггера (i-H)-ro суммиругошего 2п- разрядного устройства, выходы первого и второго 9П 1ентов ИЛИ второго блока фору1Ирования суммы и переноса соединешл с входшли дополнителыюго элемента ИЛИ, выход первого элет-юнта ИЛИ каждого а -l)-rq разряда соединен с вто- рым входом первого элемента И и с третьими входами четвертого и шестого элементов И каждого i -го разряда, а выходвторого элемента ИЛИ (f -i)-ro разряда соединен с вторым входом пятого элемента И и с третьими входами второго и третьего элементов И каждого t-ro разряда, о т л и ч а ю щ и И с я тем, что, с целью расширения функциональных возможностей за счет реверсивного изменения значения выходной функции, в квадратор введен блок управления, состоящий из управляющего триггера, шести элементов И, двух элементов И-НЕ, элемента ИЛИ и элемента задержки, основной О - разрядный счетчик выполнен реверсивным, суммируюшее 2 л -разрядное устройство состоит из (ft +1)-разрядного параллельного сумматора со сквозным переносом, выход которого через соединительный элемент ИЛИ подключен к входу реверсивного (f -1)разрядногб счётчика, перньш входы первого и второго эпвме ггов И блока управпения соединены соогветсгвенно с входными шинами сложения и вь1читания, вторые входы подключены к вьйсодам первого и второго элементов И-1 блока, входы которых соединены соответственно с единичными и нулевыми выходами триггеров разрядов П -разрядного счетчика, выходы первого в вт(фого элементов И блока управпения связаны соответственно с единичным и ну левым входами управляющего триггера и с первым в вторым входами элемента ИЛИ BbiXoa которого соединен с входом элемента задержки блока, единичный выход управляющего триггера соединен с первыми входами третьего и четвертого элементов И, а иулетюй выход - с первыми входами пятого и шестого элемейгов И 6noicia Jraдавления, вторые Входаг третьего и пятого эп€ментоь И блока уггравле ния связаны с выходом дополнитетшного элемента ИЛИ блока форктровайкя суммь и переноса еторого разряда и с суммируюшим ЕКОДОМ суммирукяаего 2п - разрядного устройства, быхрдь третьего и пятогч элементов И блока управпения соединены соответственно с суммирующим.и вычитающим входаме основного о разрядного счетчика, вторые входы четвертого и шестого- алеM tTcm И блока управления связаны с клходом первснО элемента ИДИ бйока фор. мярОЁвния суммь и переноса « -го разрява, выходы шестого я четвертого элементов И блока управления соединены соответственно с вычитаганим и через соеди яительный элемент ИЛИ о суммируюшйм входами, (п -1)- а рядного счетчика суммирующего 2 п -разрядного устройства, блок форалирования суммы и переноса nei iiot4 разряда выполнен на семи элементах И и тр«с элементах ИЛИ, причем первые входы первого, второго и третьего элементов И соединены с выходом элемента задержки блока управления, вторые входы первого и второго элементов И соединены с единичным, а третьего элемента И - с нулевым выходами триггера первого разряда основного И-разрядного счетчиха, третьи входы первого и второ-го элементов И соединены соответственно с единичным и нулевым выходами триг гера второго разряда/суммирующего 2празрядного устройства, выход первого элемента И соединен с первыми входами четвертого и пятого элементов И, выходы которых соединены с первыми вкодами соответстбенно первого и второго элементов ИЛИ, выход второго элемента. И соединен с первыми входами шестого и седьмого элементов И, выходы которых связаны со вторыми входами первого и второго элементов ИЛИ соответственно, выход третьего элемента И связан с третьим входом второго элемента ИЛИ, входы третьего элемента ИЛИ подключены к выходам первого и второго элеме1. тОв И, а выход- Через элемент ИЛИ к счетному юсоду триггера второго разряда суммирующего 2п- разрядного устройств ва, вторые входы четвертого, седьмого, пятого и шестрго элементов И соединень1 соответственно с едн1Шчным и нулевым выходами управлякиаего триггера, каждый блок формирования.суммы и переноса, начиная со второго, содержит седьмой, восьмой, девятый и десятый элементы И, четвертый, пятый элементы ИЛИ, причем входы четвертого элемента ИЛИ сошиненыс выходами второго и четвертого элемента И, а входы пятого элемента ИЛИс выходами третьего и шестЬго элементов И, выход четвертого элемента ИЛИ связанс первьми входами седьмого и восьмого элементов И, а выход пятого элемента ИЛИ - с первыми входами девятого и десятого элементов И, втЬ|%ле входы седьмого, десятого элементов И соединены с единичными, а восьмого, девятого элемен- ОВ И - с нулевым вьосодами упр фляюш&го триггера, выходы седьмого и девятого элем.ентов И связаны со вторым и третьим входами первого элемента ИЛИ, а выходы восьмого и десятого элементов И -со вторым и третьим входами второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Квадратор | 1980 |

|

SU926652A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Цифровой линейный интерполятор | 1989 |

|

SU1693592A1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Цифровой регулятор | 1982 |

|

SU1056130A2 |

| Цифровой регулятор | 1981 |

|

SU974336A1 |

| Устройство для автоматического поиска дефектов в логических блоках | 1982 |

|

SU1108451A1 |

| Арифметическое устройство | 1985 |

|

SU1550510A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Устройство для моделирования дискретного радиоканала | 1983 |

|

SU1103256A2 |

Sv

.J

Авторы

Даты

1979-07-15—Публикация

1977-03-01—Подача