Изобретение относится к области автоматики и вычислительной техники и может быть использовано для автоматизированного контроля работоспособности электронных устройств различного назначения.

Известно устройство для контроля и локализации неисправностей 1, содержащее блок передачи сигналов, переключатель с масштабным усилителем, блок синхронизации и управления, блок информации, счетчик адреса, блок сравнения пределов, первый блок логики, два генератора сигналов, регистр и второй блок логики.

Недостатками этого устройства являются ограниченные функциональные возможности, не позволяющие вести тестовый контроль.

Наиболее близким к данному изобретению по технической сущности является устройство для контроля 2, содержащее блок управления, первый выход которого соединен со входом первого блока памяти и через элемен задержки - с первым входом коммутатора, счетчик, первый выход которого соединен со входом блока индикации,логический блок,программный бло

Недостатком такого устройства является низкое быстродействие.

Целью изобретения является повышение быстродействия.

Это достигается тем, что предлагаемое устройство содержит второй блок памяти, блок формирования адресов, первый и второй регистры, распределитель кодов, компараторы,триг0геры, элементы сравнения, блок опроса регистров, выходы/программного блока через последовательно соединенные второй блок памяти и распределитель кодов соединен с первыми входа5ми первого регистра и первыми входами триггеров, вторые входы которых соединены со вторым выходом блока управления, а выходы - с первыми входами элементов сравнения, вторые входы

0 которых подключены к выходам компараторов, первые входы которых подсоединены к выходам первого блока памяти, а вторые входы - к выходам коммутатора, выходы элементов срав5нения через последовательно соедиг ненные второй регистр, логический блок и счетчик подключены ко входу блока управления, третий выход которого соединен через блок опроса ре0

гистров со вторым входом второго регистра, четвертый выход со вторым входом первого регистра, пятый выход - со вторым входом распредепителя кодов, luecTon выход через блок Формирования адресов со вторым входом второго блока памяти.

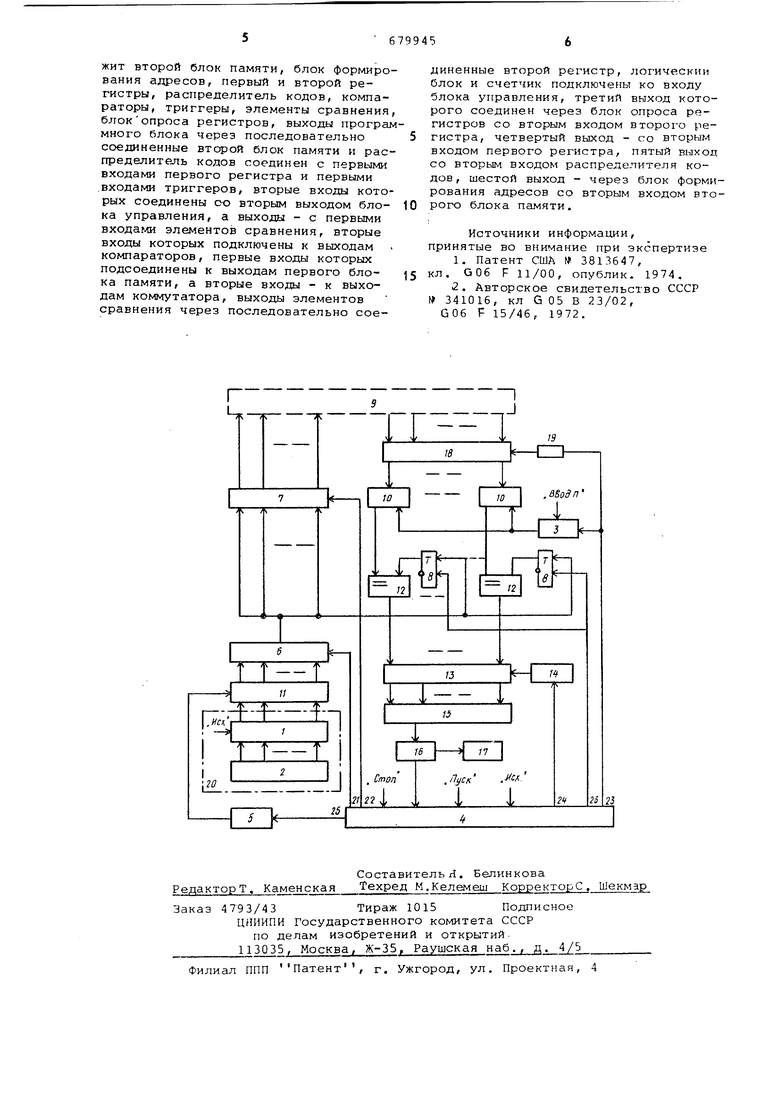

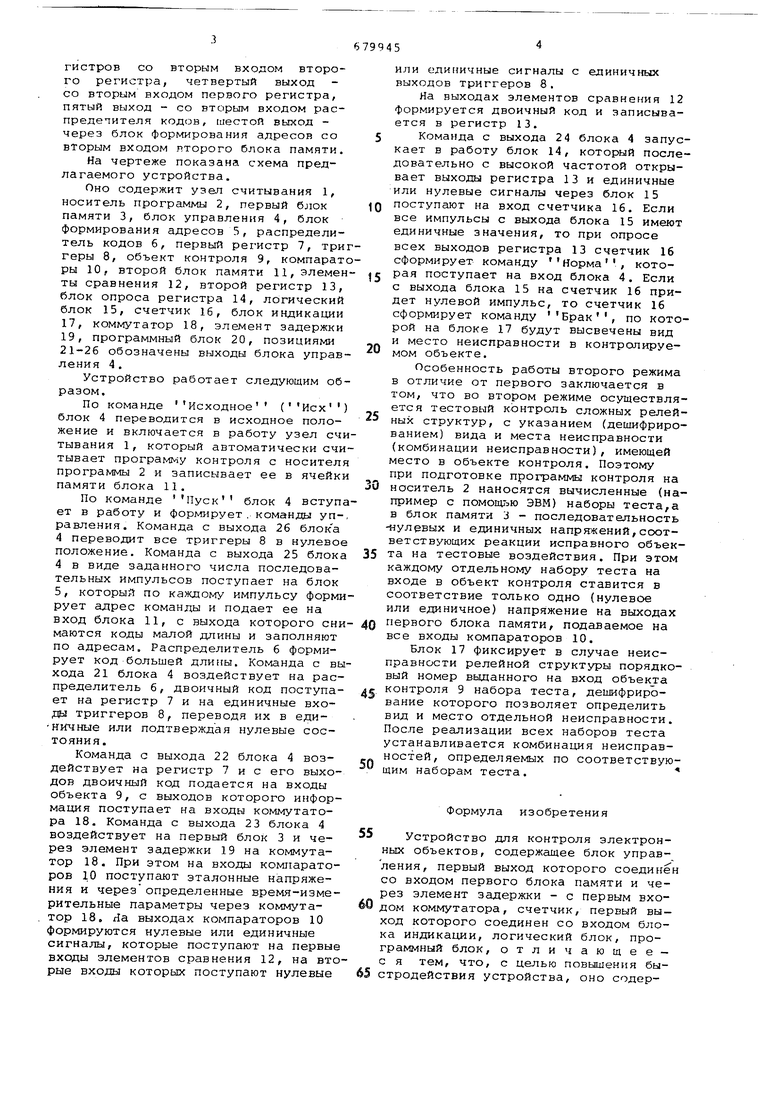

На чертеже показана схема предлагаемого устройства.

Оно содержит узел считывания 1, носитель программы 2, первый блок памяти 3, блок управления 4, блок формирования адресов 5, распределитель кодов б, первый регистр 7, триггеры 8, объект контроля 9, компараторы 10, второй блок памяти 11, элементы сравнения 12, второй регистр 13, блок опроса регистра 14, логический блок 15, счетчик 16, блок индикации 17, коммутатор 18, элемент задержки 19, программный блок 20, позициями 21-26 обозначены выходы блока управления 4 .

Устройство работает следующим образом.

По команде Исходное (Исх) блок 4 переводится в исходное положение и включается в работу узел считывания 1, который автоматически считывает nporpaMNiy контроля с носителя nporpai Mbi 2 и записывает ее в ячейки памяти блока 11.

По команде Пуск блок 4 вступает в работу и формирует. команды уп-, равления. Команда с выхода 26 блока 4 переводит все триггеры 8 в нулевое положение. Команда с выхода 25 блока 4 в виде заданного числа последовательных импульсов поступает на блок 5, который по каждому импульсу формирует адрес команды и подает ее на вход блока 11, с выхода которого снимаются коды малой длины и заполняют по адресам. Распределитель 6 формирует код большей длины. Команда с выхода 21 блока 4 воздействует на распределитель 6, двоичный код поступает на регистр 7 и на единичные входы триггеров 8, переводя их в едиНкчные или подтверждая нулевые состояния.

Команда с выхода 22 блока 4 воздействует на регистр 7 и с его выходов двоичный код подается на входы объекта 9, с выходов которого и 1формация поступает на входы коммутатора 18. Команда с выхода 23 блока 4 воздействует на первый блок 3 и через элемент задержки 19 на коммутатор 18. При этом на входы компараторов 10 поступают эталонные напряжения и черезопределенные время-измерительные параметры через коммутатор 18. Ла выходах компараторов 10 формируются нулевые или единичные сигналы, которые поступают на первые входы элементов сравнения 12, на вторые входы которых поступают нулевые

или единичные сигналы с единичных выходов триггеров 8.

На выходах элементов сравнения 12 формируется двоичный код и записывается в регистр 13.

Команда с выхода 24 блока 4 запускает в работу блок 14, который последовательно с высокой частотой открывает выходы регистра 13 и единичные или нулевые сигналы через блок 15 поступают на вход счетчика 16. Если все импульсы с выхода блока 15 имеют единичные значения, то при опросе всех выходов регистра 13 счетчик 16 сформирует команду Норма, которая поступает на вход блока 4. Если с выхода блока 15 на счетчик 16 придет нулевой импульс, то счетчик 16 сформирует команду Брак, по которой на блоке 17 будут высвечены вид и место неисправности в контролируемом объекте.

Особенность работы второго режима в отличие от первого заключается в том, что во втором режиме осуществляется тестовый контроль сложных релейных структур, с указанием (дешифрированием) вида и места неисправности (комбинации неисправности), имеющей место в объекте контроля. Поэтому при подготовке программы контроля на носитель 2 наносятся вычисленные (например с помощгзю ЭВМ) наборы теста,а в блок памяти 3 - последовательность -нулевых и единичных напряжений, соответствующих реакции исправного объекта на тестовые воздействия. При этом каждому отдельному набору теста на входе в объект контроля ставится в соответствие только одно (нулевое или единичное) напряжение на выходах первого блока памяти, подаваемое на все входы компараторов 10.

Блок 17 фиксирует в случае неисправности релейной структуры порядковый номер выданного на вход объекта контроля 9 набора теста, дешифрирование которого позволяет определить вид и место отдельной неисправности. После реализации всех наборов теста устанавливается комбинация неисправностей, определяемых по соответствующим наборам теста.

Формула изобретения

55 Устройство для контроля электронных объектов, содержащее блок управления, первый выход которого соедине со входом первого блока памяти и через элемент задержки - с первым входом коммутатора, счетчик, первый выход которого соединен со входом блока индикации, логический блок, программный блок, отличающее- с я тем, что, с целью повышения быстродействия устройства, оно содержит второй блок памяти, блок формирования адресов, первый и второй регистры, распределитель кодов, компараторы, триггеры, элементы сравнения, 6jroKопроса регистров, выходы программного блока Через последовательно соединенные второй блок памяти и распределитель кодов соединен с первыми входами первого регистра и первыми .входами триггеров, вторые входы которых соединены ее вторым выходом блока управления, а выходы - с первыми входами элементов сравнения, вторые входы которых подключены к выходам компараторов, первые входы которых подсоединены к выходам первого блока памяти, а вторые входы - к выходам коммутатора, выходы элементов сравнения через последовательно соединенные второй регистр, логическим блок и счетчик подключены ко входу блока управления, третий выход которого соединен через блок опроса регистров со вторым входом второго регистра, четвертый выход - со вторым входом первого регистра, пятый выход со вторым входом распределителя кодов, шестой выход - через блок формирования адресов со вторым входом второго блока памяти.

Источники информации, принятые во внимание при экспертизе

1. Патент США № 3813647, кл. G06 F 11/00, опублик. 1974,

2. Авторское свидетельство СССР № 341016, кл G 05 В 23/02, G06 F 15/46, 1972.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для телеконтроля | 1990 |

|

SU1732366A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1981 |

|

SU1012234A1 |

| Устройство для контроля и диагностики логических блоков | 1984 |

|

SU1295401A1 |

| Устройство для контроля объектов | 1985 |

|

SU1363141A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1383368A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

Авторы

Даты

1979-08-15—Публикация

1978-02-09—Подача