(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ МНОГОКАНАЛЬНЫХ РАВНОДОСТУПНЫХ СИСТЕМ СВЯЗИ

другим входом управляемого делителя частоты и вторым входом блока записи кода, третий вход которого подключен к второму выходу управляемог делителя частоты.

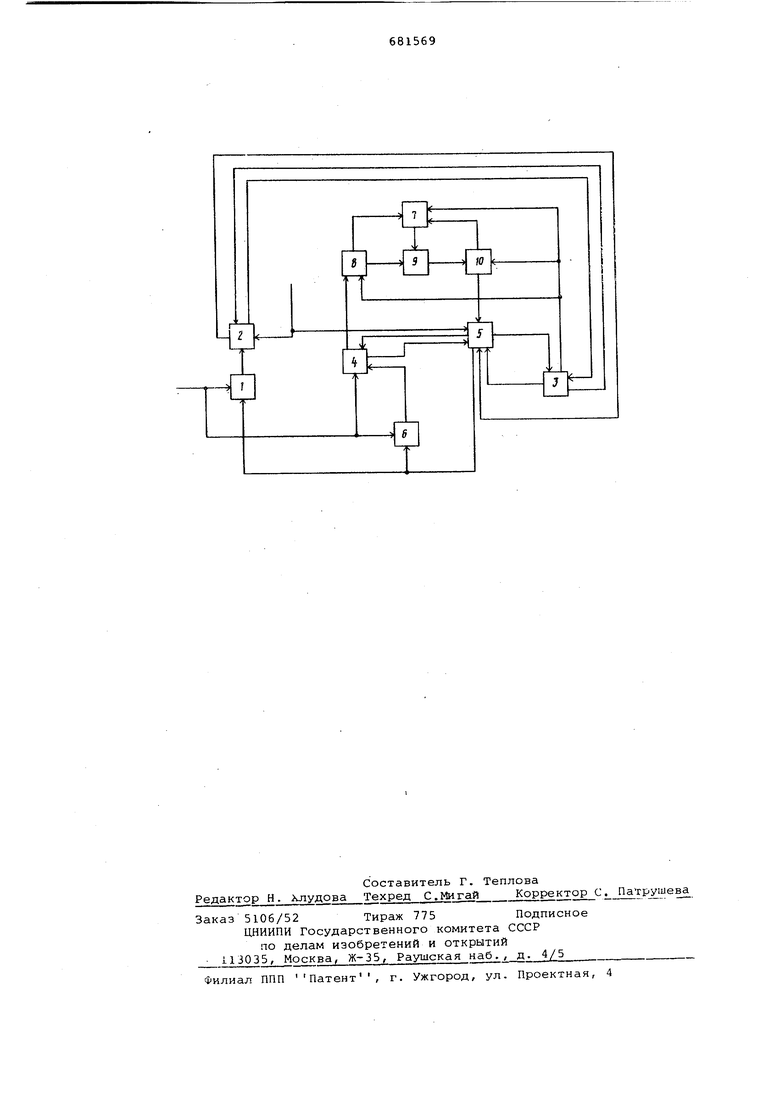

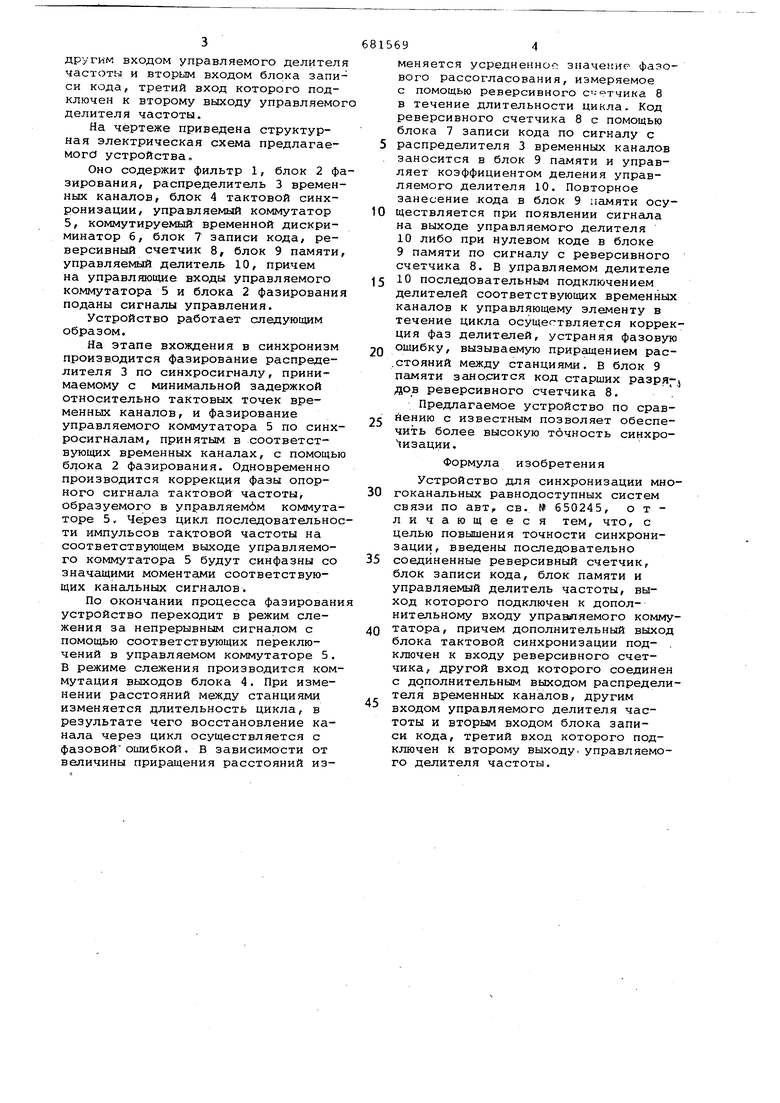

На чертеже приведена структурная электрическая схема предлагаемого устройства.

Оно содержит фильтр 1, блок 2 фазирования, распределитель 3 временных каналов, блок 4 тактовой синхронизации, управляемый коммутатор 5, коммутируемый временной дискриминатор б, блок 7 записи кода, реверсивный счетчик 8, блок 9 памяти, управляемый делитель 10, причем на управляющие входы управляемого коммутатора 5 и блока 2 фазирования поданы сигналы управления.

Устройство работает следующим образом.

На этапе вхождения в синхронизм производится фазирование распределителя 3 по синхросигналу, принимаемому с минимальной задержкой относительно тактовых точек временных каналов, и фазирование управляемого коммутатора 5 по синхросигналам, принятым в соответствующих временных каналах, с помощью блока 2 фазирования. Одновременно производится коррекция фазы опорного сигнала тактовой частоты/ образуемого в управляемом коммутаторе 5, Через цикл последовательности импульсов тактовой частоты на соответствующем выходе управляемого коммутатора 5 будут синфазны со значащими моментами соответствующих канальных сигналов.

По окончании процесса фазировани устройство переходит в режим слежения за непрерывным сигналом с помощью соответствующих переключений в управляемом коммутаторе 5. В режиме слежения производится коммутация выходов блока 4. При изменении расстояний между станциями изменяется длительность цикла, в результате чего восстановление канала через цикл осуществляется с фазовойошибкой, В зависимости от величины приращения расстояний изменяется усредненное:; зв1аче ие фазового рассогласования, измеряемое с помощью реверсивного с-етчика 8 в течение длительности цикла. Код реверсивного счетчика 8 с помощью блока 7 записи кода по сигналу с 5 распределителя 3 временных каналов заносится в блок 9 памяти и управляет коэффициентом деления управляемого делителя 10. Повторное занесение .кода в блок 9 памяти осуществляется при появлении сигнала на выходе управляемого делителя 10 либо при нулевом коде в блоке 9 памяти по сигналу с реверсивного счетчика 8. В управляемом делителе

5 10 последовательным подключением делителей соответствующих временных каналов к управляющему элементу в течение цикла осуществляется коррекция фаз делителей, устраняя фазовую

Q ошибку, вызываемую приращением рас.стояний между станциями. В блок 9 памяти зано.сится код старших разряд.) дов реверсивного счетчика 8.

Предлагаемое устройство по сравйению с известным позволяет обеспечить более высокую точность синхро изации.

Формула изобретения

Устройство для синхронизации многоканальных равнодоступных систем связи по авт, св. № 650245, отличающееся тем, что, с целью повышения точности синхронизации, введены последовательно 5 соединенные реверсивный счетчик, блок записи кода, блок памяти и управляемый делитель частоты, выход которого подключен к дополнительному входу управляемого коммутатора, причем дополнительный выход блока тактовой синхронизации под- . ключен к входу реверсивного счетчика, другой вход которого соединен с дополнительным выходом распределителя временных каналов, другим входом управляемого делителя частоты и вторым входом блока записи кода, третий вход которого подключен к второму выходу.управляемого делителя частоты.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU758550A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1469562A1 |

| Устройство синхронизации многоканальных равнодоступных систем связи | 1978 |

|

SU745012A1 |

| Устройство для синхронизации равнодоступных многоканальных систем связи | 1975 |

|

SU563736A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1987 |

|

SU1478363A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1976 |

|

SU650245A1 |

| Устройство синхронизации многоканальной системы радиосвязи | 1990 |

|

SU1739502A1 |

| Устройство синхронизации равнодоступной многоадресной системы радиосвязи | 1982 |

|

SU1030986A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

Авторы

Даты

1979-08-25—Публикация

1978-03-16—Подача