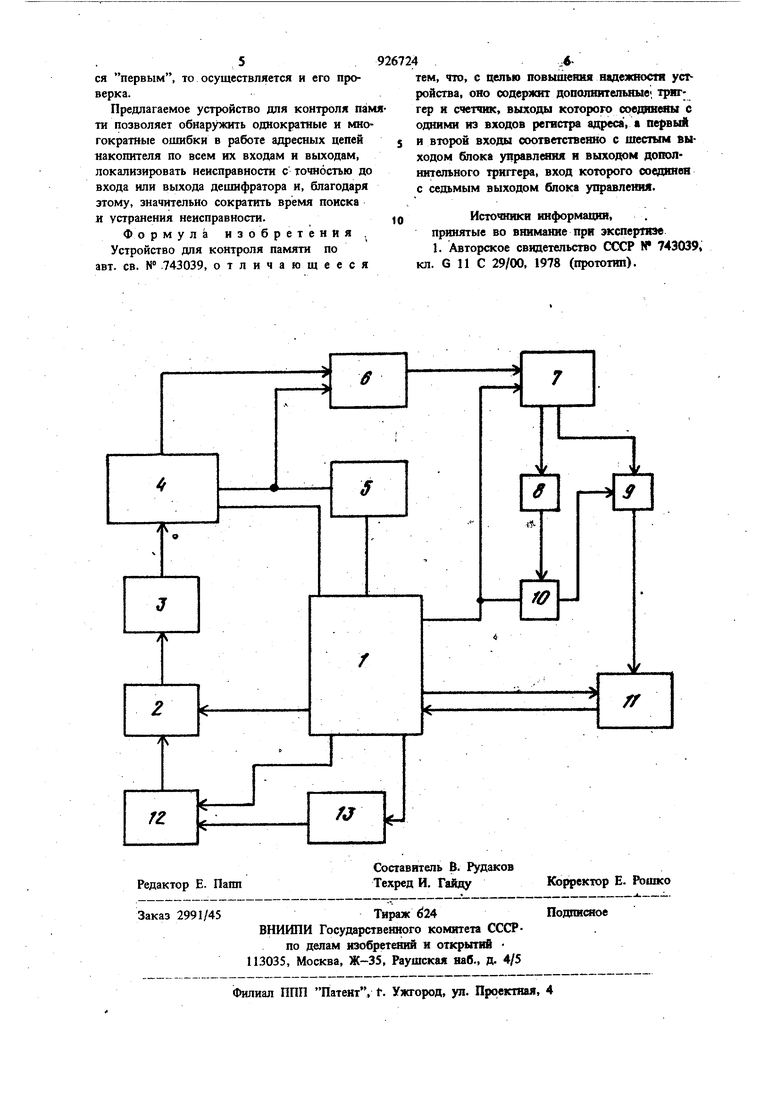

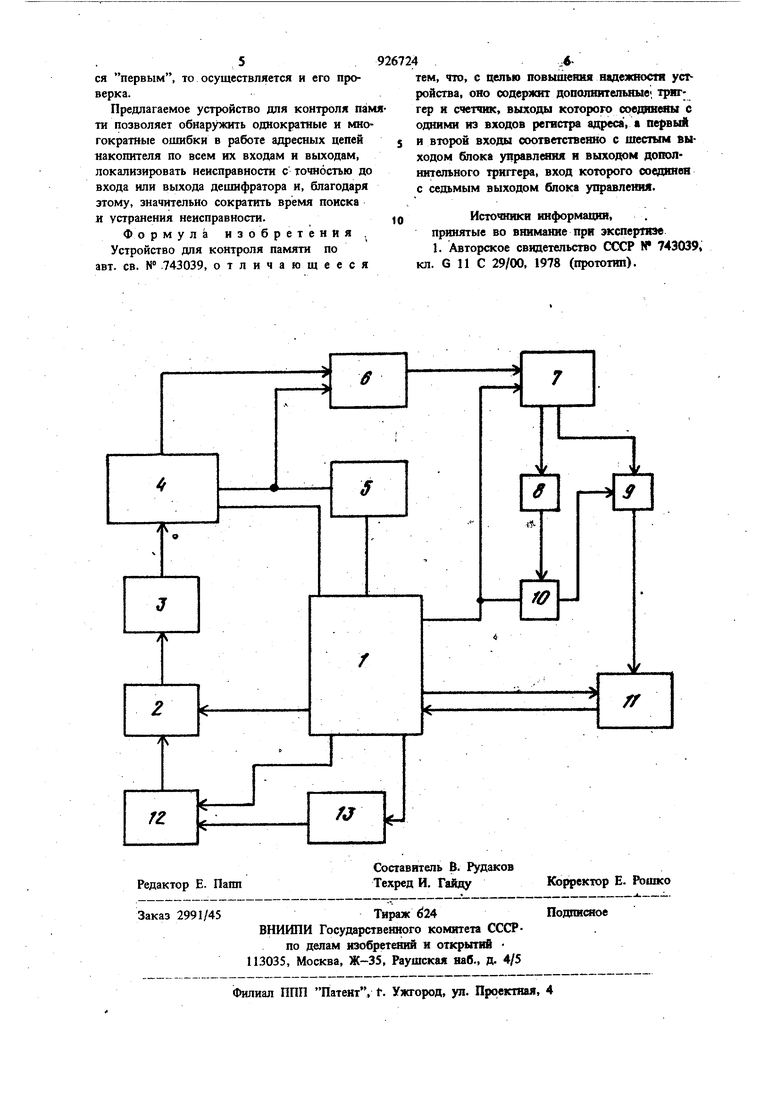

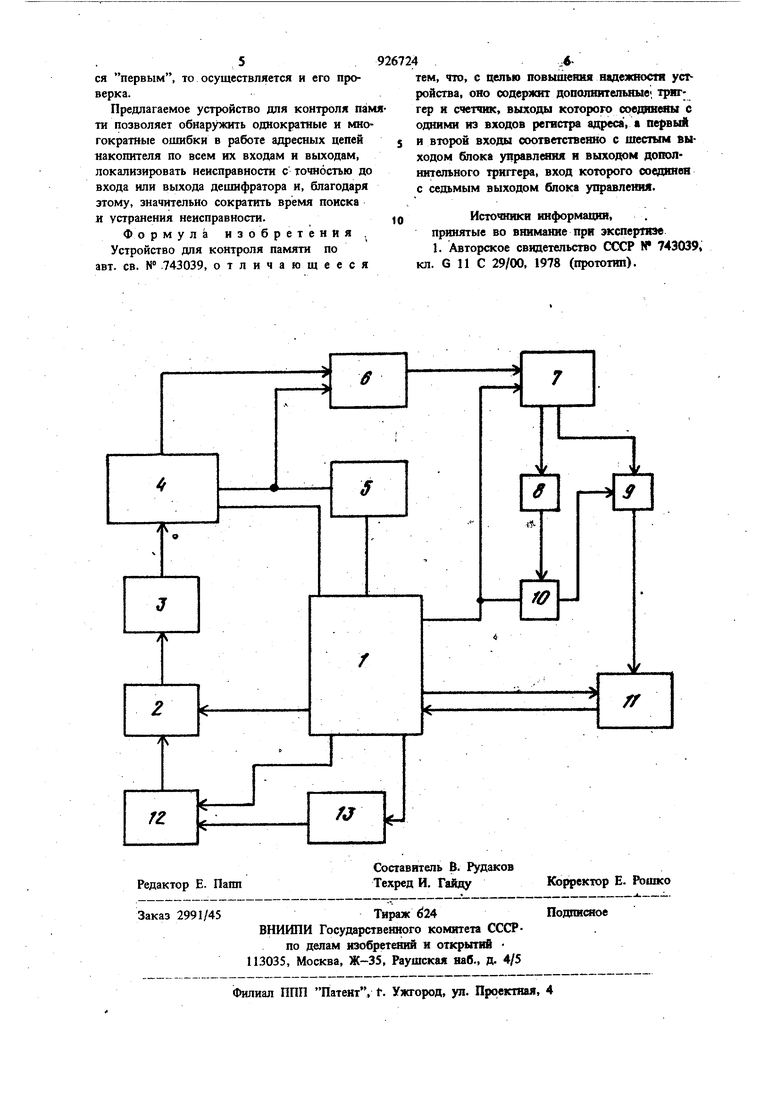

(54) УСТГОЙСТВО ДЛЯ КОНТЮЛЯ ПАМЯТИ Изобретение относится к запоминающим устройствам. По основному авт. св. № 743039 известно устройство для контроля памяти, содержащее последовательно соединенные регистр адреса и дешифратор адреса, выход которого подклю чен к одному из входов накопителя, другие входы которого подключены к выходу регист ра числа и первому выходу блока управления,, второй и третий выходы которого соединены со входами регистра адреса и регистра числа, блок сравнения, входы которого подкл чены к выходам накопителя и регистра числа, счетчик, элементы И, триггер и регистр ошибок, выход и первый вход которого подключены соответственно ко входу и четвертому выходу блока управления, второй вход соединен с выходом oднqгo из элементов И, вхо ды которого подключены к одним из выходов счетчика и выходу триггера, первый вход которого соединен с пятым выходом блока управления и одним из входов счетчика, други вход и выход счетчика подключены соответственно к выходу блока сравнения и входам другого элемента И, выход которого подключен ко второму входу триггера 1. Недостатком этого устройства является то, что оно не позволяет выявить все ощибки выходных цепей адресного тракта, в частности не выявляются ошибки в работе последнего по номеру выхода дешифратора, что приводит к увеличению времени восстановления устройства и снижает надёжносп устройства. Цель изобретения - повьштение надежности устройства. Поставленная цель достигается тем, что В устройство для контроля памяти введены дополнительные триггер и счетчик, выходы которого соединены с одними из входов регистра адреса, а первый и второй входы соответственно с шестым выходом блока управления и выходом дополнительного тритгера, вход которого соединен с седьмым выходом блока управления. На чертеже представлена структурная схема устройства для контроля памяти. Устройство содержит блок 1 управления, ре-, гистр 2 адреса, дешифратор 3 адреса, накопи392тель 4, регистр 5 числа, блок 6 сравнения, счетчик 7, элементы И 8 и 9, триггер 10, регистр 11 ошибок, дополнительный счетчик 12, дополнительный триггер 13. Выходы блока 1 управления с первого по пятый соединены соответственно с входами накопителя 4, регистра 2 адреса, регистра 5 числа, регистра II ошибок и триггера 10. Выходы счетчика 12 соединены с одними из входов регистра 2 адреса, а первый и второй входы соответственно с шестымвыходом блока 1 управления и выходом триггера 13, вход которого соединен с седьмым выходом блока 1 управления. Устройство работает в двух режимах. Проверка входных адресных цепей (первый режим). Работа устройства начинается с установки в нулевое состояние регистров 2 и 5, счетчиков 7 и 12 и триггеров 10 и 13 (цепи установки в нуль условно не показаны). Затем блок 1 управления формирует режим запи си информации в накопитель 4 и разрешает формировани|г кодов адреса и числа. Код адреса формируется счетчиком 12 и передается в регистр 2 адреса. Первоначальйо пересчет адресов организуется только в первой половине регистра адреса, в другую половину записываются нули. Блок 1 управления формирует число, необходимое для проверки определен ного входа дешифратора 3, и регистр 5 числа записывает его в накопитель 4: при проверке i-ro входа дешифратора по каждому выбираемому адресу в накопитель записывается число, соответствующее состоянию i-ro разряда регистра адреса. Через 2 циклов за писи (п - количество разрядов в регистре адреса) блок 1 управления формирует сигнал считьюания. Считанная из накопителя 4 инфорт мация блоком 6 сравнения сравнивается с ранее записанной и цри их несовпадении форми- рует сигнал ошибки, подаваемый на вход счет чика 7. Неисправность i-ro входа дешифратора 3 адреса приводит к тому, что к половине запоминающих элементов накопителя 4 обраще ние происходит дважды: сначала в них записы вается нуль, а затем (по тому же адресу) единица. При сравнении считанной и записанной информации получается 2/2 ошибок, записанных в счетчике 7. Элемент И 9 фиксирует это состояние счетчика 7 и при наличии разрешающего сигнала с триггера 10 вьфабатьшает сигнал подаваемый на информационный вход регистра 11. Триггер 10 дает разрешающий сигнал на вход элемента И 9 при условии, что не срабатьшает элемент И 8, фиксирующий состояние счетчика 7, равное . Такое состояние счетчика 7 может быть в том случае, если ошибки вь1званы не (или не только) неисравностью i-ro входа дешифратора, а неисравностью накопителя 4. Таким образом, при количестве ошибок, большем или меньшем 2 /2, сигнал на информационный вход регистра И ошибок не поступает, т.е. при этом i-ый вход дешифратора не считается неисправным. После окончания процесса считывания при проверке 1-го входа дешифратора 3 блок 1 управления вырабатывает управляющий сигнал по которому происходит запись в регистр 11 ошибок и установка в нуль счетчика 7 и триггера 10. Затем блок 1 управленияформирует число, необходимое для проверки (i + 1)-го входа дешифратора 3, и процесс проверки продолжается аналогично описанному до последнего входа. Затем блок 1 управления формирует сигнал считывания информации из регистра 11 ошибок, если ошибки имеют место, то блок 1 управления формирует сигнал останова; если оишбки отсутствуют, то проверка продолжается. При этом код адреса со счетчика 12 переписывается уже в старшие разряды регистра 2 адреса, а младшие заполняются нулями. В остальном работа устройства протекает аналогично описанному выше. Проверка выходных адресных целей (второй режим). Работа устройства во. втором режиме (проверка правильности работы выходов дешифратора) в принципе аналогична работе в первом режиме, но имеет три особенности. Первая особенность состоит в том, что на регистр 2 адреса подается не п/2-разрядный, а (п-1)разрядный код, а в п-ый разрАд регистра 2 адреса записывается нуль. Вторая особенность заключается в том, что для проверки правильности работы j-ro выхода дешифратора 3 блок 1 управления формирует число для записи в накопитель таким образом, что нуль записывается по адресам с номерами j + (m-l)2 . (,22 72), по остальным номерам за1шсьшаются единицы. Обнаружение неисправности выходных цепей дешифратора 3 происходит аналогично обнаружению неисправности входных цепей. Это относится ко всем выходам, кроме последнего, так как при просчете счетчика 12 в йрямом направлении последний выход дешифратора 3 не проверяется. Поэтому после окончания прямого просчета блок 1 )Т1равления вырабатывает сигнал реверса, устанавливающий триггер 13 в состояние единицы (это третья особенность работы устройства в режиме проверки выходных адресных цепей). Сигнал с триггера 13 переводит счетчик 12 в режим реверса, и начинает ся обратный просче адресов. Так как при этом последний выход дешифратора становится первым , то осуществляется и его проверка.

Предлагаемое устройство для контроля памти позволяет обнаружить однократные и многократные ошибки в работе адресных цепей накопителя по всем нх входам и выходам, локализировать неисправности с точностью до входа или выхода деигафратора и, благодаря этому, значительно сократить время поиска к устранения неисправности.

Формуле изобретения ,

Устройство для контроля памяти по авт. св. № .743039, отличающееся

тем, по, с целью повышения надежяостя уст ройства, оно содержит дополнительные- триггер и счетчик, выходы которого соедиямы с одними иэ входов регистра адреса, первый и второй входы соответственно с шестым выходом блока управл шя и выходом дополнительного триггера, вход которого соеднноя с седьмым выходом блока управлеюм.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N 743039, кл. G И С 29/00, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1978 |

|

SU743039A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU980166A1 |

| Устройство для контроля памяти | 1982 |

|

SU1020865A1 |

| Оперативное запоминающее устройство с самоконтролем | 1977 |

|

SU708423A1 |

| Устройство для контроля памяти | 1979 |

|

SU769642A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037350A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| Устройство для контроля накопителей | 1982 |

|

SU1048521A1 |

Авторы

Даты

1982-05-07—Публикация

1980-01-24—Подача