(54) ЗАПОМИНАЮЩИЙ ЭЛЕМЕНТ

жет служить инжектором, поэюлг/ заюмйнаюццш элелдант невозможно выполнить на одном кристалле с использовшаюм подложки в качестве рз.

Цель изобретешш состоит в повышеш1й быстродействия запоминающего элемента и степени интеграции.

Поставленная цель достигается тем, что запоми н1Ш|дай элемент дополнительно содержит третш, .чет1Йртьш и пятый управляющие п-р-п транзисторы и допоташтельньш источник тока, причем базы третьего, четвертого и пятого управляюц;5нх п-р-п транзисторов «одьслючены к 1шформшдаонной ишие н положительному полюсу.дополнительного источника тока, отрицательньш полюс которого подключен к имие Питаний, коллекторы третьего и четвертого управляющих я-р-п транзисторов подключены соответственно к коллекторам первого и второго п-р-н транзисторов запиш. коллектор пятого управляющего п-р-п транзистора подключен к базе п-р-п транзистора считывания, а змит1-еры третьего, четвертого и пятого управляющих п-р-п тршгаисторов подключены к шине нулевого потентдаала.

Такое исполнение запомгнающего элемента позволяет использовать обцдай инжектор, например подложку, т.е. изготовлять интегральную схему ЗЭ только на вертикальньзх транзисторах как п-р-п, так и р-п-р и за счет этого повысить быстродействие и степень ннтеграцни запо в-пшгонюго элемзигд и снизить потребяяелзую монщость,

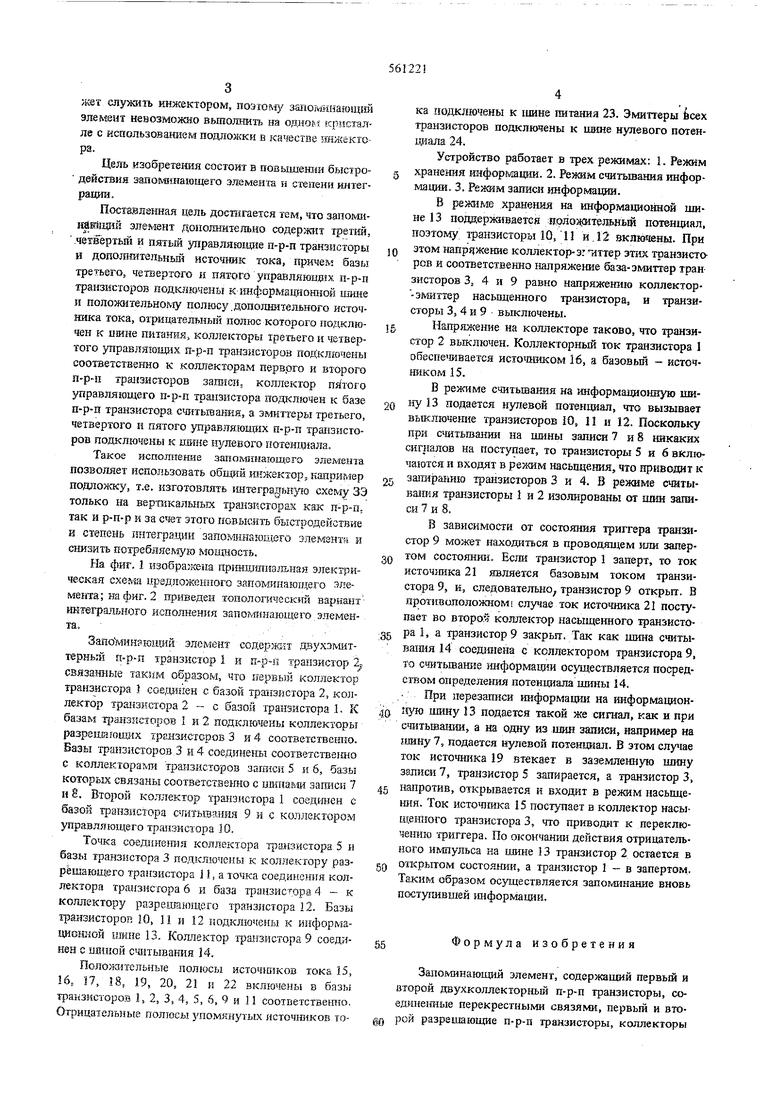

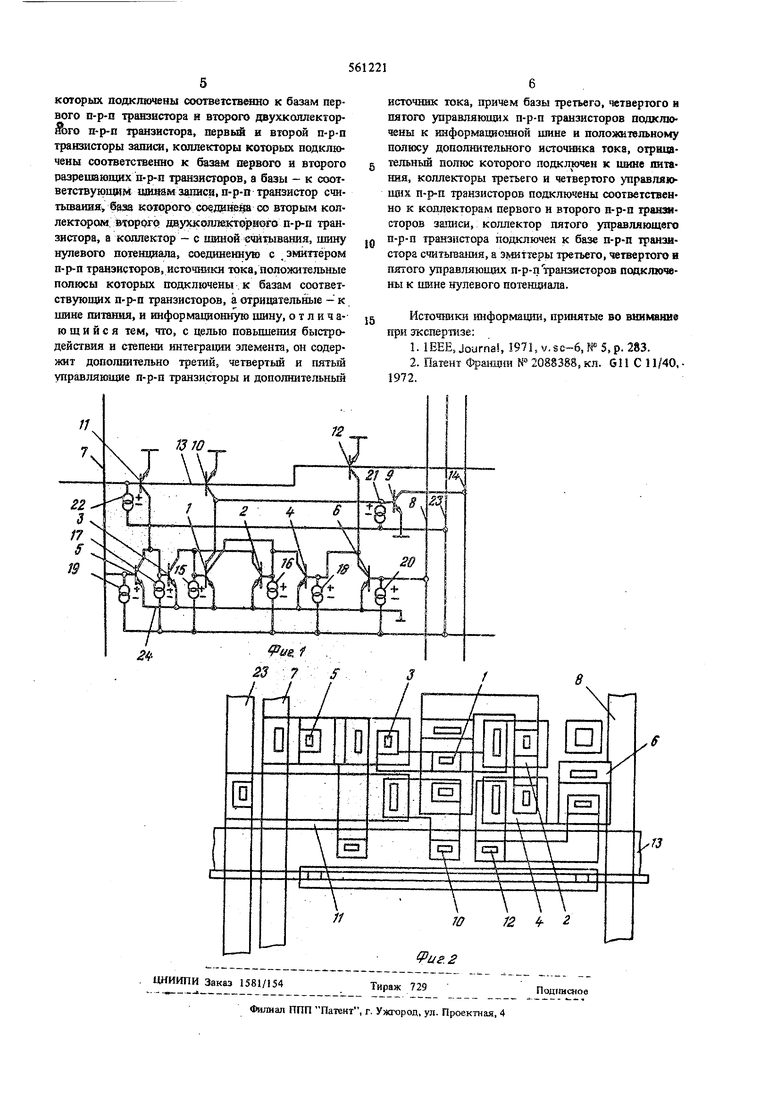

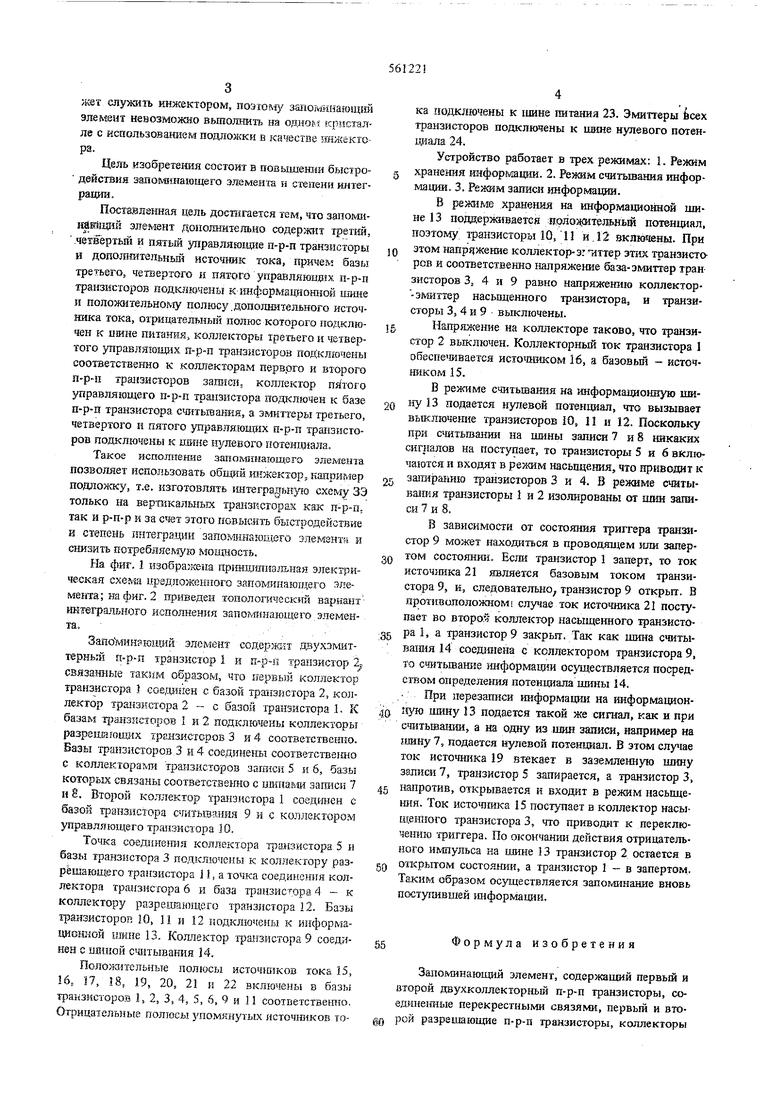

На фнг, 1 изобра;кепа пркнцигп13.чьная элекгрическая схема предложенного запс шнающб.го элемента; на фиг. 2 приведен топологаческте вариант нк1гегралл ного исполнения запоминающего элемента..

Заиомин 1ощяй элемент содержит двухэмиттерньш п-р-п транзистор 1 и п-р-й тршгаистор 2, связадагые тактам образом, что первый коллектор транзистора I соединен с базой транзистора 2, коллектор транзистора 2-е базой транзистора 1. К базам т1 а11зис1Р{зов I и 2 подключены коллекторы разреиигоицк транзясторов 3 и 4 соответственно. Базы транзисторов 3 н4 соедине Ш соответствекшо с коллекторами транзисторов загажи 5 и 6, базы которых связаны соответственно с ишнал-ш записи 7 н 8. Второй коллектор транзистора 1 соедшген с базон транзистора считывания 9 и с коллектором управляюндего трг1нзистора 10.

Точка саеднрге}шя коллектора транзистора 5 и базы транзистора 3 подключены к коллектору разрешающего транзистора 11, а точка соединення коллектора транзистора 6 и база транзистора 4 - к коллектору разрешаинцаго транз1гстора 12. Базы гранзистороп Ш, И и 12 подключены к информациогшой шине 13. Коллектор i-ранзистора 9 соединен с ц. сштывашш 14.

Полойштельные полюсы источш1ков тока 15, б, 17, 1В, 19, 20, 21 и 22 включены в базы транзисторов 1, 2, 3, 4, 5, 6, 9 и 11 соответственно. Отрндательньш полюсы зпомкнутых источников тока подключены к шине питания 23. Эмиттеры Ьсех транзисторов подключены к имне нулевого потенидала 24.

Устройство работает в трех режимах: 1. Режим

хранения информации. 2. Режим считьшания информации. 3. Режим записи информации.

В режиме хранения на информационной шине 13 поддериагвается :надояштельный потенциал, поэтому транзисторы iО,11 и, 12 зключены. При

этом напряжение коллектор- з: лттер этих транзисторов и соответственно напряжение база-эмиттер транзисторов 3. 4 и 9 равно напряжеш1ю коллектор-зьшттер насьпденного транзистора, и транзисторы 3, 4 и 9 вьпслючены.

Напряжение на коллекторе таково, что транзистор 2 выключен. Коллекторный ток транзистора 1 обеспечивается истойносом 16, а базовьш - источником 15.

В режиме считьшания на информационную шину 13 подается нулевой потенциал, что вызывает выключе ше транзисторов 10, 1 и 12. Поскольку при сштьюании на шины записи 7 и 8 никаких сигналов на поступает, то транзисторы S и 6 включаются и входят в режим насыщения, что приводит к

зшгарашпо транзисторов 3 и 4. В режиме счнтывагшя транзисторы 1 и 2 изолированы от Ш1Ш записи 7 и 8.

В зависимости от состояния триггера транзистор 9 может находиться в проводящем или запертом состоянгш. Ecjra транзистор 1 заперт, то ток источшша 21 является базовым током транзистора 9, и, следовательно, транзистор 9 открыт. В противоположном случае ток источника 21 поступает во второй- коллектор насыщенного транзистоpa 1, а транзистор 9 закрья. Так как шина считыБшшя 14 соединена с коллектором транзистора 9, то считьшашге информащш ос ществляется посредетвом определения потенциала шины 14. - При перезаписи информации на информацион1 ую шину 13 подается такой же сигаал, как и при считьшаики, а на одну из шин записи, например на ЛЕШну 7, подается нулевой потенциал. В зтом случае ток источш{ка 19 втекает в заземлеш1ую зэлиси 7, тралзистор 5 запирается, а транзистор 3,

напротив, открывается н входит в режим иасьпцения. Ток истошшка 15 поступает в коллектор насыщенного транзистора 3, что приводит к переключению триггера. По о сончании действия отрицательного импульса на шине 13 транзистор 2. остается в

открытом состоянии, а транзистор 1 - в запертом. Таким образом осуществляется запоглгаание вновь постутшвшей Ш1формаш1И.

Формула изобретения

Запоминающий элемент, содержащий первый и второй двухколлекторный п-р-п транзисторы, соед,иненные перекрестными связями, первый и второй разрешающие п-р-п транзисторы, коллекторы

которых подключены соответственно к базам первого п-р-о транзистора н второго двухколлекторшго п-р-п транзистора, первый в второй п-р-п транзисторы записи, коллекторы которых подключены соответстаенно к базам оервого и второго разрешающих п-р-п транзисторов, а базы - к соответствую1одм вдшам записи, п-р-п транзистор свдтьшания база которого соедане|в со вторым коплектсфом второго даузсколлекториого п-р-п транзистора, а коллектор - с шиной ечйщвания, шину нулевого потешрала, соединенную с эмиттером п-р-п транзисторов, источники тока, положительные полюсы которых подключены к базам соответствующих п-р-п транзисторов, а отрицательные - к шине питания, и информационную шину, отличающийся тем, что, с целью повьпиения быстродействия н степени интеграции элемента, он содержит дополнительно третий, четвертый и пятый управляющие п-р-п транзисторы и дополнительньп1

//

. ne. 1 . 23 7 У

источник тока, причем базы третьего, четвертого и пятого управляющих п-р-п транзисторов подключены к информационной шине и положительному полюсу дополнительного источника тока, отрицательный полюс которого подключен к шине питания, коллекторы третьего и четвертого правляющ х П-р-п транзисторов подключены соответственно к коллекторам первого и второго п-р-п транзисторов записи,: коллектор пятого управляющего п-р-п транзистора подключен к базе п-р-п транзистора считьгеа шя, а элшттерь: третьего, четвертого и пятого управляющих п-р-п TpaHsicropoB подключены к шине нулевого потенциала.

Источршки 1шформации, принятые во внимание

при зкспершзе:

1.IEEE, JournaS, 971, v.sc-6, N 5,p. 283.

2.Патент OpaiGSjra N 2088388, кл. 611 С 11/40, 1972.

8

| название | год | авторы | номер документа |

|---|---|---|---|

| Коммутатор | 1977 |

|

SU684742A1 |

| Оперативное запоминающее устройство | 1982 |

|

SU1111204A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Усилитель записи и считывания для запоминающего устройства с произвольной выборкой | 1983 |

|

SU1091223A1 |

| Универсальный Д(Т)-триггер | 1988 |

|

SU1561200A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU693434A1 |

| Матричное запоминающее устройство | 1977 |

|

SU744724A1 |

| Дешифратор | 1975 |

|

SU610298A1 |

| Формирователь сигналов записи и считывания | 1983 |

|

SU1113852A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

Авторы

Даты

1977-06-05—Публикация

1975-01-04—Подача