1

Изобретение относится к области вычислительной техники и может быть использовано для выполнения арифметических и логических операций в арифметических устройствах ЭВМ.

Известно матричное устройство для умножения, осуществляющее только операцию умножения, содержащее п групп по числу разрядов множителя, каждая группа содержит дешифраторы, п одноразрядных сумматоров и логические элементы 1).

Недостатками такого устройства является малое быстродействие выпсшнения операции умножения из-за необходимости форидарования каждого частичного произведения и невозможн.ость выполнения других арифметических и логических операций.

Наиболее близким по технической сущности к данному изобретению является устройство 2, содержащее регистр множителя, п/2 элементов И, п/2 дешифраторов, К групп п/2 арифметико-логических блоков, в каждой группе с разрядностью {п + (2 )

t 1,..,п), причем

(где К - од.

первый вход 1-го элемента И соединен с (21-1 )-ым выходом регистра

множителя (i 1,4,...,п), входы п/2 дешифраторов соединены с выходами регистра мнсяснтеля.

Недостатком этого устройства являются ограниченные функциональные возможности.

Целью изобретения является расширение функциональных возможностей устройства за счет выполнения опера0ций: сложение, вычитание, сдвиг вправо, сдвиг влево.

Для этого в предлагаемое устройство введены (п/2 + 1)-ый элемент И, коммутатор, пржчем первый разряд

5 первой информационной шины устройства разрядностью п соединен со вторыли входами п/2 элементов И, выходы которых соединены со входами младших разрядов первых групп вхо0дов каждого арифметико-логического блока в каждой группе устройства, начиная со второй, выход j -то дешифратора соединен ( 1,...,п/2) с управляющим входом ). -го арифметико5логического блока первой группы, входы со второго по п-й первой группы входов которого соединены с соответствующими разрядами второй информационной шины разрядностью п уст0ройства, первая информационная шина

разрядностью n которого соединена с первым,.../ п-м входами I -го арифметико-логического блока первой группы, п-ый разряд второй информационной 11ШНЫ разрядностью n устройства соединен с первым входом (п/2+ + 1)-го элемента И, первая управляющая шина устройства соединена с управляющими входами п/2-го дешифратора, коммутатора и вторым входом (п/2 + 1)-го элемента И, первый и второй входы коммутатора соответственно соединены с п-ым и (п-1)-ым разрядами первой информационной шины разрядностью n устройства, а выход - с (п + 1)-ым входом первой группы входов п/2 арифметико-логического блока первой группы, (п + 1)-ый вход второй группы входов которого соединен с выходом (п/2+1)-го элемента И, выходы (2т - 1) арифметико-логических блоков -ой группы устройства (т 1,,..,п/2) соединены с первой группой (i + 1) входов со сдвигом вправо на 2 разрядов каждого арифметико-логического блока (Е + 1)-ой группы устройства, выходы 2т арифметико-логических блоков Е -ой группы устройства соединены со второй группой i-входов со сдвигом на 2 разрядов влево каждого арифметикологического блока (t + 1)-ой группы устройства, выход младшего разряда (2т - 1)-го арифметико-логического блока первой группы устройства подключен к первому входу соответствующего разряда каждого арифметико-логического блока ( Р + 2)-и группы устройства, управляющие входы каждого арифметико-логического блока в 6-й группе устройства, кроме первой объединены и подключены ко второй управляющей шине устройства, выход п-го разряда регистра множителя подключен ко входу переноса п/2-го арифметико-логического блока второй группы устройства,третья управляюща шина устройства подключена к третьи группам входов всех арифметико-логических блоков всех групп устройства, кроме первой, выход арифметикологического блока Р -и группы устройства и выходи ()-х младших разрядов первых арифметико-логических блоков каждой группы являются выходми устройства.

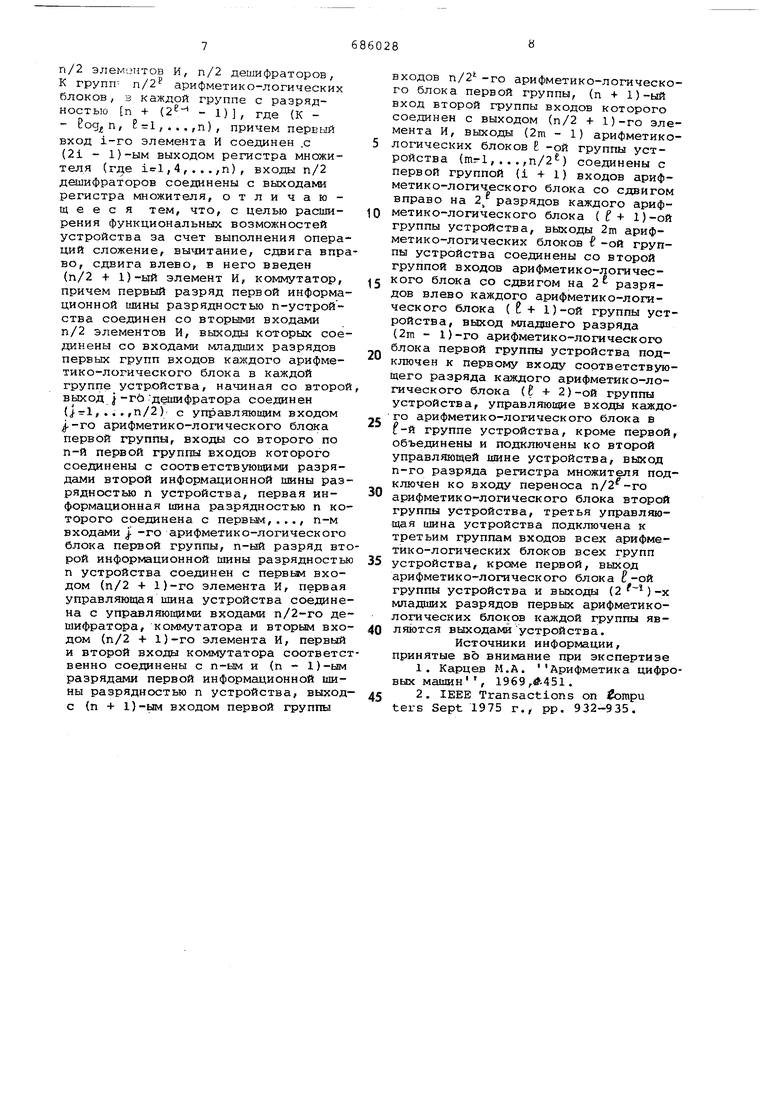

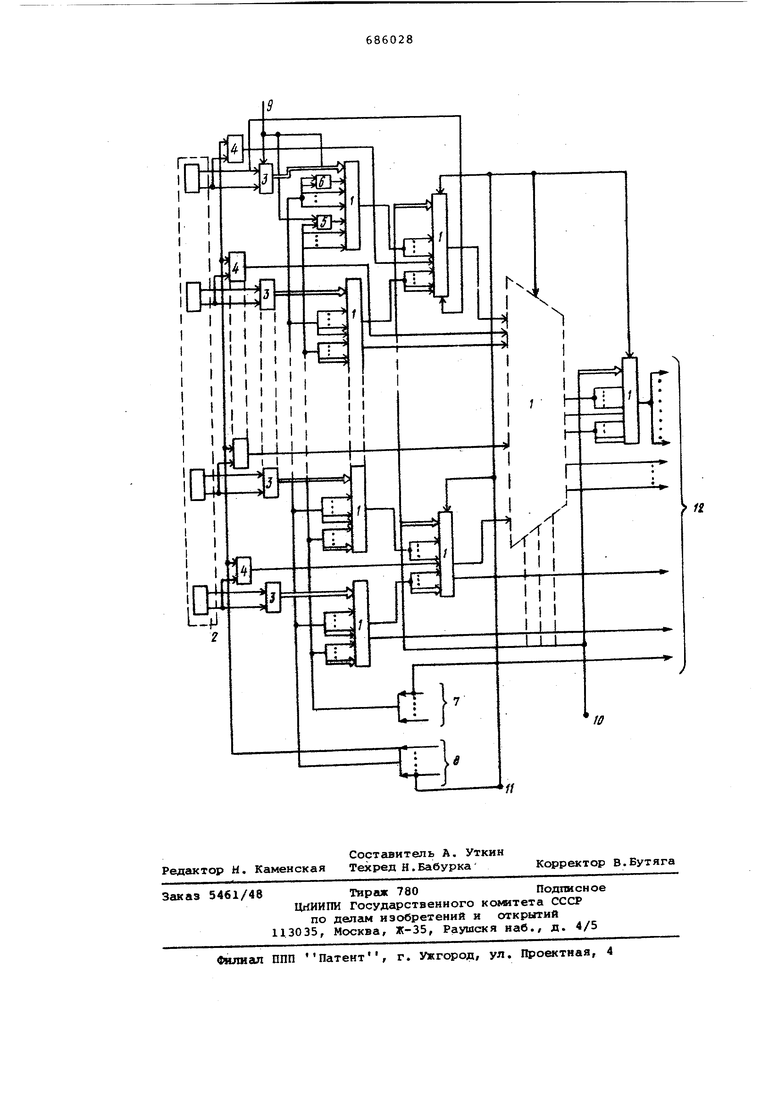

На чертеже представлена схема вычислительного п-разрядного устройства, где арифметико-логические блоки (АЛБ) - 1, регистр множителя - 2, дешифраторы - 3, элементы И - 4, 5, коммутатор - 6, инфорглационные входы - 7, 8, управляющие входы - 9, 10, 11, выход устройства - 12.

Каждая пара разрядов регистра множителя подключена к двум входам дешифратора 3, на четырех выходах которого формируется соответствую1ДИЙ код настройки для данного параллельного АЛБ первой группы устройства. В зависимости от состояния разрядов множителя дешифраторы формируют коды настройки, соответственно равные функциям четырехразрядного АЛБ: О,А, 2А, А+В. Для п/2 -го АЛБ первой группы устройства коды настройки дополнительно будут иметь еще функции А и В. Значения кодов настройки и функции АЛБ от значений разрядов множителя показаны в таблице. На входы 7 и 8 могут поступать как разные числа А и В, так ij коды множимого: прямой и со сдвигом вправо на один разряд.

Таким образом, при умножении на входы всех АЛБ первой группы устройства поступают коды А и А/2. Соответственно для функций четырехразрядного АЛБ это будет В и А. Значение Функции будет соответствовать функции . Следовательно, умножение двух чисел в предлагаемом умножителе осуществляется на два разряда множителя, каждое АЛБ первой группы устройства обрабатывает два частичных произведения, соответствующих разрядам множителя. Поэтому для дальнейшего сложения частичных произведений необходимо младшую сумму частичных произведений сдвинуть вправо на i разрядов по отношению к старшей полученной сумме частичных произведений .

Для сложения частичных сумм и предназначены следующие группы устройства, управляюгдие входы АЛЕ которых настроены при ут ножении на реализацию функции .

Числа поступают в устройство в дополнительном коде, где стагжшй разряд - разряд знака.

Работа устройства заключается в след тощем.

Умножение . В регистр множителя записывается значение кода множителя, который, анализируясь дешифраторами 3, превращается в коды настройки параллельных АЛБ первой группы устройства. На вход 9 подается код операции умножения. Одновременно с этим, на входы множимого 7 и 8 поступают коды множимого А и А/2 соответственно. Проходя через все строки умножителя, код множимого и его частичные суммы формируют на выходе устройства результат, который совместно с соответствующими выходами первых АЛБ каждой группы, как показано на чертеже, и с младшими разрядами множимого образуют полноразрядный результат произведения. Для правильного формирования окончательного произведения через элементы И 4 на соответствующие входы параллельных АЛБ 1 каждой группы устройства поступает значание младшего разряда множимого в зависимости от значения соответствующего разряда множителя. При необходимости можно с выхода умножит ля снимать п-разрядньгй результат и 2п-разрядный результат. При , по алгоритму у ножения чисел, заданных в дополнительном коде, необходимо из конечной суммы произведения вычесть код множимого. Для этого n/2-й дешифра тор вырабатывает коды настройки п/2 tsM АЛБ, указанные в таблице. При A-iO и , из алгоритма умножения чисел, основанного на ра ширении разрядной сетки, следует, что необходимо заполнить старшие разряды каждого частичного произве дения символами .. В предложен ном умножителе это осуществляется за счет подачи символа о вх ду 11 из УУ (не показанного на чер теже) / в те старшие разряды АЛБ всех групп, кроме первой, которые равны сдвигу между входами А и В. Причем эта вырабатывается в зависимости от знака множимого. Сдвиг вправо. В этом режиме-код числа поступа на входы АЛБ первой группы устройс ва с входов как 7, так и 8. В регистр 2 записывается код настройки например, 000.. 10..00, благодаря ко торому какой-либо дешифратор 3 выра батывает код настройки, равный или . Коды настройки для управляющих шин остальных групп устройст ва равны , где А или В равны нулю. Таким образом, наличие символ в одном из разрядов регистра 2 позволяет осуществить сдвиг кода числа на любое число разрядов от 1 цо п. При этом результат сдвига снимает со старших разрядов умножителя . В случае когда число прложительное или отрицательное, из УУ поступает соответственно О или осуществляя тем самым обычный или модифицированный сдвиг вправо. Сдвиг влево. В этом режиме, как и в предыдущем, в регистр 2 записывается управляющее слово, например, 000. .10, .00. На управляющие шины остальных групп устройства подается код настройки равный , где или А или В равны нулю. Результат сдвига влево от 1 до (п - 1) снимается с млад ших разрядов устройства. Сложение. Для осуществления режима сложения чисел, заданных в дополнительном коде, на входы 7 и 8 поступают соответственно числа А и В на управ ляющий вход 9 поступает код операции сложения, который разрешает про хождение через элемент 5 и коммутатор б сигнала, равного 16-му разряду входов 7 и 8. При этом на вход И подается символ О В регистр 2 записывается управляющее слово, которое формирует под действием сигнала со входа 9 на выходе п/2-го дешифратора код настройки, рашный А+В. Полученный результат сложения, в виде (п + 1)-разрядного кода с выхода АЛБ первой строки поступает на вход А п/2-го АЛБ следующей группы, которая настроена на функцию передачи кода, т.е. , Далее процесс прохождения кода через остальные группы устройства будет аналогичен второй группе, коды настройки этих групп также будут равны . Результат сложения снимается с выхода старших разрядов устройства в дополнительном коде. Вычитание. Операция вычитания выполняется аналогично операции сложения, но при этом n/2-й дешифратор вырабатывает код настройки, равный F A-B-1 с подачей на вход переноса п/2-го АЛБ первой группы устройства симвоТаким образом, как при сложении, так и при вычитании, на выходах устройства формируется (п + 1)-разрядный код результата. Из описания работы устройства следует, что оно может выполнять, кроме операции умножения чисел в дополнительном коде, также операции сложения, вычитания, модифицированные сдвиги вправо и сдвиг влево на 2 разрядов, а также логические операции , , . При усложнении п/2-го дешифратора множитель может выполнить полный набор арифметических и логических пераций. Для выполнения операции ычитания (А-В) на вход п/2-го деифратора из управления поступает игнал, которьй совместносо значеиями разрядов множителя, вырабатыает код настройки F A-B-1. Таблица де Х| - значение предыдущего разряда множителя, Х|( - значение последующего разряда множителя. Формула изобретения Вычислительное п-разрядное устройтво, содержащее регистр множитепя,

n/2 элем итов и, n/2 дешифраторов, К групп п/2 арифметико-логических блоков, в каждой группе с разрядностью п + ( - 1), где (К - , ,...,n), причем перВЕлй вход i-ro элемента И соединен .с (21 - 1)-ым выходом регистра множителя (где ,4,. .. ,п), входы п/2 дешифраторов соединены с выходакш регистра множителя, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения операций сложение, вычитание, сдвига вправо, сдвига влево, в него введен (п/2 + 1)-ый элемент И, коммутатор, причем первый разряд первой информационной шины разрядностью п-устройства соединен со вторыми входами п/2 элементов И, выходы которых соединены со входами 1лладших разрядов первых групп входов каждого арифметико-логического блока в каждой группе устройства, начиная со второй выход I-гбдешифратора соединен (J ,... ,п/2 ) с управляющим входом -го арифметико-логического блока первой группы, входам со второго по п-й первой группы входов которого соединены с соответствуюьщми разрядами второй информационной шины разрядностью п устройства, первая информационная шина разрядностью п которого соединена с первьм,. .., п-м входами ji -го арифметико-логического блока первой группы, п-ый разряд второй информационной шины разрядностью п устройства соединен с первьам входом (п/2 + 1)-го элемента И, первая управляющая шина устройства соединена с управляющими входами п/2-го дешифратора, коммутатора и вторым входом (п/2 + 1)-го элемента И, первый и второй входы коммутатора соответственно соединены с п-ым и (п - 1) разрядами первой информационной шины разрядностью п устройства, выходс (п + 1)-ым входом первой группы

входов арифметико-логического блока первой группы, (п + 1)-ый вход второй группы входов которого соединен с выходом (п/2 + 1)-го элемента И, выходы (2т - 1) арифметикологических блоков Е -ой группы устройства (т:-1, . . .,п/2) соединены с первой группой (1+1) входов арифметико-логического блока со сдвигом вправо на 2/ разрядов каждого арифO метико-логического блока ( f + 1)-ой группы устройства, выходы 2т арифметико-логических блоков -ой группы устройства соединены со второй группой входов арифметико-логичес5 кого блока со сдвигом на 2 разрядов влево каждого арифметико-логического блока (6 + 1)-ой группы устройства, выход младшего разряда (2т - 1)-го арифметико-логического

Q блока первой группы устройства подключен к первому входу соответствующего разряда каждого арифметико-логического блока (6 + 2)-ой группы устройства, управляющие входаз каждоe ГО арифметико-логического блока в f-й группе устройства, кроме первой, объединены и подключены ко второй управляющей шине устройства, выход п-го разряда регистра множителя подключен ко входу переноса

арифметико-логического блока второй группы устройства, третья управляющая шина устройства подключена к третьим группам входов всех арифметико-логических блоков всех групп

5 устройства, креме первой, выход арифметико-логического блока -ой группы устройства и выходы (2 )-х младших разрядов первых арифметикологических блоков каждой группы яв0 ляются выходамиустройства.

Источники информации, принятые во внимание при экспертизе

1. Карцев М.А. Арифметика цифровых машин , 1969,-451.

52. IEEE Transactions on fompu

ters Sept 1975 г./ pp. 932-935.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОБРАБОТКИ НЕЧЕТКОЙ ИНФОРМАЦИИ | 1998 |

|

RU2158441C2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU932489A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Операционное устройство мультимикропроцессорной системы | 1982 |

|

SU1107128A1 |

| Устройство для умножения @ -разрядных чисел | 1982 |

|

SU1111153A1 |

| Устройство для умножения | 1979 |

|

SU817701A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения по модулю 2 @ -1 @ | 1985 |

|

SU1304018A1 |

Авторы

Даты

1979-09-15—Публикация

1977-05-16—Подача