113

Изобретение относится к автоматике и вычислительной технике и может быть исполЬзопано в преобразующих устройствах специализированных вычислительных машин, оперирую Щ1х в двоич- fioft системе исчисления и выдающих результат обработки информации в десятичной системе.

Цель изобретения - повьпиение быст

родеыствия и расширение функциональных возможностей за счет получения единичного позиционного кода тетрады

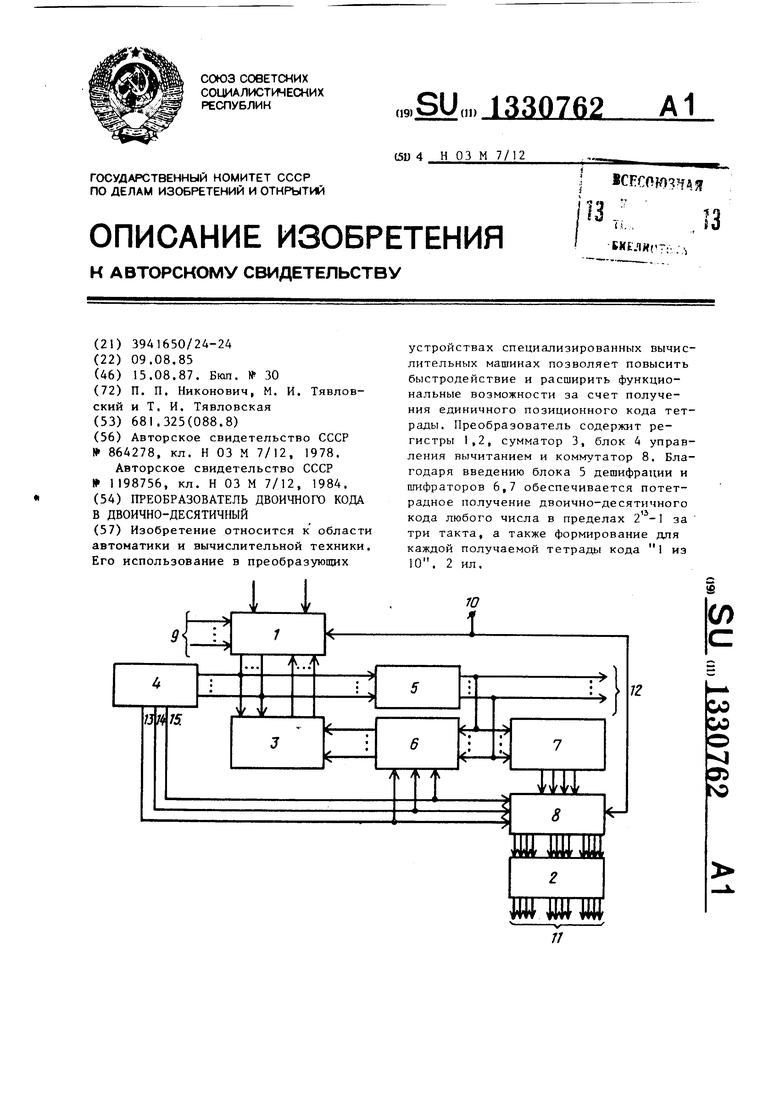

На чертеже изображена блок-схема преобразователя.

Преобразователь двоичного кода в двоично-десятичный содержит первый и второй регистры 1 и 2, сумматор 3 блок 4 управления вычитанием, блок 5 деш1 фра1ши, первый и второй шифраторы 6, 7 и коммутатор 8. На фиг. 1 обозначены информационные и тактовый входы 9 и 10, первые и вторые выходы I и 12, а также выходы 13 - 15 блока | управления вычитанием.

Блок 4 управления вычитанием идентичен аналогичному блоку прототипа и служит для анализа всех разрядных входов информационного кода преобразователя, поступающих от регистра 1 YcjiOBHe формирования сигналов признаков тысяч, сотен и десятков на вы- ходлх 13-15 блока А управления вычитанием следующее:

выход 13 cf, 2 V

с -1

.

18

2

2 (2V

v2 - 2Ч2%2Ъ;

1«.1ход 14 Ср,-1р, Г2 + +

-

иыхол 15 Ср f,. (.I j Г 2 + +2 +2 ().

Блок 5 дешифрации служит д,пя формирования единичного позиционного кода, разряды которого формируются в соответствии со следующими условиями :

вьгход девятого (старщего) разряда , + 2 ;2 -(2 +2 ) + 2 2

8,

2Ч2 +2 +2 +2Ч2 - (1 + 2) ;

выход восьмого разряда f , 2 X 2 (2 + 1) + 2 2 (2 + 2 + 2) 2.2(2 + 2) ;

выход седьмого разряда f,f,- х(2 +2 2)+2 2 + 2 (2 + 2.2 ,2)+2 . ((2-+2 « 2)) + 2 °.(+2 (1 + 28)У1 ;

выход шестого разряда 4, f г ,f,. Г 2 -2 -2 +2 2 () + 2М( 1 241+2 -(1+2 )) +2 - 2 ;2 «

«2(2 +2 2)-t-2 1+2 ( + (H2(l+2 )))j ;

выход пятого разряда ,, t,

fj f

, 2 2((l+2

f j f f , Г2

(2 -t-2/+2 ) 2

(l+2 )+2 .

2. 2 (2 +2 -t-2 + 2)+2 (H-2 (K2 (1 + 2(1-ь2)))) ;

выход четвертого разряда f f/

(2 +2 )+2 2 (1+2Ч1+2)) 2 °- 2 2

+

2 ()+2 .1+2 (l-t-2. (1+2 )) , выход третьего разряда f7 f, f

X f:

f.-f.

5

0

I, 2 . 2 + +2П2 -( 2) +2 2 2« 2 X (2 +2 - 2)+2 . (1+2 (1+2(1-1- 2)));

выход второго разряда ,- f « ,-f,.(24242.2) + )+2 ( (1+2 ) +

f,-f.

+ 2 2 (

+2 °- 2- 2-(2 +2 ) + 2.1 + 2%

.(( (1+2«.(1+2 )))1, ;

выход первого (младшего) разряда .. f,.fv fv . fr f8« +2 (2 +2 + 25 . () + + 2 (I+2 +2 - 28- 2.(2 + 2) + + (H24l + 2(l+2 ))-) .

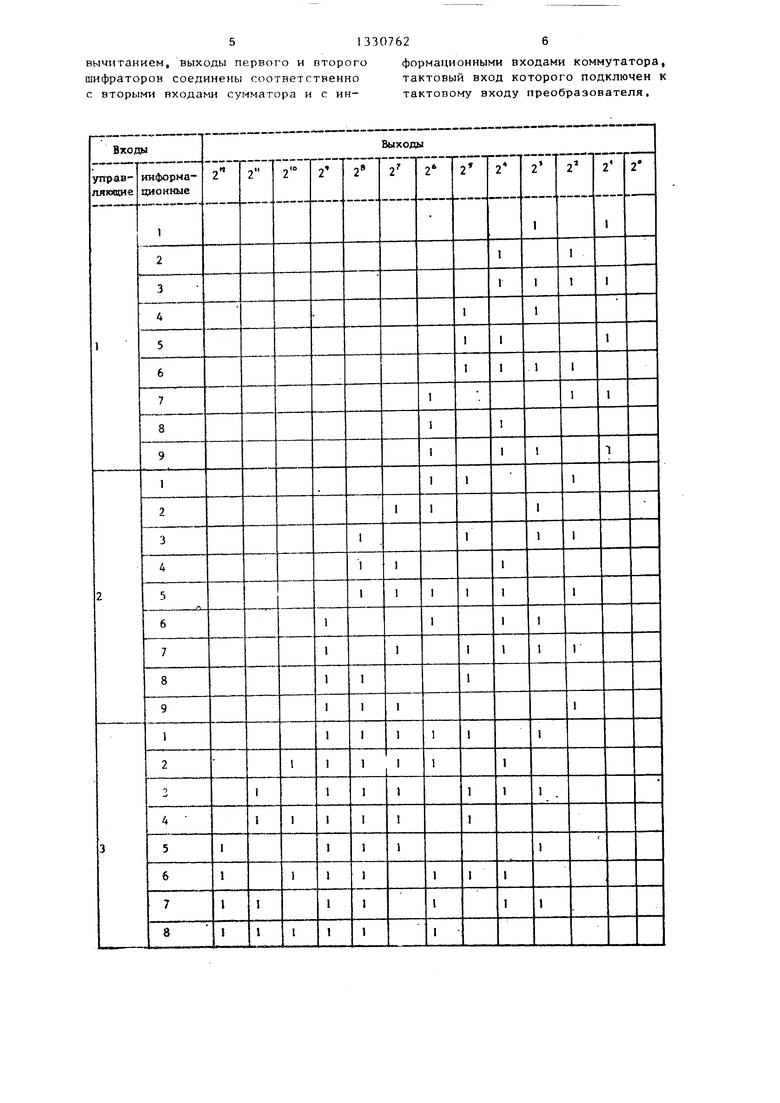

Первый шифратор 6 работает в соответствии с таблицей истинности. 0 При этом на его управляющие входы с первого по третий поступают сигналы соответственно tp - ср с блока 4, а на информационные входы с первого цо девятый - сигналы соответственно fg-f, с блока 5. При этом при появлении на информационных входах шифратора 6 единицы, например в первом разряде f9, а на управляющих входах также в первом разряде () , на выходе шифратора 6 формируется двоичный код числа тетрады с наличием единицы в разрядах 2 и 2 , что соответствует числу 10. Р сли поступят

5

0

сигналы f.. иср.

то выходной код

числа тетрады будет принимать значе

ние единица в разрядах 2,2 и 2 , что соответствует числу 100. Если поступят сигналы f, и , , то сформируется число 1000, т.е. наличие единиц в разрядах 2 и 2 - 2.

Второй шифратор 7 служит для преобразования единичного позиционного кода с блока 5 в двоично-десятичный код тетрады.

Преобразователь двоичного кода в двоично-десятичный работает следующим образом.

В исходном состоянии в регистр 1 записано с входов 9 преобразуемое

двоичное число, регистр 2 установлен в исходное нулевое состояние. Число, записанное в регистр 1, анализируется в блоке 4 управления вычитанием. Если анализируемое число содержит тысячи, то появляется сигнал признака тысяч на выходе 13 блока 4, если число не содержит тысяч, а содержит сотни, то появляется сигнал признака сотен

на выходе 14 этого блока 4, а-если оно содержит только десятки, то появляется сигнал признака десятки на выходе 15 блока 4. Одновременно осу- ществляется анализ разрядов двоичного числа в блоке 5 дешифрации, в котором формируется единичный позиционный код тетрады. Этот код поступает на входы 12 преобразователя и на входы шифраторов 6 и 7. В шифраторе 6 с учетом признаков тетрады, поступающих на его управляющие входы с блока 4, формируется двоичный код тетрады. Этот код поступает на вхо- ды сумматора 3, где вычитается из числа, поступающего на его другие входы от регистра 1.

При поступлении импульса тактовой частоты с входа 10 на тактовый вход регистра 1 результат вычитания из сумматора 3 заносится в регистр для дальнейшего преобразования. Операция вычитания повторяется с приходом каждого импульса тактовой частоты и осуществляется до тех пор, пока число в регистре 1 не станет меньше десяти.

Десятичный код тетрады с выхода блока 5 преобразуется в двоичный код тетрады в шифраторе 7. Этот код тетрады через коммутатор 8, управляемый сигналами признака тетрады, которые поступают от блока 4 управления вычитанием, и синхронизируемый импульсами тактовой частоты, которые поступают с входа 10 преобразователя, поступает на соответствующие входы регистра 2 для временного хранения. По каждому импульсу тактовой частоты в регистр 2 заносится одна тетрада двоично-десятичного числа. Двоичный код тетрады единиц формируется в регистре 1. Так, например.

число 7895 преобразуется за 3 такта, 55 первого и входами второго шифрапричем в первом такте формируется двоичный код числа 7 (0111) и сигнал признака тысячи, который коммутирует этот код на входы регистра 2

торов и являются вторыми выходами преобразователя, управляющие входы первого шифратора подключены к соответствующим выходам блока управления

в тетраду тысяч. Во втором такте формируется двоичный код числа 8

(1000)и признак сотен, который коммутирует этот код в тетраду сотен регистра 2. По третьему такту формируется двоичный код числа 9

(1001)и сигнал признака десятки. Этот код поступает в регистр 2 в тетраду десятков. Двоичный код единиц, равный 5 (0101), формируется в регистре 1 по третьему такту.

Таким образом, быстродействие данного преобразователя вьппе, чем в прототипе, так как преобразователь тринадцатиразрядных двоичных чисел осуществляется всегда за 3 такта. Кроме того, обеспечивается формирование единичного позиционного кода каждой тетрады н десятичном формате, т.е. кода 1 из 10, что расширяет функциональные возможности преобразователя.

Формула изобретения

Преобразователь двоичного кода в двоично-десятичный, содержащий первый регистр, выходы которого подключены к соответствующим входам блока управления вычитанием и к первым входам сумматора, выходы которого соединены с информационными входами

первого регистра, выходы блока управления вычитанием подключены к управляющим входам коммутатора, выходы которого соединены с входами второго регистра, выходы которого являются

первыми входами преобразователя, установочные и тактовый входы первого регистра являются соответственно информационными и тактовым входами преобразователя, отличаюЩ и и с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет получения единичного позиционного кода тетрады, в преобразователь введены

шифратор и блок дешифрации, входы которого подключены к соответствующим выходам первого регистра, выходы блока дешифрации соединены с соответствующими информационными входаторов и являются вторыми выходами преобразователя, управляющие входы первого шифратора подключены к соответствующим выходам блока управления

вычитанием, выходы первого и второго шифраторов соединены соотБетственно с вторыми входами сумматора и с информационными входами коммутатора, тактовый вход которого подключен к тактовому входу преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1448412A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1974 |

|

SU620975A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1975 |

|

SU708344A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичных кодов в двоично-десятичные | 1984 |

|

SU1200428A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1084779A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый КОд | 1979 |

|

SU849199A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1300640A1 |

Изобретение относится к области автоматики и вычислительной техники. Его использование в преобразующих устройствах специализированных вычислительных машинах позволяет повысить быстродействие и расширить функциональные возможности за счет получения единичного позиционного кода тетрады. Преобразователь содержит регистры 1,2, сумматор 3, блок 4 управления вычитанием и коммутатор 8. Благодаря введению блока 5 дешифрации и шифраторов 6,7 обеспечивается потет- радное получение двоично-десятичного кода любого числа в пределах 2-1 за три такта, а также формирование для каждой получаемой тетрады кода 1 из 10. 2 ил. Шшгж WrT ТТт

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Авторское свидетельство СССР 1198756, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-08-15—Публикация

1985-08-09—Подача