(54) УСТРОЙСТВО ДЛЯ ВЫЧИТАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1978 |

|

SU736098A1 |

| Устройство для вычитания | 1979 |

|

SU851403A1 |

| Устройство для вычитания | 1978 |

|

SU746513A1 |

| Устройство для вычитания | 1978 |

|

SU811249A1 |

| Устройство для вычитания | 1979 |

|

SU789992A1 |

| УСТРОЙСТВО ВЫЧИТАНИЯ | 1972 |

|

SU435523A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| МНОГОКАНАЛЬНЫЙ КОРРЕЛЯТОР | 1973 |

|

SU387370A1 |

| Устройство для сложения-вычитания | 1981 |

|

SU1005037A1 |

| Следящий аналого-цифровой преобразователь | 1988 |

|

SU1594691A1 |

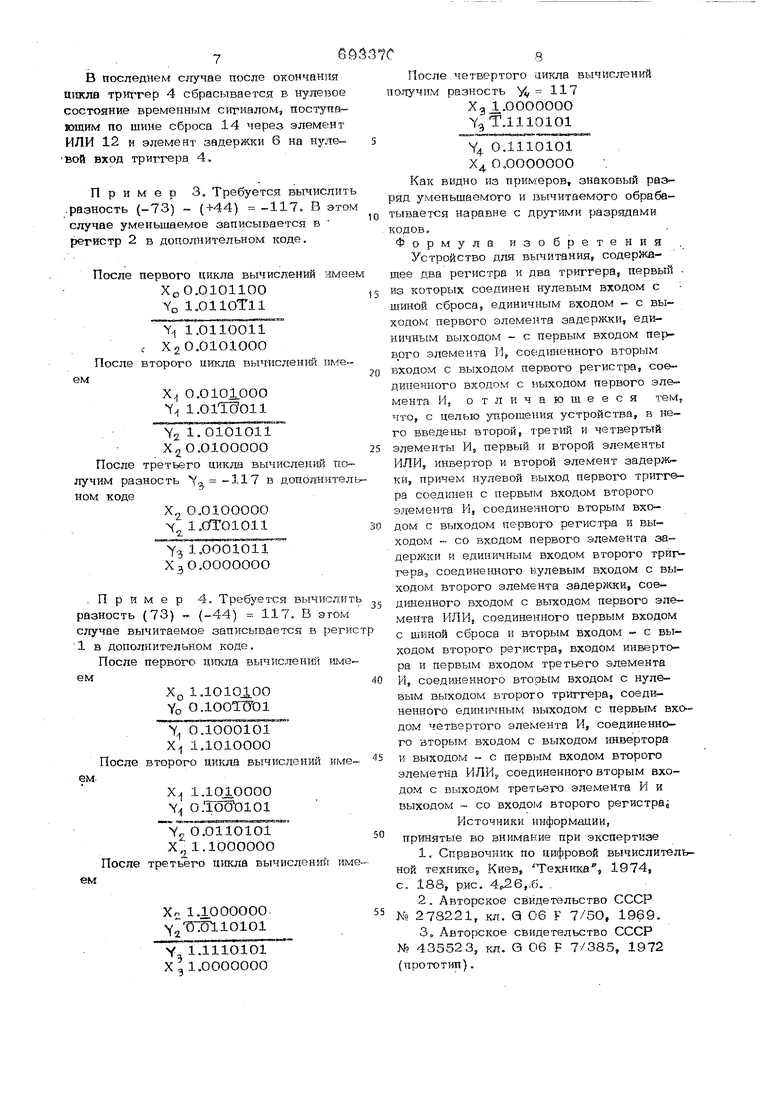

. -I. Изобретение относится к области вычислительной техники. Известны устройства для вычитаии5а, собранные на дбух регистрах (уменьшаемого и вычитаемого) и одноразрядном вычитатепе на три входа 1. Недостатком таких устройств являеч ся сложность реализации вычитатепя. Известнь более простые устройства вычитания, в которых отсутствует вычвтатель 2. Наиболее близким к предлагаемому является устройство для вычитания, содержащее дв1а регистра и два триггера, первый из которых соединен нулевым входом с шиной сброса, единичным вхорям - с выходом первого элемента зйдержки, единичным выходом - с первым входом первого элемента И з. Недостатком такого устройства является относительная сложность схемь сум матора на три входа, который входит в состав устройства. Цель изобр1етеййя - упрощение yci ррйства дпя вычитания. Указанная аельдоститаётря тем, что в устройство введены второй, третийи четвертый элементы И, первьй и вторсЛ элементы ИЛИ, инвертор и вторсй элемент задержки, «ричем нулевой выход первого триггера соедшюн с первым входом второго элемента И, подклютенного вторым входом к выходу йерйого регистра и выхо дом - ко ътфау иервого элемента задержки и единичнсму йхЬду Ьторого триггера, соединенного нулевым входом с выход(м второго элемента задержки, связанного входом с выходбм первого элемента ЙЛ1 соединенного первым входом с шиной сброса и вторым входом с выходом второго регистра, вход инвертора и первым входом третьего элемента И, подклюпеняого вторым входом Jc нулевому выходу второгч триггера, соединенного единич1шм выходом с перВ1ь1М входом четвертого элемента И, связанного вторым входом с выходом инвертора и выходок - с первым входом второго элемента ИЛИ,соединенного вторы входом с выходом третьего элемента И и выходом - со входом второго регистра. На чертеже изображена структурная схема устройства для вычитания. Ус тройство сод&ржит- два регистра 1 и 2, два триггера 3 и 4, два эадер жи 5 и 6, ЧётБтре двухвходовых :эпемента И 7-lP инвертор 11, два даухбтгодЬвЫХ элемента ИЛИ 12, 13 и шину сброса 14. Единичный вьгход триггера 3 связан Спёр вымШрДом элемента И 7, срединен вбгб BTOpfeiM ;вхЬдом с выходом регистра 1/ noflJmicweHHbro входом к выходу эле;,м;ента 1Л 7. -: , : . ; -. .. , .. .,, , . : ; Нулевой выход триггера 3 соединен с рервым входом элемента И 8, пьдклк }ённогр ёто{ ым ;входЬм к вьгходу регистра 1. единичный вход триггера 4 связан . ср вхрдом элемента 1задержки 5 и ёрХРдом эпемёнта И 8. ЁыходэлёШТнта задержки. 5 средйнен с единичным входов триггера 3. Нулевой вход триггера 4 связан с выходом эяементй задержки 6, сЬеййнейн го входом с еь1ходом ; элемента ИЛИ 12, подключённого перв:ым входом к Шине сброса и istopbiM входрм - к выход : регистра 2, иерврму входу элемента И 0 и входу инвертора 11. . Ёдинйчнь1й вьтход триггера 4. сшзан с первым входом элемента И 10, Ьоедв н нногр втРрьш вхс4оК с выхрдом ив- . вертора 11. Шщод элемента И 10 связ ан с иервйм входом элемента , сбёдйнензого BTppbiM ВХОДОМ: с выхрдом элемента И 9, пбдтотюченярго вторым вхо дом к нулбвойу вь1Ходу триггера 4. Выход элемента ЙЛИ 13 соединен; со входом регистра 2. Нулевого вход триггера 3 подключен к шине cdpoca 14. Устройстводля вычитания работает следующ 5М образом. В ЙСХРДЕ10М состо-агнии устройства три1 геры 3 и 4 усташйлйвак) нулёвре еос:т6яниё Сйгйайрм, йрступайшш по шин сброса 14. В регистр 1 по сийхрънизиру юшйм йм зульсак тактовой частотьг последо тедьно, начиная с младпгих разрядов, запись1&йетс а дзвойч оый 1с6д вьлчйтаемого; а в регистр 2 двойчнь5й код уменыпаемо го заносится по Синхронизирующим нм:цуаьсакя, задержанным на прлперкода отйрснтельно синхронизирующих импульсов ;й;гистра 1, На шину сброса 14 поступае Серия Временных сигналов, совпадающая со временем считывавгас с вь1хода регистра 2 последнего Л--го разряда. Двоичные коды вычитаемого считываются с выхода регистра 1 последовательно, начвнйя с младшего разряда. Так Как исходном состоянии триггер 3 находится в нулевом состоянии, то элемент И 7 закрыт единичным выходом триггера 3, а элемент И 8 открыт нулевым выходом триггера 3. Со Сдвигом на полпериода тактовой часто1ы с выхода регистра 2 считывается последРвательно, начиная с младnieiro разряда, двоичньгй код уменьшаеМогр, который через элемент И 9, открытый нулевы л выходом триггера 4 и элемент ИЛИ 13 (элемент И 10 заКрЫТ единичным выходом триггера 4) поступает на взсод рэгистр 2. / i Таким образРм, мйадшйё разряды Згменьшае1Й1ог6 переписываются без йзме- нения с выхода регистра 2 на его Вход До тех прр, пока триггер 4 не перейдет в ёддаичное состояние. Триггер 4 установится в единичное . ; срстояние первой мдадшей единицей дво. кода вычиШемого, кРторая с выхода регистра 1 через элемент И 8, от крытый нулевым выходом триггера 3, поступает На единияный вход триггера 4 )1 вход элемен%1 задержки 5. Первая-млаййюя единица двоичного кода вь1Чйтаек ргой выхода регистра 1 на еро Вход не йостуИйт, так как элемент И 7 в это BfieMa закрыт единичным; Tfinrrepa 5. Однако, все другие |)аэряды двойЧногЬ 1к6да вы1Итаемогр после первой младшей единицы перепишутся с выхода регистра 1 на его вход без иэ 1ен:ения через элемент И 7, открываемый единичньтм выходом триггера 3 после поСтуплейия на его единичный вход импульса первой ёДИ нинь1 вычитаемого с выхода элемента 5 задержки йапол гериода тактовой частоть.. После установки триггера 3 в ёдйнйчнбе состояние элемент ИВ ййкрЙЫётей, заттрёййя поступление импульсов с выхода регистра 1 йа единичный вход триггера 4. После перехода триггера 4 по И мпульсу первой младшей единицы вычитаемогч) в единичное состояние элемент И 9 закрывается, а элемент И 10 открьсвается и начинает п|оопускать инвертированный двоичный код уменьшаемого С выхода регистр 2 на его вход через инвертРр 11, элемент. И 10 и мент ИЛИ 13. Инвертированный код уменьшаемого пасывйется в регистр 2 до тех пор. пока на выходе регистра 2 не появитгся первйя единица двоичного кода уменьшаемого. ИмпулЬс первой (считая с номера разряда уменьшаемого, совпадающего с номером разряда младшей единицы вычи- s таемого) единицы уменьшаемого rtociynaет с выхода регистра 2 на закрытый нулевым выходом триггера 4 элемент И Q, на вход инвертора 11 и через элемент ИЛИ 12 на вход элемента 6 задерзкки 0 на полпериода тактовой частоты. Этот импульс с помощью инвертора 11 закр(ет элеменч- И 1О, вследствие чего на вход регистра 2 импульс в этом разряде не поступит. Спустя полпёрйода тактЬвой частоты, импульс первой единицы уменьшаемого с выхода элемента задер(Ки 6 поступит на нулевой вход триггера 4 и установит его в нулевое состояние. После возврата триггера 4 в нулевое состояние все последующие разряды уменьш емого переписываюгся без изменения с выхода регистра 2 через элемент И 9, открытый нулевом выходом триггера 4, и элетмент ИЛИ 13 на вход регистра 2 до последнего п-го разряда включительно. После одного цикла вычислениЙ1 когда одна единица кода вычитаемого уменьщает двоичный код вычитаемого на величину ЭТОЙ единиШ), временной импульс, сов падакиций с окончанием записи последнего Ь-го разряда уменынаемого с вьпсода регистра 2 на его Вход, поступает на шину сброса 14 и возвращает триггеры 3 и 4 в нулевое состояние. В результате устройство возвращается в исходное состояние: триггеры 3 и 4 находятся в нулевом состояний, с выходов регистров 1 и 2 постутаайиг мдадшие разряды двоичных кодов промежуточйьтх вычислений. В следующем цикле вычислений устройство работает аналогично до тех пор, пока в регистре 1 не останется нулевое содерасимое. В этом случае в регистре 5 2 зафиксируется двоичный код разйости, а триггеры 3 и 4 бущгт Находиться в Щглевом состоянии.. Если уменьшаемое меньше вычитаем1 tOi то разность фиксируется в дополнйтель ном коде. Пример 1. Требуется вычислить разность 73-44 29. Двоичный код вычитаемого XQ d.blOllOO (точкой отделен знаковый разряд) запнсь1вается в регистр 1, а двоичный код уменьшаемого Vo 0.1О01О01 - в регистр 2. ко тр ны ге ва ле то 4 со ед то да ги по ва пр ем ты лу ра Ч Триггер 3 младшую единицу а вычитаемого, которая переводит ггер 4 в единичное состояние. Двоичкод уменьшаемого до установки три1%а 4 в единичное состояние переписытся в регистр 2 без изменения, а посустановки триггера 4 в единичное соо ние инвертируется до сброса триггере нулевое состояние. Триггер 4 сбрасывается в нулевое тояние после инвертирования первой ницы уменьшаемого. При нулевом соснии триггера 4 остальные разряды коуменьшаемого переписываются в ре- тр 2 без изменения. Таким образом, ле первого цикла вь1чйслений имеем XoO.QlOll.OO YO o.iooTOoi О.10О01О1 Х|О.О1О1ООО В коде вычитаемотю подчеркнута nei младшая единица, начиная с которой исходит инвертирование кода уменьшатх), а в коде уменьшаемого подчеркнуразряды, подлежащие инвертированию. Во втором цикле вычислений получим х o.oiojboo V 0.106О101 . Vi O.OllliOl X20.0100000 После третьего цикла вычислений поим двоичньгй код разности Yj - 29 X,O.O100OOO ХзО.ОТ111О1 Y,j О.О01И01 х 0.0000000 Пример 2. Требуется вычислить ность 44 - 73 -29. В первом цикле вычислений имеем Хо 0.1ОО1О01 YO O. Y| 0.0101011 х o.iooiopo После второго цикла вычислений полу-. .1ооАооо Y O.OlCfIbil YiO.OlOOOll XjiO.lOOOOOO в третьем цикле получаем разность -29 в дополнительном коде Х20.1ОООРОО Y TOlOOOll .iioooii х,р. ооооооо В последнем случае после ок цикла триггер 4 сбрасывается в cdCToaHHef временным сигналом, ющим по шине сброса 14 через ИЛИ 12 и элемент задержки 6 вой вход триггера 4.. : П р и м е р 3. Требуется .разность (-73) - (+44) -11 случае уменьшаемое записывает регистр 2 IB дополнительном ко После первого цикла вычисл XoO.QlOllOO ; YO i.oiioTii V l.OliOOll f Х20.01О10ОО V Побле второго иикйа вычисл Х O.OlOi.000 Ч i.oiTOoii Yj 1.0101011 х 0.0100000 После третьего цикла вычис луч:им разность Ya -117 в д ном коде Х,О.010ОООО ч,., 1.С/ТО 011 ; Y3 -CK oi6ii ХзО.ООООООО /Пример 4. Требуется разность (73) - (-44) 117 сЭтучйе вычитаемое записываетс ;1 в дополнт1те:льн6м коде, После первого цикла вычисл ем : -.. ;. :„ :. Х, l.lOlOiOO SV, O.lOOTDtil Y/O.IOOOIOI Х 1.1010006 После второго цикла рычисл Х IjMpiOOO Y одШ)101: Yg 0.0110101 X 2 1.1(300000 После третьего цикла вычис Хо 1.1.000000 10101 V 1.1110101 .ooooooo После четвертого цикла вычислений получим разность % 117 Хз1..0000ООО YaT.l 110101 У О.1110101 Х О-ООООООО . Как видно из примеров, знаковый раэряй уменьшаемого и вычитаемого обрабатывается наравне с другими разрядами Кодов. Формула и 3 о б р е т е ни я Устройство Для Вычитания, содерйсащее два регистра и дёа триггера, первый из которых соединен нулевым входом с шиной сброса, ёдинйчнь1М входом - с выходом первого элемента задержки, единичным выходом - с первым входом первого элемента И, соединенного вторым ёхбдом с вьосодом первого регистра, соединенного входом с вьгходбм первого ЭЛ&мента И, 6 т л И а Ю щ е е с я тем, что, с целью упрощения устройства, в него введены второй, третий и четвертый элементы И, первый и второй элементы ИЛИ, инвертор и второй элемент задержки, прйчётм нулевой выход Первого триггера соединён с пер1Вйм входом второго элемента И, соединенного вторым входом с выходом первогб регистра и выходом - со входом первого элемента задержки и единйчньтм входом второго трйт гера, соединёшот о нулевым входом с выходом второго элёМейта задержки, соединенного входом с выходом пёрйого элецента ИЛИ, соединенного первым входом с шиной сброса и вторым входом - с выходом второго {зег истрй, взЛОдом инвертоjpa и первым взсЬдой третьего элемента И, соединённого вторым входом с нулевым выходом второго триггера, соединенного единичным вьЬсодом с первым входом четвертого элемента И, соединенного вторым йходом с выходом инвертора и выходом - с первым входом второго элеметна ИЛИ, соединенного вторым входбм с выходом, третьего элемента И и в;ь1ходом - со входом второго регистра; . Источники информации, принятые во внимание при экспертизе 1.Справочник по цифровой вычислительной технике, Киев, Техника , 1974, с. 188, рис. ,.б. . 2.Авторское сйидетёльство CQCP MO 278221, кл. Q 06 F 7/50, 1969. 3.Авторское свидетельство СССР № 435523, кл. G 06 F 7/385, 1972 (прототип).

Авторы

Даты

1979-10-25—Публикация

1977-06-28—Подача