Изобретение относится к вычислительной технике и предназначено для вычитания двух чисел.

Известны устройства для вычитания, содержащие два регистра (уменьшаемого и вычитаемого) и одноразрядный вычитатель 1.

Недостаток таких устройств - сложность реализации вычитателя.

Известны более простые устройства для вычитания, в которых отсутствует вычитатель, а функцию вычитания выполняют одноразрядный сумматор на три входа и два триггера 2.

Недостаток этих устройств - относительная сложность схемы сумматора на три входа.

Наиболее близким к предлагаемому является устройство для вычитания, содержащее два регистра и два триггера, первый из которы.х соединен нулезым вводом с шиной сброса, единичным входом с выходом первого элемента задержки, единичным выходом с первым входом первого элемента И, соединенного вторым входом с выходом первого регистра, соединенного входом с выходом первого элемента И, причем нулевой выход первого триггера соединен с первым входом второго элемента И, соединенного вторым входом с выходом первого регистра и выходом - с входом первого эле-, мента задержки и единичным входом второго триггера, соединенного нулевым входом с выходом второго элемента задержки,соединенного входом с выходом первого элемента ИЛИ,соединен10ного первым входом с шиной сброба и вторым входом - с выходом Второго регистра, входом инвертора и первым входом третьего элемента И, соединенного вторым входом с нулевым выходом

15 второго триггера, соединеного единичным выходом с первым входом четвер- . того элемента И, соединенного вторым входом с выходом инвертора и выходом - с первьам входом второго

2Q элемента ИЛИ, соединенного вторым входом с выходом третьего элемента И и выходом - со входом второго регистра 3) ,

25

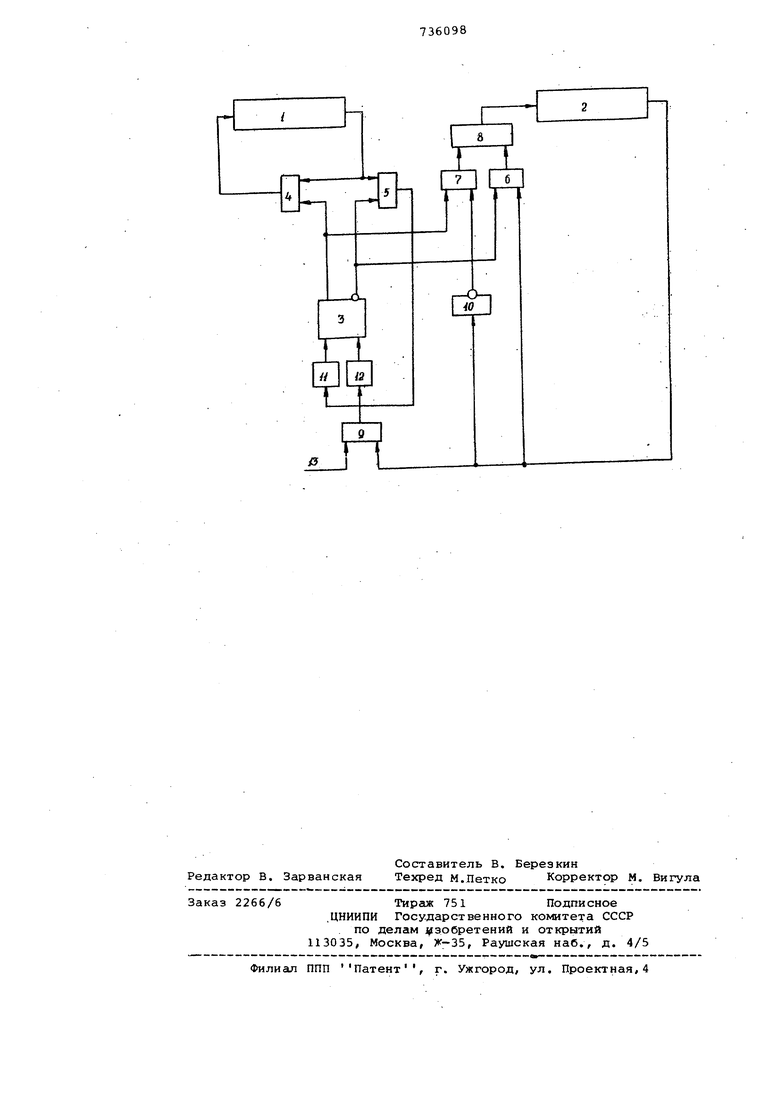

Недостатком такого устройства является его относительно невысокое 1 быстродействие вследствие задержки на один цикл каждой единицы вычитаемого во втором триггере. Наличие второго триггера в составе устройст ва также приводит к его усложнению. Цель изобретения - повышение быстродействия и упрощение устройства Поставленная цель достигается тем, что в устройстве для вычитания содержащем дварегистра, триггер, элементы И, ИЛИ и НЕ, причем вход .первого регистра подключен к выходу первого элемента И, первый вход которого соединен с первым входом второго элемента И и выходом первого регистра, вторые входы первого и второго элементов И подключены к еди ничному и нулевому выходам триггера соответственно, выход второго элемента И через первый элемент задержки подключен к единичному входу триггера, входы первого элемента ИЛИ подключены к выходам третьего и чет; вертого элементов И, а выход - ко входу второго регистра, выход которо го подключен к первым входам третьег элемента И и второго элемента ИЛИ и входу - элемента НЕ, выход которого подключен к первому входу четвертого элемента И, второй вход второго элемента ИЛИ подключен к шине сброса, а выход - ко входу второго элемента задержки, выход второго элемента задержки подключен к нулевому входу триггера, нулевой и единичный выходы которого подключены ко вторым входам третьего и четвертого элементов И соответственно. На .чертеже представлена функциональная схема предлагаемого устройства. Устройство для вычитания содержи два регистра 1 и 2, триггер 3, четыр двухвходных элемента И 4-7, два двух входных элемента ИЛИ 8 и 9, элемент НЕ 10, дпа элемента 11 и 12 задержк шину 13 сброса. Триггер 3 соединен единичным выходом с входом элемента И 4 и входо элемента И 7, нулевым выходом - с входом элемента И 5 и входом элемен И б, единичным входом - с выходом эл мента 11 задержки, нулевым входом - с выходом элемента задержки 12. Регистр 1 подключен входом к выходу элемента И 4, выходом - к другим входам элементов И 4 и 5, Выход регистра 2 подключен к входам элементовИ б, ИЛИ и к входу элемента НЕ ДО, соединенного выходом с входом элемента И 7. Выходы элементов 7 подключены ко входам элемента ИЛИ 8, соединенного выходом со входом регистра 2. Выход элемента И 5 подключен к ходу элемента 11 задержки. Вход эл мента 12 задержки подключен к выход элемента ИЛИ 9, соединенного другим входом с шиной 13 сброса. Устройство для вычитания ра&зтае с ледующим образом. В исходном состоянии триггер 3 станавливается в нулевое состояние игналом, поступающим по шине 13 броса. В регистр 1 по синхронизирующим мпульсам тактовой частоты последовательно, начиная с младших разрядов, записывается двоичный код вычитаемого. В регистр 2 двоичный код уменьаемого заносится по синхронизируюдим импульсам, задержанным на полпеиода относительно синхронизирующих мпульсов регистра 1. На шину 13 сброса поступает серия временных сигналов, совпадающая по времени с моментами считывания, с выхода регистра 2 последнего п-го азряда. Двоичные коды вычитаемого считыаю.тся с выхода регистра 1 последоваельно, начиная с младшего разряда. Так как в исходном состоянии триггер 3 находится в нулевом состоянии, то элемент И б открыт его нулевым выходом, а элемент И 7 закрыт его единичным выходом. С выхода регистра 2 считывается последовательно, на;чиная с младшего разряда, двоичный код уменьшаемого, который через элемент И 6, открытый нулевым выходом триггера 3, и элемент ИЛИ 8 поступает на вход регистра 2. Таким образом, младшие разряды уменьшаемого переписываются без изменения с выхода регистра 1 на его вход до тех пор, пока триггер 3 не перейдет в единичное состояние. Триггер 3 устанавливается в единичное состояние первой младшей единицей двоичного кода вычитаемого, которая с выхода регистра 1 через элемент И 5, открытый нулевым выходом триггера 3, поступает на единичный вход триггера 3 через элемент 11 задержки, В результате триггер 3 перейдет в единичное состояние только после окончания действия импульса единицы вычитаемого на выходе регистра 1. Этим обеспечивается стирание первой единицы кода вычитаемого с помощью элемента И 4, закрытого единичным выходом триггера 3. После перехода триггера 3 в единичное состояние элементы И 5 и 6 закрываются нулевым выходом триггера 3, а элементы И 4 и 7 открываются единичным выходом триггера 3. В результате инвертированный с помощью элемента НЕ 10 двоичный код уменьшаемого поступает через элементы И 7 и ИЛИ 8 на вход регистра 2, а двоичный код вычитаемого переписывается без изменения через элемент И 4 с выхода регистра 1 на его вход. Так будет продолжаться до тех пор, пока на выходе регистра 2 не появляется импульс двоичного кода уменьшаемого, который через элемен

ИЛИ 9 и элемент 12 задержки поступает на нулевой вход триггера 3. Элемент 12 задержки задерживает импульс единицы уменьшаемого на время его действия на выходе регистра 2, Этим обеспечивается инвертированиеединицы двоичного кода уменьшаемого с помощью элемента НЕ 10 и элемента И 7, открытого единичным выходом триггера 3.

После перевода триггера 3 в нулевое состояние единичным кодом уменьшаемого элементы И 4 и 7 закрывавэтся единичным выходом триггера 3, а элементы И 5 и 6 открываются нулевым ВЫ ходом триггера 3. В результате двоичный код уменьшаемого с выхода регистра 2 через элементы И б и ИЛИ 8 начинает переписываться в регистр 2 без изменения до тех пор, пока триггер 3 не перейдет в единичное состояние.

Триггер 3 переводится в единичное состояние первой (после установки триггера 3 в нулевое состояние) единицей кода вычитаемого, которая с выхода регистра 1 через элемент И 5, открытый нулевым выходом триггера 3, поступает на единичный вход триггера 3 спустя время задержки элемента 11, Эта единица кода вычитаемого на вход регистра 1 не поступает,так как элемент И 4 закрыт единичным выходом триггера 3.

После перехода триггера 3 в единичное состояние вновь элементы И 5 и б закрываются, а элементы и 4 и 7 открываются. Инвертированный код уменьшаемого с выхода элемента НЕ 10 через элементы И 7 и ИЛИ 8 записывается в регистр 2, а двоичный код вычитаемого с выхода регистра 1 переписывается без изменения в регистр 1 через элемент И 4,

Дальнейшая работа устройства аналогична. При нулевом состоянии триггера 3 двоичный код уменьшаемого переписывается без изменения в регистр 2, а при единичном состоянии триггера 3 в регистр 2 поступает инвертированный код уменьшаемого,

В единичное состояние триггер 3 переводят единицы кода вычитаемого, которые стираются с помощью элемента И 4 ,

В нулевое состояние триггер 3 устанавливают либо единицы кода уменьшаемого, считываемые с выхода регистра 2, либо в конце цикла ьычислений импульсы, поступающие по шине 13 сброса.

Один цикл вычислений занимает время перезаписи всех .. п-разрядов двоичного кода уменьшаемого с выхода регистра 2 на его вход и двоичного кода вычитаемого с выхода регистра 1 на его вход.

Максимальное время вычислений в предложенном устро йстве для вычитания занимает два цикла, во втором цикле обрабатываются всё единицы кода вычитаемого не стертые в первом ци кле.

Вычисления заканчиваются после с обнуления содержимого регистра 1 автоматически.

Если уменьшаемое меньше вычитаемого/разность фиксируется в дополнительном коде.

Q П р и м-е р 1, Требуется вычислить разность 845-446 399.

Двоичный код вычитаемого Хо 0.00110111110 (точкой отделен знаковый разряд) записывается в .регистр 1, а двоичный код уменьшаемо5го YO 0.01101001101 - в регистр 2, Двоичный код уменьшаемого остается без изменения до первой младшей единицы вычитаемого, начиная с которой инвертируется до первой едини0 цы уменьшаемого, затем опять код уменьшаемого остается без изменения до следующей ед11ницы вычитаемого, начиная с которой код уменьшаемого инвертируется и т.д. Единицы кода вы5 читаемого, начиная с которых код

уменьшаемого инвертируется, стираются ,

Таким образом, после первого цикла вычислений имеем

30Х, 0,0013,0111110

Y о.оаТПГо Ш

Y, 0.01010110011 X, 0,00100100100 в коде BbT4HTaeNioro подчеркнуты 35 единицы, начиная с которых происходит ин вертирование кода уменьшаемого а в коде уменьшаемого подчеркнуты разряды подлежащие инвертированию. Подчеркнутые е.диницы в коде вычитаеМО го стираются.

40

Во втором цикле вычислений получим окончательный результат

К,, 0.00100100,00 У; 0. ОПДЮДрд.Ц УЛ 0.00110001111 Х 0.00000000000

Пример 2. Требуется вычислить разность 446-845 -399.

Результат получаем в дополнительном коде после первого цикла вычислений

Хо 0.01101001101

1а- 212Ш21Ш2 У, 0.11001110001 X, 0,00000000000

в данном случае триггер 3 сбрасывается в нулевое состояние в конце цикла временным сигналом, поступающим по шине 5.3 сброса через элемент ИЛИ 9 и элемент 12 задержки на нулевой вход триггера 3.

Пример 3 Требуется вычислить разносгь (-845)-{446) 1291. В этом случае уменьшаемое записыва-ется в регистр 2 в дополнительном коде.

После первого цикла вычислений имеем

O.OOllOillllO l .TUtPloTrffUTl

1 .01100001101 0,00000011000

После второго цикла вычислений получим результат в дополнительном коде

Х| 0.00000011000 .01ТШГСГОТ101

Уг 1,01011110101

Xj О.ООООООООООО

Пример 4. Требуется вычислить разность 845 - (-446) 12 В этом случае вычитаемое записывается в регистр 1 Б дополнительном коде.

После первого цикла вычислений имеем

Хо 1.11001000010

YO oTSliolooiTcioi

1,10100001011 1,00000000000

X,

После второго цикла вычислений получаем окончательный результат

Х| 1.00000000000 YI О0001011 Yg ОЛ0100001011 Xg 0.00000000000

Как видно из примеров, знаковый разряд уменьшаемого и вычитаемого обрабатывается наравне с другими разрядами кодов.

Быстродействие предложенного устройства для вычитания значительно выше, чем в известном, в котором количество циклов вычислений равно количеству единиц п кода вычитаемог

В предложенном устройстве для вычитания максимальное количество циклов вычислений равно двум, Следовате.льно, достигнут эффект увеличения быстродействия в п,/2 раза Например, эффект увеличения быстродействия в 10 раз достигается при п

20, т.е. при двадцатиразрядных кодах вычитаемого.

Кроме того, схемная реализация предложенного устройства для вычитания проще, так как требует на один триггер меньше, чем известное.

Формула изобретения Устройство для вычитания, содержащее два регистра, триггер, элементы И, ИЛИ и НЕ,причем вход первого регистра подключен к выходу первого элемента И, первый вход которого соединен с первым входом второго элемента И и выходом первого регистр вторые входы первого и второго элементов И подключены к единичному и нулевому выходам триггера соответственно, выход второго элемента И через первый элемент задержки подключен к единичному входу триггера, входы первого элемента ИЛИ подключены к выходам третьего и четвертого элементов И, а выход - ко входу второго регистра, выход которого под ключей к первым входам третьего элемента И и второго элемента ИЛИ и входу элемента НЕ, выход которого подключен к- первому входу четвертого элемента И, второй

вход второго элемента ИЛИ подключен к шине сброса, а выход - ко входу второго элемента задержки, отличающееся тем, что, с целью упрощения устройства и повышения его быстродействия, выход второго элемента задержки подключен к нулевому входу триггера, нулевой и единичный выходы которого подключены ко вторь / входам третьего и четвертого элементов И соответственно.

Источники информации, принятые во внимание при экспертизе

1.Справочник по цифровой вычистштельной технике. Под ред, Б.И. М.алиновского Киев, Техника, 1974 с„ 188 , рис. 5,266,

2.Авторское свидетельство СССР 435523, кло G 06 Р 7/385, 1972.

3.Авторское свидетельство СССР ,по заявке № 2500770/18-24,

кл. G Об F 7/385, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1978 |

|

SU746513A1 |

| Устройство для вычитания | 1977 |

|

SU693370A1 |

| Устройство для вычитания | 1979 |

|

SU851403A1 |

| Устройство для вычитания | 1978 |

|

SU811249A1 |

| Устройство для вычитания | 1979 |

|

SU789992A1 |

| УСТРОЙСТВО ВЫЧИТАНИЯ | 1972 |

|

SU435523A1 |

| Генератор циклов | 1981 |

|

SU964616A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Счетчик для вычитания | 1984 |

|

SU1228276A1 |

| Устройство для вычисления квадратногоКОРНя | 1979 |

|

SU809172A1 |

Авторы

Даты

1980-05-25—Публикация

1978-03-01—Подача