п IS а

4;ib

СО

со go 00 со

Шиг.1

10

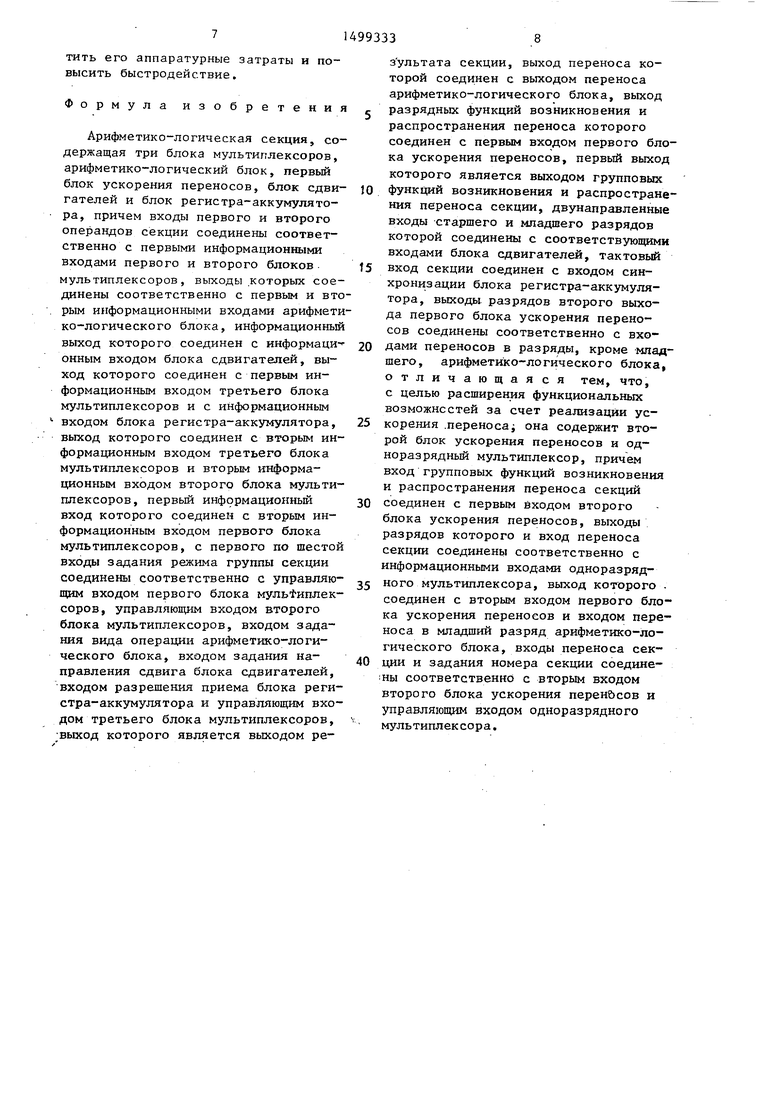

Изобретение относится к вычислительной технике, ориентировано на реализацию в виде БИС-секции, в частном случае - в виде матричной БИС (т.е . имеет специальные функциональные возможности для эффективного наращивания разрядности), и может быть использовано в быстродействующих многоразрядных арифметико-логических устройствах цифровых ЭВМ.

Целью изобретения является расширение функциональных возможностей за счет реализации ускорения переноса.

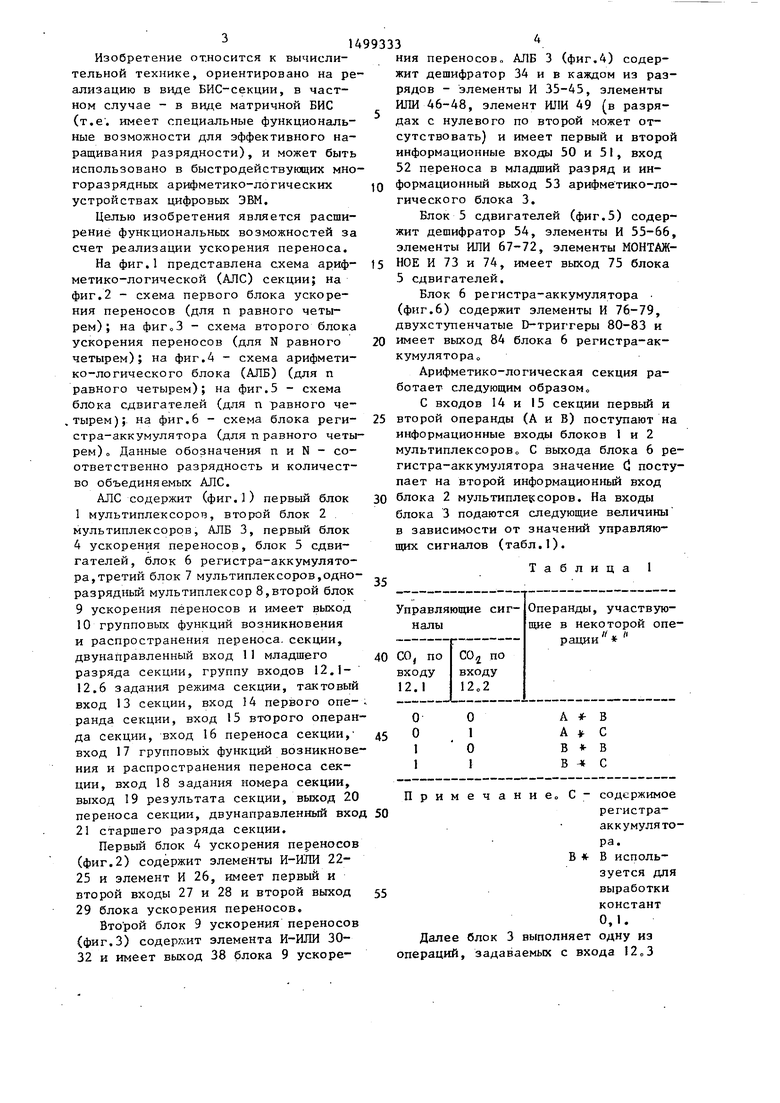

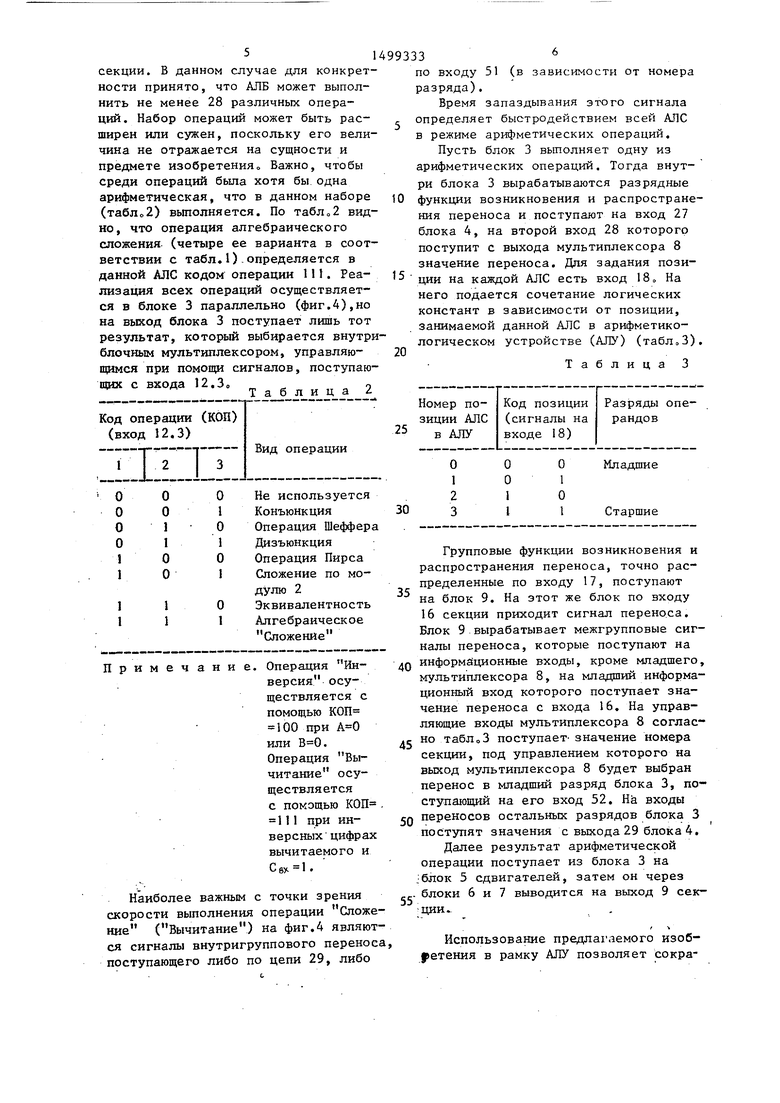

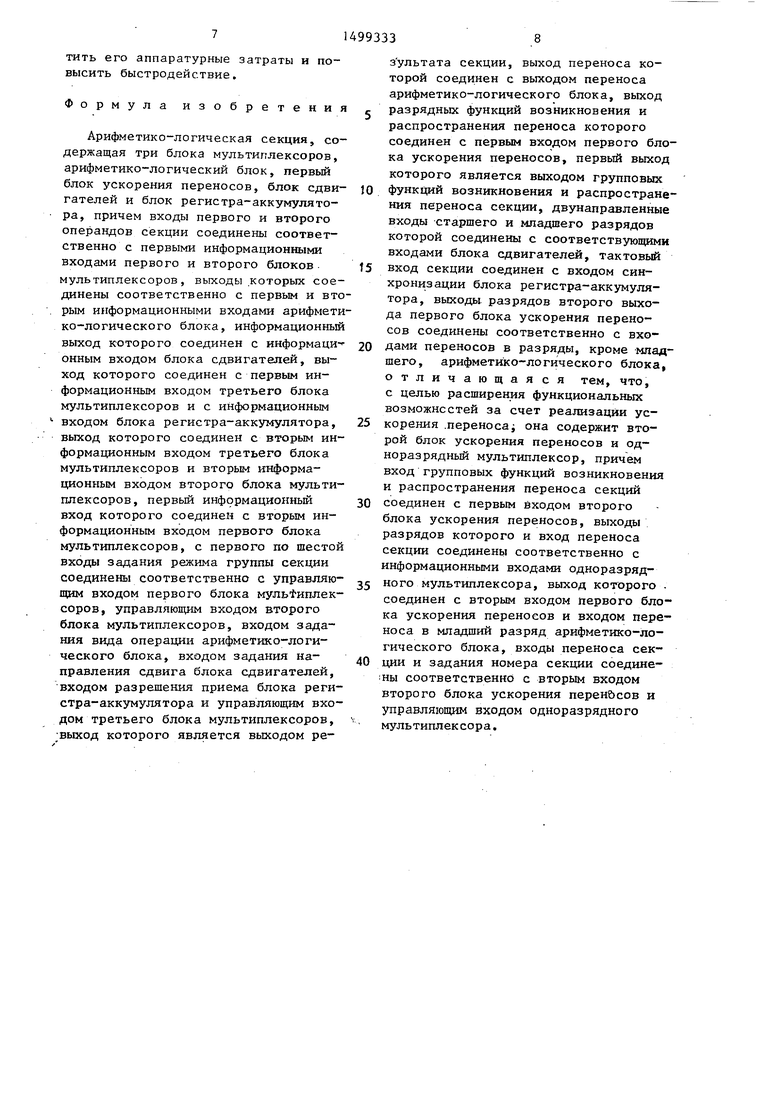

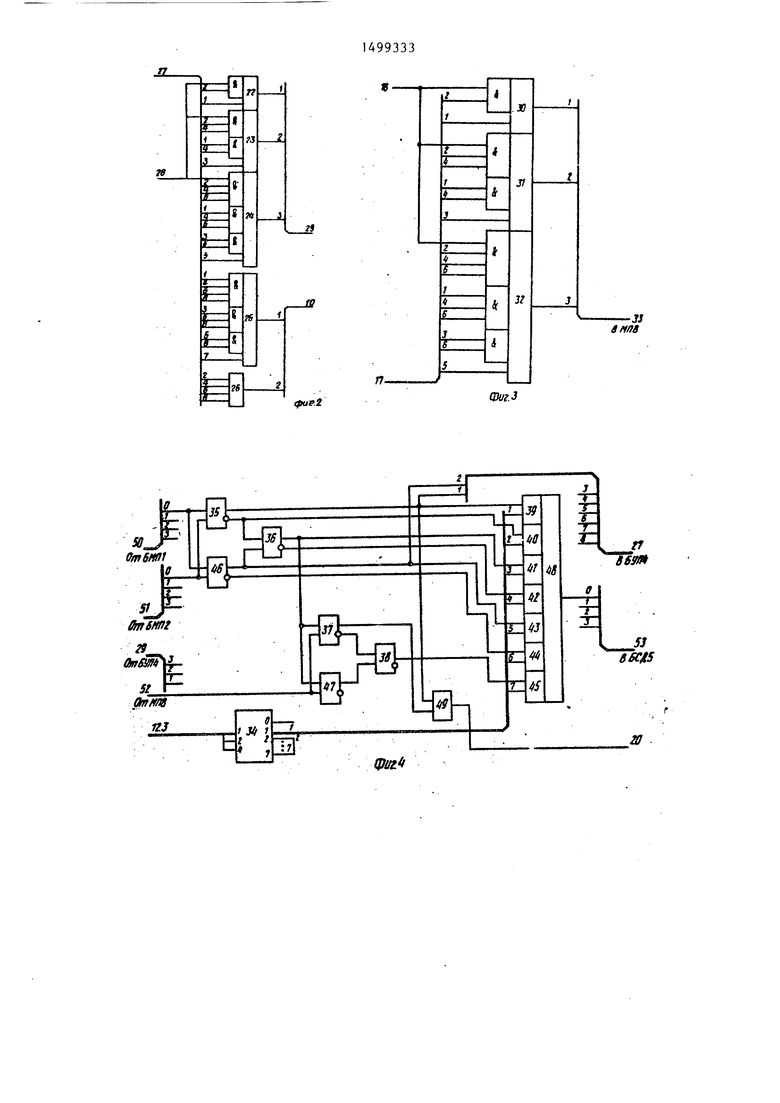

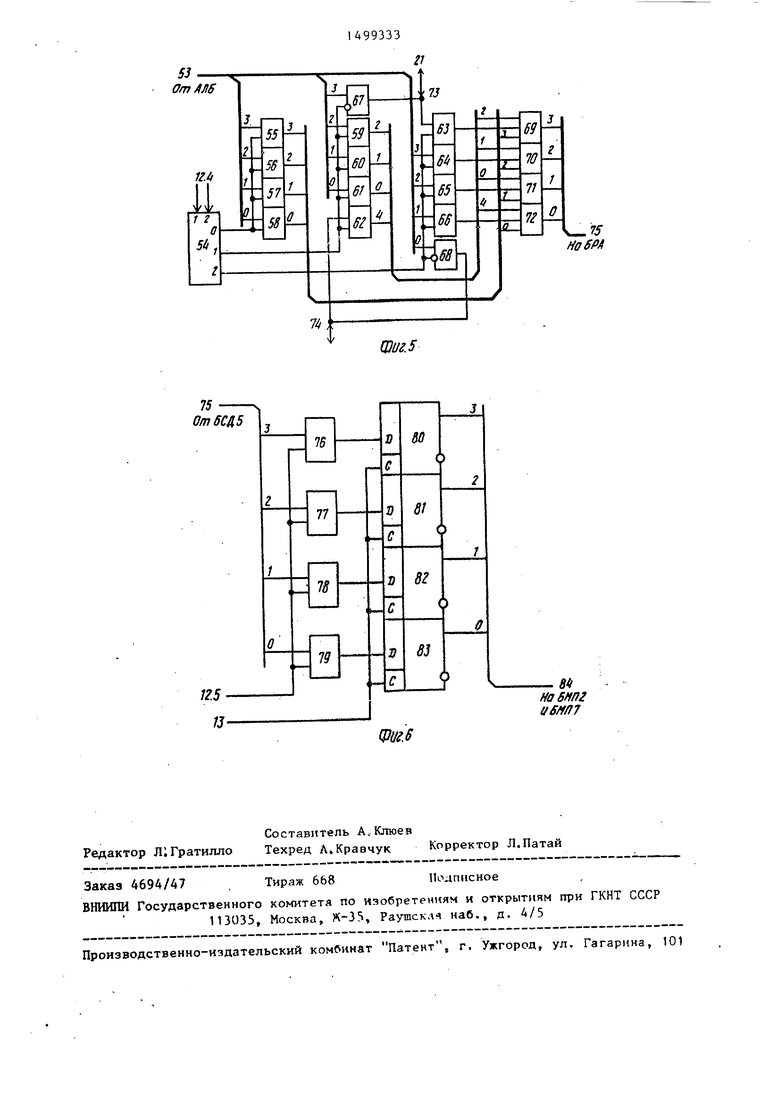

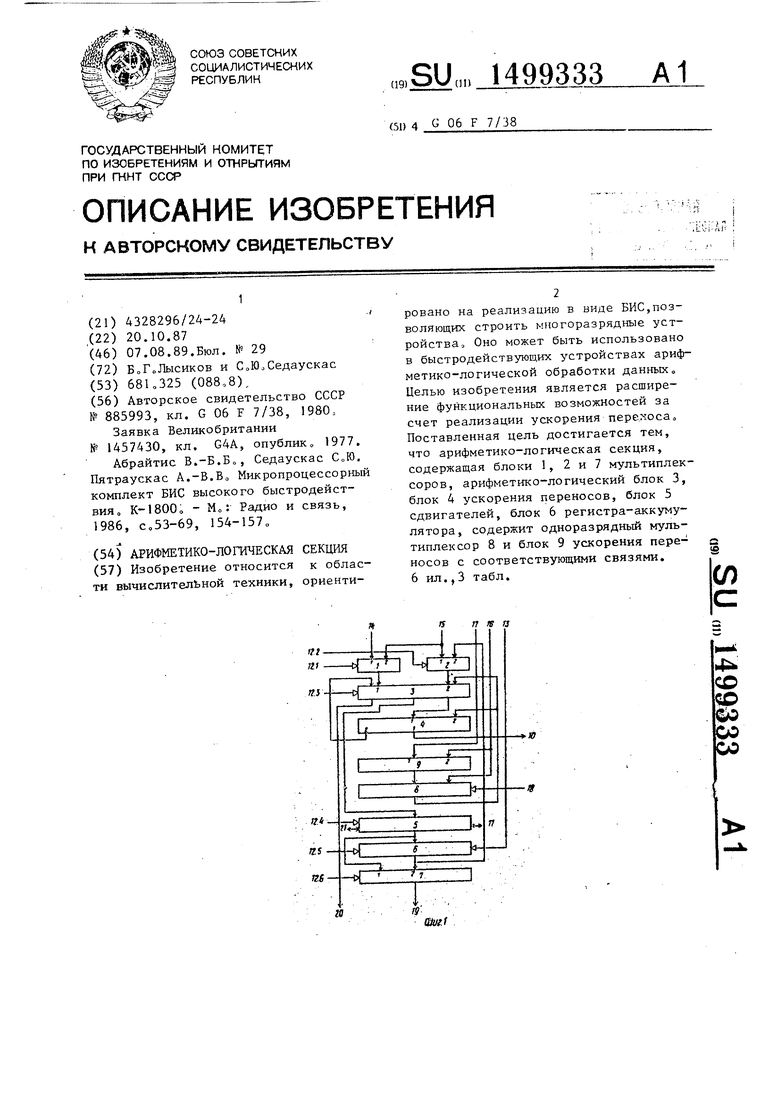

На фиг.1 представлена схема арифметико-логической (АЛС) секции; иа фиг.2 - схема первого блока ускорения переносов (для п равного четырем); на фиГоЗ - схема второго блока ускорения переносов (для N равного четырем); на фиг.4 - схема арифметико-логического блока (АЛБ) (для п равного четырем); на фиг.5 - схема блока сдвигателей (для п равного че- тырем); на фиг.6 - схема блока регистра-аккумулятора (для п равного четырем) Данные обозначения п и N - соответственно разрядность и количество объединяемых АЛС.

АЛС содержит (фиг.) первый блок 1 мультиплексоров, вторюй блок 2 мультиплексоров, АЛБ 3, первый блок 4 ускорения переносов, блок 5 сдвигателей, блок 6 регистра-аккумулятора, третий блок 7 мультиплексоров,одно- , разрядньш мультиплексор 8,второй блок

9ускорения переносов и имеет выход

10групповых функций возникновения и распространения переноса, секции, двунаправленный вход 11 младшего разряда секции, группу входов 12.1- 12.6 задания режима секции, тактовый вход 13 секции, вход 14 первого one- ранда секции, вход 15 второго операнда секции, вход 16 переноса секции,- вход 17 групповых функций возникновения и распространения переноса секции, вход 18 задания номера секции, выход 19 результата секции, выход 20 переноса секции, двунаправленный вход 50 21 старшего разряда секции.

Первый блок 4 ускорения переносов (фиг.2) содержит элементы И-ШШ 22- 25 и элемент И 26, имеет первый и второй входы 27 и 28 и второй выход 29 блока ускорения переносов.

Вто рой блок 9 ускорения переносов (фиг.З) содеряит элемента И-ИЛИ 30- 32 и имеет выход 38 блока 9 ускореts

20

25

30

55

ния переносов„ АЛБ 3 (фиг.4) содержит дешифратор 34 и в каждом из разрядов - элементы И 35-45, элементы ИЛИ 46-48, элемент ИЛИ 49 (в разрядах с нулевого по второй может отсутствовать) и имеет первый и второй информационные входы 50 и 51, вход 52 переноса в младший разряд и информационный вьпсод 53 арифметико-логического блока 3.

Блок 5 сдвигателей (фиг.5) содер жит дешифратор 54, элементы И 55-66, элементы ИЛИ 67-72, элементы МОНТАЖНОЕ И 73 и 74, имеет выход 75 блока 5 сдвигателей.

Блок 6 регистра-аккумулятора (фиг.6) содержит элементы И 76-79, двухступенчатые D-триггеры 80-83 и

имеет выход 84 блока 6 регистра-аккумулятора о

Арифметико-логическая секция работает следующим образом

С входов 14 и 15 секции первый и

второй операнды (А и В) поступают на информационные входы блоков 1 и 2 мультиплексоров С выхода блока 6 регистра-аккумулятора значение О поступает на второй информационный вход

блока 2 мультипле1бссоров. На входы блока 3 подаются следующие величины в зависимости от значений управляющих сигналов (табл.1).

Таблица 1

Примечанибо С- содержимое

регистра- аккумулятора.

В В используется для выработки констант 0,1.

Далее блок 3 выполняет одну из операций, задаваемых с входа 12„3

секции. В данном случае для конкретности принято, что АЛБ может выполнить не менее 28 различных операций. Набор операций может быть расширен или сужен, поскольку его величина не отражается на сущности и предмете изобретения Важно, чтобы среди операций бьта хотя бы одна арифметическая, что в данном наборе (табло2) выполняется. По табл,2 видно, что операция алгебраического сложения (четыре ее варианта в соответствии с табл,1)-Определяется в данной АЛС кодом операции 111. Pea- лизация всех операций осуществляется в блоке 3 параллельно (фиг.4),но на выход блока 3 поступает лишь тот результат, который выбирается внутри блочным мультиплексором, управляю- щимся при помощи сигналов, постзтаю- щих с входа 12.3

по входу 51 (в зависимости от номера разряда).

Время запаздывания этого сигнала определяет быстродействием всей АЛС в режиме арифметических операций.

Пусть блок 3 выполняет одну из арифметических операций. Тогда внутри блока 3 вырабатываются разрядные функции возникновения и распространения переноса и поступают на вход 27 блока 4, На второй вход 28 которого поступит с выхода мультиплексора 8 значение переноса. Для задания позиции на каждой АЛС есть вход 18 На него подается сочетание логических констант в зависимости от позиции, занимаемой данной АЛС в арифметико- логическом устройстве (АЛУ) (табл.З).

Таблица 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Устройство генерации адресной последовательности для контроля оперативных накопителей | 1987 |

|

SU1513524A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Арифметическое устройство | 1989 |

|

SU1647557A1 |

| Устройство для суммирования двух чисел с плавающей запятой | 1988 |

|

SU1529214A1 |

| Устройство для сложения-вычитания чисел с плавающей запятой | 1986 |

|

SU1376080A1 |

| Арифметико-логическое устройство со встроенной диагностикой | 1984 |

|

SU1275426A1 |

Изобретение относится к области вычислительной техники, ориентировано на реализацию в виде БИС, позволяющих строить многоразрядные устройства. Оно может быть использовано в быстродействующих устройствах арифметико-логической обработки данных. Целью изобретения является расширение функциональных возможностей за счет реализации ускорения переноса. Поставленная цель достигается тем, что арифметико-логическая секция, содержащая блоки 1,2 и 7 мультиплексоров, арифметико-логический блок 3, блок 4 ускорения переносов, блок 5 сдвигателей, блок 6 регистра-аккумулятора, содержит одноразрядный мультиплексор 8 и блок 9 ускорения переносов с соответствующими связями. 6 ил., 3 табл.

скорости выполнения операции Сложение (Вычитание) на фиг.4 являются сигналы внутригруппового переноса, поступающего либо по цепи 29, либо

ции

Использование предлагаемого изоб- | етения в рамку АЛУ позволяет сократить его аппаратурные затраты и повысить быстродействие.

Формула изобретения

Арифметико-логическая секция, содержащая три блока мультиплексоров, арифметико-логический блок, первый блок ускорения переносов, блок сдви- гателей и блок регистра-аккумулятора, причем входы первого и второго операндов секции соединены соответственно с первыми информационными входами первого и второго блоков. мультиплексоров, выходы .которых соединены соответственно с первым и вторым информационными входами арифметико-логического блока, информационный выход которого соединен с информаци- онным входом блока сдвигателей, выход которого соединен с первым информационным входом третьего блока мультиплексоров и с информационным входом блока регистра-аккумулятора, выход которого соединен с вторым информационным входом третьего блока мультиплексоров и вторым информационным входом второго блока мультиплексоров, первый информационный вход которого соединен с вторым ин- формационньш входом первого блока мультиплексоров, с первого по шестой входы задания режима группы секции соединены соответственно с управляющим входом первого блока мультиплексоров, управляющим входом второго блока мультиплексоров, входом задания вида операции арифметико-логического блока, входом задания направления сдвига блока сдвигателей, ВХОДОМ разрешения приема блока регистра-аккумулятора и управляющим входом третьего блока мультиплексоров, выход которого является выходом ре-

з ультата секции, выход переноса которой соединен с выходом переноса арифметико-логического блока, выход разрядных функций возникновения и распространения переноса которого соединен с первым входом первого блока ускорения переносов, первый выход которого является выходом групповых

функций возникновения и распространения переноса секции, двунаправленные входы старшего и младшего разрядов которой соединены с соответствующими входами блока сдвигателей, тактовый

вход секции соединен с входом синхронизации блока регистра-аккумулятора, выходы разрядов второго выхода первого блока ускорения переносов соединены соответственно с входами переносов в разряды, кроме младшего, арифметико-логического блока, отличающаяся тем, что, с целью расширения функциональных возможностей за счет реализации ускорения .переноса она содержит второй блок ускорения переносов и одноразрядный мультиплексор, причем вход групповых функций возникновения и распространения переноса секций

соединен с первым входом второго блока ускорения переносов, выходы разрядов которого и вход переноса секции соединены соответственно с информационными входами одноразрядного мультиплексора, выход которого - соединен с вторым входом первого блока ускорения переносов и входом переноса в младший разряд арифметико-логического блока, входы переноса секции и задания номера секции соедине- ;ны соответственно с вторым входом второго блока ускорения переносов и управляющим входом одноразрядного мультиплексора.

ipae.2

SO. Отбнп

J

&ябтг

29

Onftns ИЗ

Ц1

(DiK.3

liS

111

68

SJ

SSCfS

H9

SJ

фаг

| Арифметическое устройство | 1980 |

|

SU885993A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Заявка Великобритании № 1457430, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Абрайтис В.-Б.Во, Седаускас СоЮ | |||

| Пятраускас А.-В.В Микропроцессорный комплект БИС высокого быстродействия, К-1800, - Радио и связь, 1986, с„53-69, 154-157„ | |||

Авторы

Даты

1989-08-07—Публикация

1987-10-20—Подача