1

Изобретение относится к цифровым дифференциальным анализаторам и пред назначено для использования в устрой« ствах вычислительной техники, в частности в системах автоматического регулирования.

Известны цифровые интеграторы, содержащие регистр остатка, сумматоры, регистры подынтегральный функции, умножители .

Недостатком известных устройств является значительная конструктивная сложность.

Наиболее близким по технической сущности X данному изобретению является цифровой интегратор, содержащий генератор тактовых импульсов, соединенный с первыми входами формирователя переполнений и генератора сдвиговых импульсов, выход которого соединён с первыми входами регистра подьщ тегрального выражения и накопитель ного регистра, выход регистра подынтегрального выражения соединен с первым входом первого сумматора, выход которого подключен ко второму входу накопительного регистра, первый выход накопительного регистра соединен со вторым входом первого сумматора, а второй выход - со вторым входом формирователя переполнений, выход которого соединен через элемент задержки с третьим входом накопительного регистра, второй вход генератора сдвиговых импульсов и третий вход первого сумматора являются управляющими входами устройст- ва 2.

Однако такой интегратор не позволяет производить интегрирование перемешю- го подынтегрального выражения.

Цель изобретения - расширение функциональных возможностей, за счет реализации интегрирования с переменным подынтегральным выражением при участии в процессе интегрирования независил{ой внешней составляющей.

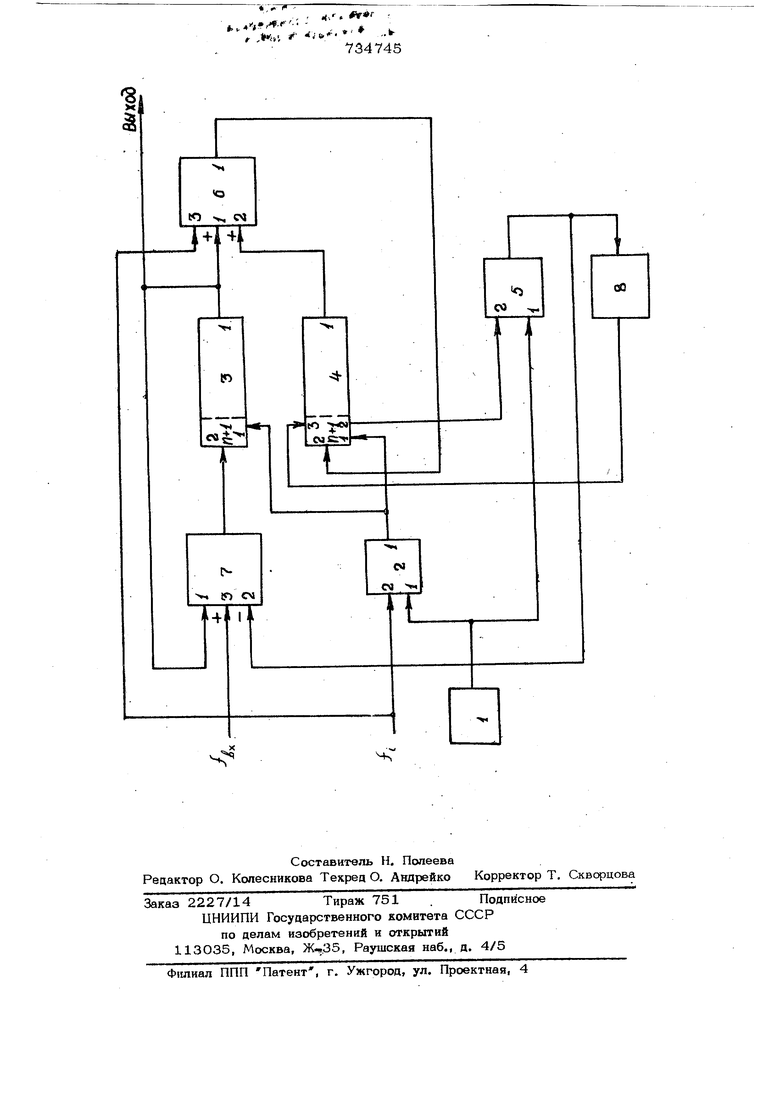

Поставленная цель достигается тем, что в интегратор введен второй сумматор, первый вход которого соединен с выходом регистра подынтегрального выражения, а второй вход - с выходом фор мирователя переполнений, третий вход второго сумматора соединен со входом устройства, выход второго сумматора .соединен с вторым входом регистра подь тегрального выражения. На чертеже представлена блок-схема цифрового интегратора. Схема цифрового интегратора содержит генератор 1 тактовых импульсов, генератор 2 сдвиговых импульсов, регистр 3 подынтегрального выражения, накопительный регистр 4, формирователь 5 переполнений сумматоры 6 и 7, элемент задержки 8. Выход регистра 3 подынтегрального выражения является выходом устройства Устройство работает следующим обра зом. В,исходном состоянии регистр 3 подьш тегрального выражения и накопительный регистр 4, разрядность которых (1+ 1), обнулены. Генератор 1 тактовых импульсов задает частоту сдвига информации регистра 3 подынтегрального выражения и накопительного регистра 4. Генератор 2 сдвиговых импульсов вырабатывает серии импульсов, причем коли чество импульсов в серии равно числу разрядов регистра 3 подынтегрального выражения и накопительного регистра 4 т. е. (1п+ 1). С приходом каждого импульса частоты интеграции происхо- дит вычислительный цикл, в течении которого производится полный сдвиг инфор мации в регистрах 3 и 4. Входные импульсы с частотой следования п, поступающие синхронно с частотой итераци ; , причем f; f ц , и с весом, равным, например, единице, поступают со aiiBKOM плюс на третий вход сумматора 7, на первый вход которого поступает содержимое регистра 3 подынтеграль- кого выражения. Сумма вновь вводится в регистр 3 подынтегрального выражения , Т.е. с приходом каждого импульса с частотой следования f ik содержимое регистра 3 подынтегрального вы ражения увеличивается на единицу. С по помщью сумматора 6 содержимое регис ра 3 подынтегрального выражения скла дывается с содержимым на копительного регистра 4 во время каждой итерации,, а сумма с выхода сумматора 6 вновь вводится в накопительный регистр;, 4, . Так как содержимое регистра 3 подыиегрального выражения определяется И. начащими разрядами и ((Я + 1)-й разряд егистра 4 обнулен, то наличие единицы (rtfl+l)-M разряде накопительного регистра 4, в который вводится сумма с ыхода сумматора 6, используется для ормирования переполнения. С выхода ормирователя 5 переполнений, синхроизированного импульсами генератора 1 тактовых импульсов, импульс переполнения, пройдя через элемент 8 задержки обну- ляет (11+1)-й разряд накопительного регистра 4. Непосредственно с выхода формирователя 5 переполнений импульсы с час., тотой переполнений ; , имеющие вес, равный единице, и со знаком минус поступают на второй вход сумматора 7. . Частота переполнений f)-, определяет ся формулой n-f, д где Ч - содержимое регистра 3 подынтегрального выражения; R - емкость значащей части накопи- тельного регистра 4, равная . Так как входные импульсы с частотой следования ц непрерывно увеличивают содержимое в регистре 3 подынтегрального выражения, являющееся одним из слагаемых суммы, поступающей в накопительный регистр 4, то частота парепачнений с выхода формирователя 5 переполнений также будет увеличива, ся. Ввиду того, что импульсы с частО той следования : у поступают на BTO«I рой вход сумматора 7 с отрицательным знаком и уменьшают содержимое регистра 3 подынтегрального выражения, то увеличение содержимого регистра 3 подынтегрального выражения будет происходить до тех пор, пока частоты f g и J j не сравняются, т. е. следовательно -I -В И . B4f. Обозначим время, по истечении которого Частоты f j и f gy станут равными, тогда Таким образом, код. содержащийся в регистре подынтегрального выражения, будет отображать величину входной частоты Ъ1 S время преобразования частоты в код равно Т . Точность преобразования частоты в код зависит от величины Г . Чем меньше величина С , тем меньше будет точ ность преобразования. Величину Т мож но регулировать путем изменения емкости значащей части накопительного регист ра 4, равной 1 , или величины частоты итераций. -;.. Если за выход устройства принять выход формирователя 5 переполнений, то предлагаемый цифровой дифференциальный интегратор может быть исполь- зован для формирования разгона и замед ления в устройствах автоматического управления станками контурного или позиционного типа. Цифровой интегратор позволяет произ водить интегрирование кода во времени и преобразовывать частоту в код. Регулирование постоянной времени интегрирования интегратора позволяет использовать его для управления станками, имеющими различные динамические харак теристики. За счет экономии дорогостоящих- микросхем сокращения монтажных и техноло1ических работ, ожидаемый эконо мический эффект ог использования предл гаемого устройства составляет, около 20О руб. на одно устройство. Ф о рмула изобретения Цифровой интегратор, содержащий генератор тактовых импульсов, соединенный с первыми входами формирователя переполнений и генератора сдвиговых , импульсов, выход которого соединен с первыми входами регистра подынтегрального выражения и накопительного регистра, выход регистра подынтегрального вы- ражения соединен с первым входом пе вого сумматора, выход которого подключенко второму входу накопительного регистра, первый выход накопительного регистра соединен со вторым входом первого сумматора, а второй выход - со вторым входом формирователя переполнений, выход которого соединен через элемент задержки с третьим входом накопительного регистра, второй вход генератора сдвиговых импульсов и третий вход первого сумматора являются управляющими входами устройства, о т л и ч а ю щи и с я тем, что, с целью расширения функциональных возможностей за счеу реализации интегрирования с переменным подынтегральным выражением при участии в процессе интегрирования независимой внешней составляющей, в него введен вто рой сумматор, первый вход которого динен с выходом регистра подынтегрального выражения, а второй вход - с выхо- дом формирователя переполнений, третий вход второго сумматора соединен со входом устройства, выход второго сумматора соединен с вторым входом регистра подынтегрального выражения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N9 519735 кл. G 06 J ,1/00, 1974. 2.Патент США № 3701890 л. 235-150.31, 1973.

,r. ,,

. -

r .IW-, -f «,

734745

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1976 |

|

SU720427A1 |

| Цифровой интегратор | 1978 |

|

SU698017A1 |

| Линейно-круговой интерполятор | 1977 |

|

SU741234A1 |

| Цифровой интегратор | 1982 |

|

SU1042015A1 |

| Интерполятор для систем программного управления | 1977 |

|

SU658528A1 |

| Модуль интегрирующей вычислительной структуры | 1982 |

|

SU1101821A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Стохастический интегратор | 1980 |

|

SU942017A1 |

| Цифровой интегратор | 1983 |

|

SU1191925A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

Авторы

Даты

1980-05-15—Публикация

1977-01-10—Подача