i

Изобретение относится к области вычислительной техники и предназначено . для подсчета одноименных цифр в двоичных кодах, а также для вычисления модуля разности (т-1), где m-количество единиц в этих кодах.

По основному авт.свид. № 450160 известно устройство для параллельного счета количества единиц (нулей) в двоичном числе.

Устройство содержит п, -разрядный входной регистр,о§ пгрупп суммат;оров по h /2К сумматоров в каждой группе ( 1 К. од„г ). Выход суммы последнего сумматора каждой группы и вьяод переноса сумматора последней К группы соединены со входами соответствуюши.х, разрядов вьгходного регистра. Входы каждого -го сумматора К группы соединены с вькодами переноса 2 -го и (2 i - 1) сумматоров (К-1) группы и с выходом суммы ( i -1) cyMNWTOpa К группы. Выходы 2 1 -го (2 i -1)-го разрядов входного регистра соединены

СО входами -го су олатора первой группы.

Недостатком известного устройства является невозможность проверки на четность полученного результата.

Целью изобретения является расширение функциональных возможностей за счет реализации проверки на четность числа,.

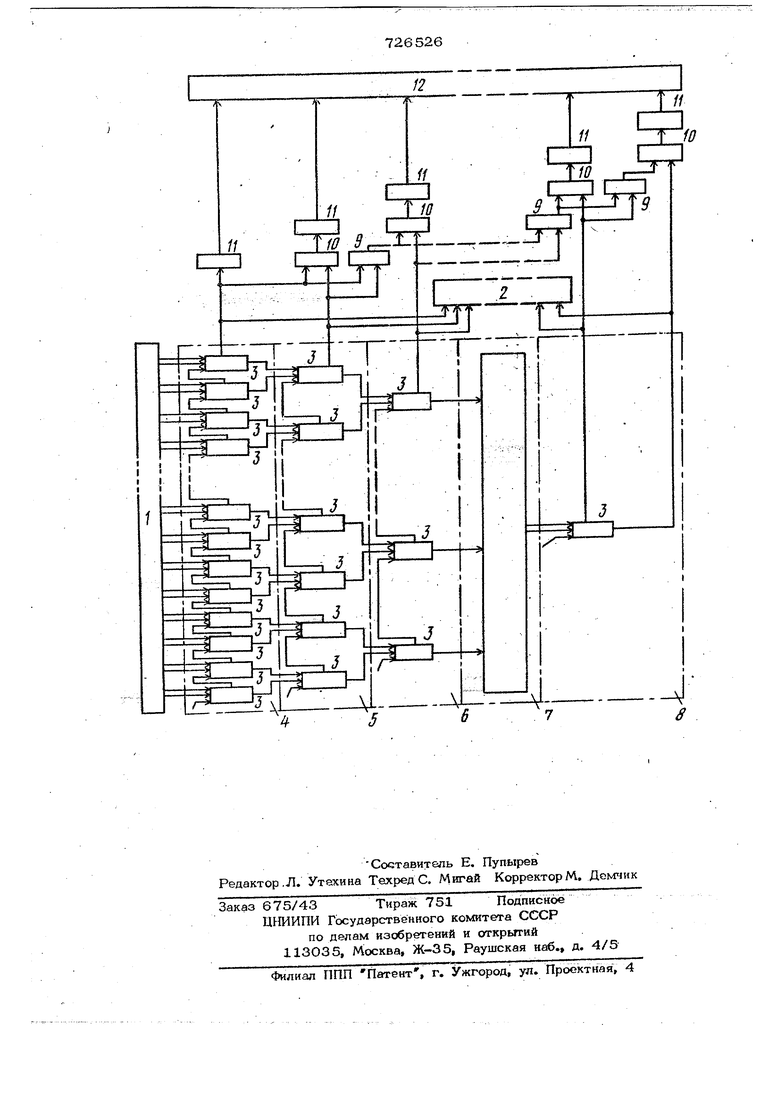

Зта цепь достигается тем, что предло0женное устройство содержит дополнител1 ный регистр, элементов НЕ, где f(,a n - число разрядов числа, и - 1 полусумматоров, ( -2 элементов Или. Вход i -го элемента НЕ (i 2.,.,е )

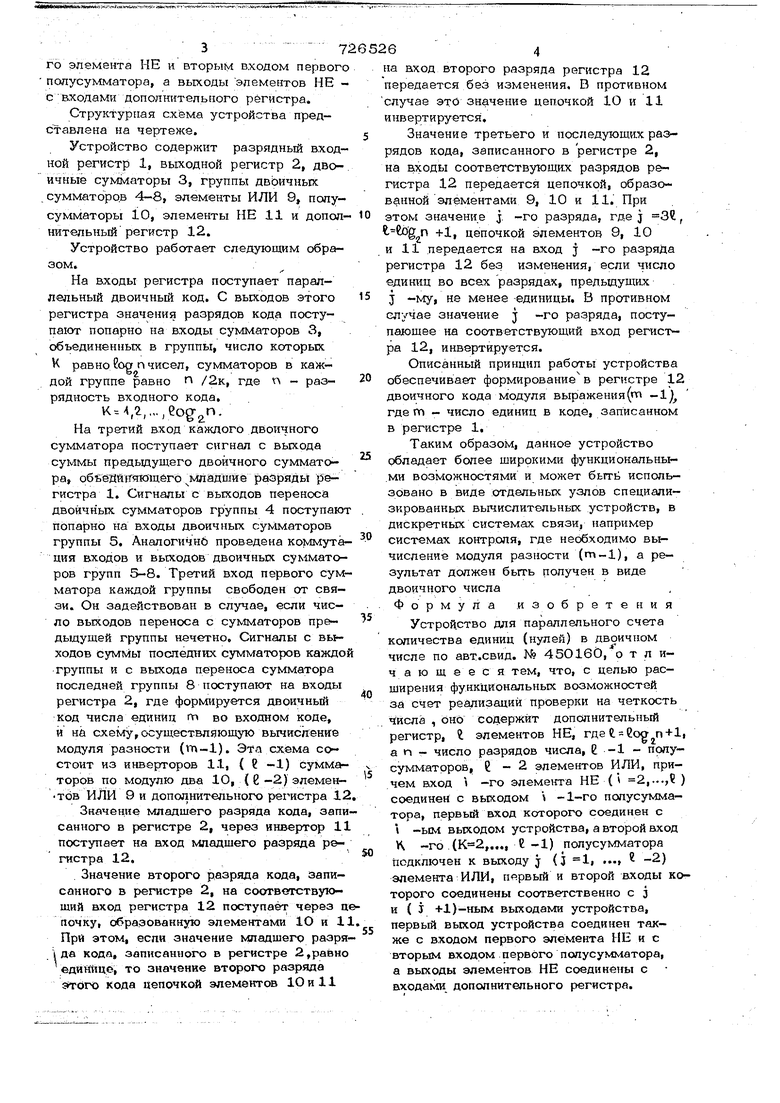

5 соединен с вькодом i -1-го полусумматора, первьгй вход которого соединен с i -ым выходом устройства. ЕЗторой вход К-го (К 2j,.., -1) полусумматора подключен к рыходу j -го (j 1,..., -2) элемента ИЛИ, первый и второй вхоДы ко торого соединены соответственно с j -м (j +1-ь1м) выходами, устройства. Первый выход устройства соедиЕ1ен с в ходом перво- 3 7 го элемента НЕ и вторым входом первог полусумматора, а выходы элементов НЕ с входами дополнительного регистра. Структурная схема устройства представлена на чертеже. Устройство содержит разрядный входной регистр 1, выходной регистр 2, двоичные сумматоры 3, группы двоичных .сумматоров 4-8, элементы ИЛИ 9, полусумматоры 10, элементы НЕ 11 и допол нительныйрегистр 12. Устройство работает следующим образом. На входы регистра поступает параллельный двоичный код. С выходов этого регистра значения разрядов кода поступают попарно на входы сумматоров 3, объединенных в группы, число которых К равно fog п чисел, сумматоров в кажраздой группе равно п /2к, где п рядность входного кода, ,2,,,,,. На третий вход каждого двоичного сумматора поступает сигнал с выхода суммы предьщущего двоичного сумматора, обlieHft(Гякзщёго 1 шадшйе разряды регистра 1, Сигналы с выходов переноса двоичных сумматоров группы 4 поступаю попарно на входы двоичньк сумматоров группы 5. Аналогично проведена коммута ция входов и выходов двоичных сумМаторов групп 5-8. Третий вход первого сум матора кажд.ой группы свободен от связи. Он задействован в случае, если число выходов переноса с сумматоров предьщущей группы нечетно. Сигналы с выходов суммы последттих сумматоров каждо группы и с выхода переноса сумматора последней группы 8 поступают на входы регистра 2, где формируется двоичный код числа единиц гг во входном коде, и ни схему, осуществляющую вычисление модуля разности (vn-l). Эта схема состоит из инверторов 11, ( -1) сумматоров по модулю два 1О, { g -2) элеме тов ИЛИ 9 и дополнительного регистра 1 Значение младшего разряда кода, зап санного в регистре 2, через инвертор 1 поступает на вход младщего разряда Р&гистра 12, Значение второго разряда кода, записанного в рюгистре 2, на соответствующий вход регистра 12 поступает через ц почку, образованную элементами 1О и 1 При этом, если значение младшего разря i да кода, записанного в регистре 2,равно единйцо, то значение второгчэ разряда кода цепочкой элементов 1Ои11 64 а вход второго разряда рнгистра 12 передается без изменения. В противном случае это значение цепочкой 10 и 11 инвертируется. Значение третьего и последующих разрядов кода, записанного в регистре 2, на Еходы соответствующи.х разрядов регистра 12 передается цепочкой, образованной элементами 9, 10 и 11. При этом значение | -го разряда, где j 31, +1, цепочкой элементов 9, 10 и 11 передается на вход j го разряйа регистра 12 без изменения, если число единиц во всех разрядах, предьщущах j -му, не менее единицы, В противном случае значение j -го разряда, поступающее на соответствующий вход регистра 12, инвертируется. Описанный принцип работы устройства обеспечивает формирование в регистре 12 двоичного кода модуля выражения (т -1) гдеm - число единиц в коде, записанном в регистре 1, Таким образом, данное устройство обладает более широкими функциональны.ми возможностями и может быть использовано в виде :отдельньгх: узлов специализированных вычислительньгх устройств, в дискретных системах связи, например системах контроля, где необходимо вычисление модуля разности (m-l), а результат должен быть получен в виде двоичного числа Формула изобретения Устройство для параллельного счета количества единиц (нулей) в двоичном числе по авт.свид. № 45О160, о т л ичающееся тем, что, с целью расширения функциональных возможностей за счет реализаций проверки на четкость числа , оно содержит дополнительный регистр, i элементов НЕ, гдеС. Со,п+1, an- число разрядов числа, 2 -1 - полусумматоров, С - 2 элементов ИЛИ, причем вход -го элеме1гга НЕ ( 2,..., ) соединен с выходом -1-го полусумматора, первый вход которого соединен с -ым выходом устройства, а второй вход К -го (,,,,, С-1) полусумматора подключен к выходу j (j 1, .,., -2) элемента ИЛИ, первый и второй входы которого соединены соответственно с з и ( J +1)-ным выходами устройства, первый выход устройства соединен также с входом первого элемента НЕ и с вторым входом .первого полусумматора, а выходы элементов НЕ соединены с входами дополнительного регистра.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1134934A1 |

| ПОРОГОВЫЙ ЭЛЕМЕНТ | 1987 |

|

RU2034401C1 |

| Пороговый элемент | 1987 |

|

SU1584098A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Преобразователь кода грея в двоичныйКОд | 1973 |

|

SU842783A1 |

| Устройство для возведения в квадрат @ -разрядных двоичных чисел | 1990 |

|

SU1784977A1 |

| Устройство для умножения | 1983 |

|

SU1130859A1 |

| Устройство для умножения | 1986 |

|

SU1339551A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Матричный вычислитель экспоненты | 1981 |

|

SU1024911A1 |

Авторы

Даты

1980-04-05—Публикация

1978-01-12—Подача