зователя, второй вход синхронизации преобразователя соединен с входом регистра сдвига и с управляющим входом второго регистра, выход младшего разряда регистра сдвига соединен со вторыми входами элементов И первой группы, выход п-ого элемента И первой группы (где п -число разря юв преобразуемого кода соединен сё входом .(n-l)-oro разряда первого регистра и с первым входом младшего разряда сумматсфа, выход (n-l)-oro элемента ИЛИ группы соединен со входом (п-2)-ого разряда первого регистра и с первым входом (n-l)-oro разряда сумматора, выход i-oro (n-2) элемента ИЛИ группы соединен с первым входом i-ого разряда сум.матора и вторым входом (i+2)-oro разряда сумматора.

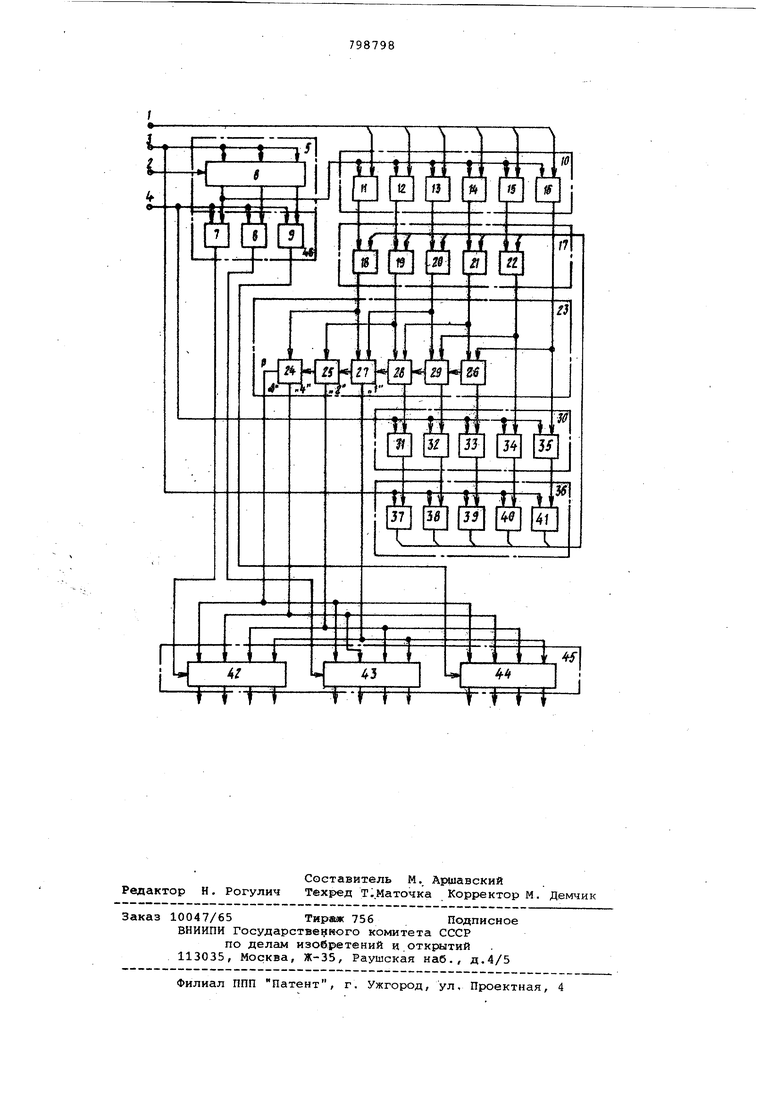

На чертеже приведена блок-схема предлагаемого преобразователя для случая.преобразования шестиразрядных дробных двоичных чисел в трехразрядные, десятичные .

Преобразователь содержит информационный вход 1 для подачи параллельного двоичного кода дробного числа, вход 2 для подачи импульса признака кода, входы 3 и.4 синхронизации преобразователя путем подачи сдвинутых друг относительно друга синхроимпульсов, блок 5 .управления, состоящий из регистра б сдвига и элементов И 7,8 и 9, первую группу 10 элементов И 11-16, группу 17 элементов ИЛИ 18-22, сумматор 23, состоящий и полусумматоров 24-26 и сумматоров 27-29, первый регистр 30, триггеров 31-35, второй регистр 36, триггеров 37-41 и тетрады 42-44 выходного регистра 45, Элементы И 7-9 образуют вторую группу 46 элементов И.

Преобразователь работает следующим образом.,

Двоичный код преобразуемого дрюбного числа поступает с информационного входа 1 на входы группы элементов И 10, причем первый после запятой двоичный разряд поступает на вход элемента И 11. О поступлении на преобразование очередного кода свидетельствует импульсный признак кода, поступающий с входа 2 на вход первого разряда регистра сдвига 6. Продвижение информации по регистру 6 осуществляется синхросигналами, поступающими с входа З.При поступлении очередного синхроимпульса признак кода записывается в регистр и появляется на выходе первого разряда регистра, с выхода которого он поступает на вход элемента И 7 и управляющие входы элементов И групп 10, разрешая прохождение двоичного кода через группу элементов И 10 и ИЛИ 17 на вход сумматора 23, обеспечивающего сложение этого кода с.

тем жё кодом, сдвинутым на два разряда в сторону старших разрядов.. Таким образом, осуществляется умножение входного кода на число 10 (1010). По окончании процесса распрстранения переносов в сумматоре, на ЕГО выходах появляется код первой частной суммы, четыре старших разряда которой с выходов полусумматоров и сумматора 24, 25 и 27 определяют код стадией тетрады десятичного числа. Этот код поступает одновременно на входы всехтетрад 42-44, н записывается только в тетраду 42, нуправлякяций вход которой поступает при появлении на входе 4 - синхронизирующего сигнала сигнал приема первой тетрады числа. Одновременно с этим дробная часть кода суммы с выходов полусумматора и сумматоров 26, 28 и 29 ИЛИ 22 и И 16 записывается в первый регистр 30.

При поступлении очередного синхроимпульса на вход 3 код дробной части суммы из первого регистра 30 переписывается во второй регистр 36, с выходов которого через группу элементов ИЛИ 17 поступает на входы двоичного сумматора 23 и умножается на число 10 (1010). Этим же синхросигналом в регистре сдвига 6 единица сдвигается в следующий- разряд, отчего группа элементов И 10 и элемент И 7 запираются, а при поступлении очередного синхросигнала на вход 4 на ыходе элемента И 8 появился сигнал приема второго числа, которое записывается в тетра ду 43 выходного регистра 45.

Этот процесс поочередного выделения разрядов десятичного числа продолжается до окончания преобразования. После п циклов преобразования преобразователь самоочищается. Чис/ловой.пример преобразования шестиразрядного двоичного кода, 10011:

1-й цикл

,110011 110011

- первая

частная сумма 7 дробная часть первой частной суммы

,11111 11111

,l011 - вторая

g частная сумма

, 1011 1011

110,111 - третья g частная сумма 4-й цикл 111 - четвертая ч тная су 1,11 Четвертый разряд 8 5-й цикл ill IQjIYi 1 пятая час -- ная сумма Пятый разряд 6-й цикл + Шестой разряд - шестая час ная дробная ча отсутствует т.е. преобразовательсамоочистил ся. Использование предлагаемого преобразователя позволяет упростить из вестный преобразователь за счет сок щения разрядности регистра на четыре разряда, исключить цепи передачи кода при сдвиге на четыре разряда и упростить расширение разрядности преобразователя (не требуется увеличивать число цепей сдвига) . Кро ме того, предлагаемый преобразователь, в отличие от известного, имеет возможность преобразования нескольких входных чисел,.для чего следует увеличить число выходных регистров и с соответствующими цепями коммутации. Остальная же часть преобра-зователя остается общей. Формула изобретения Преоб)азователь дробных двоичных чисел в десятичные, содержащий сумматор, первый регистр, разрядные входы которого соединены с первой группой выходов сумматора, тетрады выходного регистра, отличающийся тем, что, с целью упрощен преобразователя, он содержит frpynпы элементов И, группу элементов ИЛИ регистр сдвига, второй регистр, информационные входы которого соединены -с выходами первого регистра, а разрядные выходы второго регистра соединены с первыми входами элементов ИЛИ группы, вторые входы которых соединены с выходами элементов И группы, вторая группа f выходов сумматора соединена с информационными входами тетрад выходного регистра, управлякадие входы тетрад которого соединены с соответствующими выходами элементов И второй группы, первые входы которых соединены с разрядными выходами регистра сдвига, вторые входы элементов И второй группы соединены с первым входом синхронизации преобразователя и с управляющим входом первого регистра, первые входы элементов И первой группы соединены с информационным входом преобразователя, второй вход синхронизации преобразователя соединен с входом регистра сдвига и с управляющим входом второго регистра, выход младшего разряда регистра сдвига соедичен со . вторыми-входами элементов ИI первой группы, выход п-ого элемента И первой группы (где п -число разрядов преобразуемого кода) соединен со входом (п-1) -ого разряда первого регистра и с первым входом младшего разряда сумматора, выход (.п-1)-ого элемента ИЛИ группы соединен со входом (п-2) -ого разряда первого регистра и с первым входом (п-1)-ого разряда сумматора, выход i -ого ( +(п-2) ) элемента ИЛИ группы соединен с первым входом i-oro разряда сумматора и вторым входом (i +2) -ого разряда сумматора. Источники информации, принятые во внимание при экспертизе 1. Патент ФРГ W 1963030, кл. 42 тЗ 5/02, 1973. .2. Авторское свидетельство СССР I 308426, кл. G 06 F 5/02, 1969 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичных чисел в коде 4,2,2,1 в двоичные | 1979 |

|

SU860055A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1979 |

|

SU877521A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU734670A1 |

| Преобразователь двоично-десятичного кода в двоичный код | 1978 |

|

SU723567A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1975 |

|

SU634267A1 |

| Реверсивный преобразователь двоичного кода в двоично-десятичный | 1988 |

|

SU1621182A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1988 |

|

SU1529457A2 |

Авторы

Даты

1981-01-23—Публикация

1979-01-18—Подача