I

Устройство относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах с плавающей запятой оперирующих с последовательными кода ми, а также в каналах связи подобных устройств с внешними объектамИа например, с АВМ,

Наиболее эффективным является применение устройства для автоматического преобразования мантиссы и порядка в вычислительных структураХр построенных на основе цифровых интеграторов, множитель ных и суммирующих блоков, в которых переменные представлены в виде мантисс и приращений порядков. Для согласования цифровых интеграторов, множительных и суммирующих блоков между собой требуется включение устройства дл.я автоматы-jg ческого преобразования мантиссы и поряд- ка,

Известны, например, схема индикадш и управления положением плавающей аапя-

той jij J и система с плаваютей запятой

2,

Однако для применения в вычислительных структурах, построенных на основе цифровых интеграторов эти устройства неэффективны.

Наиболее близким к предлагаемому является Цифровой интегратор для однородных цифровых интегрирующих структур с плавающей запятойв отдельная функциональная часть которого предназначена для 111реобразован{1Я мантиссы и порядка вход- йой велйчкны в каждом йз входных каналов, к такому виду, чтобы прйращенйя порядков бьши одно{ азряйными.

Устройство содержит реверсивный счетчик, управляемый регистр сдвига, элемент запрета, сумматор порядка, блок аналткза порядкв} блок анализа разности порядков, блок формнровакьш приращения порядка, причем Бкоды сгшгаемых порядка и выход приращения порядка подключены к соответствуюивм Бходам реверсивного счетчика,

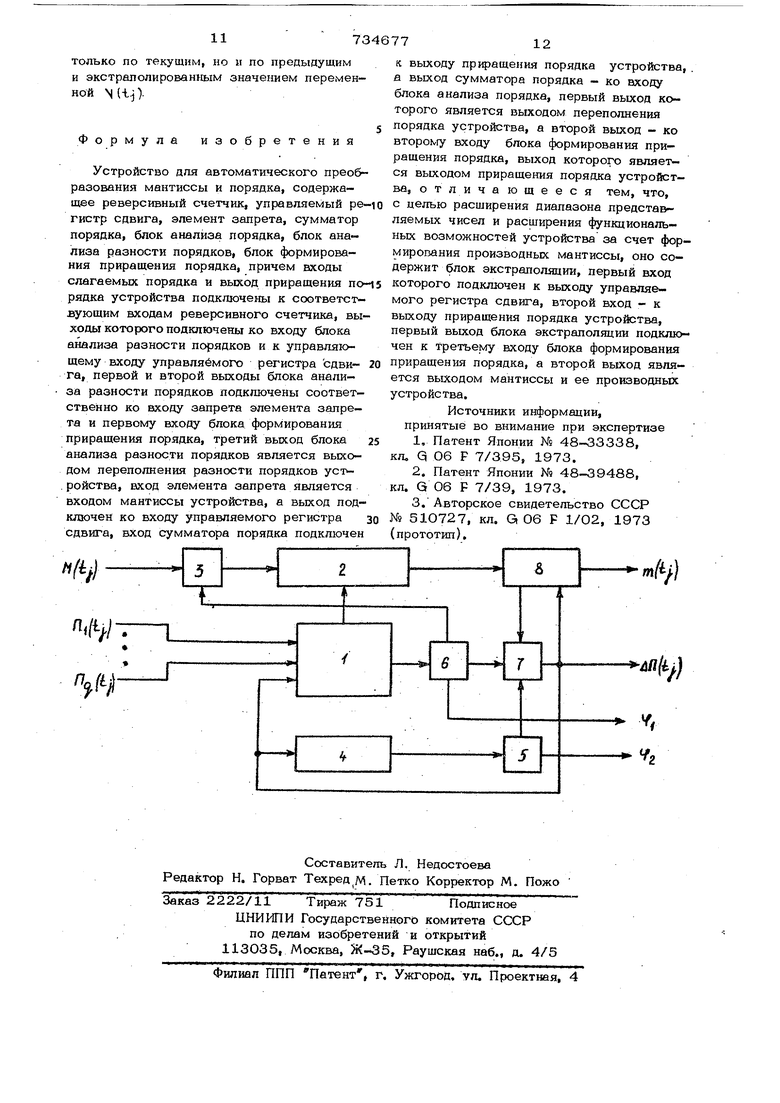

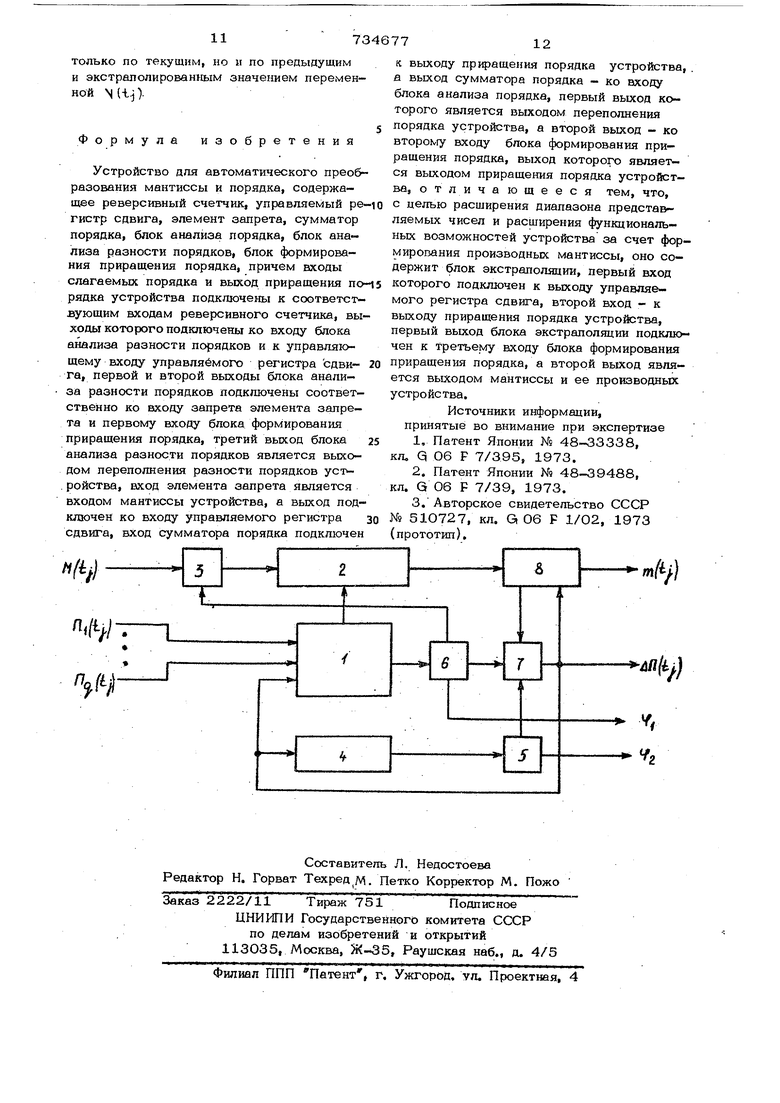

выходы которого подключены ко rJtCEV -ка анализа разности порядков и к управляющему входу управляемого регистра сдвига, первый и второй выходы блока анализа разности порядков подключены соответственно ко входу запрета элемента запрета и первому входу блока формирования приращения порядка, третий выход блока анализа разности порядков является выходом переполнения разности порядков, вход элемента запрета является входом мантиссы устройства, а выход подклю чен ко входу управляемого регистра сдвига, вход сумматора порядка подключен к выходу приращения порядка, а выход матора порядка - ко входу блока анализа порядка, первый выход которого является выходом переполнения порядка, а второй выход - ко второму входу блока формирования приращения порядка, выход которого является выходом приращения порядка з. Недостатком такого устройства являются ограниченные диапазоны представляемых чисел и узкие функциональные возможности устройства (отсутствует jj рование производных мантиссы). Цель изобретения - расширение диапазона представляемых чисел, расширение (функциональных возможностей устройства за счет формирования производньсс мантис сы. Сущность предлагаемого изобретения состоит в том, что устройство для автомати.еского преобразования мантиссы и порядка, состоящее из реверсивного счет чика управляемого регистра сдвига, эле- мента запрета, сумматора порядка, блока анализа порядка, блока анализа разности порядков, блока формирования приращения порядка, причем входы слагаемых порядка и выход приращения порядка устройства подключены к соответствующим входам реверсивного счетчика, выходы которого подключены ко входу блока анализа разности порядков и к управляющему входу управляемого регистра сдвига, первый и второй выходы блока анализа разности по рядков подключены соответственно ко входу запрета элемента запрета и первому входу блока формирования приращения порядка, третий выход блока анализа разности порядков является выходом переполнения разности порядков устройства, вход элемента запрета является входом мантиссы устройства, а выход подключен ко входу управляемого регистра сдвига, вход сумматора порядка подключен к вы ходу-приращения порядка устройства, а выход сумматора порядка - ко входу бло-. ка анализа порядка, первый выход которого является выходом переполнения порядка устройства, а второй выход - ко второму входу блока формирования приращения порядка, выход которого является выходом приращения порядка устройства, дополнительно содержит блок экстрапол1щии первый вход которого подключен к выходу управляемого регистра сдвига, второй вход - к выходу приращения порядка уст ройства, первый выход блока экстраполяции подключен к третьему входу блока формирования приращения порядка, а второй выход является выходом мантиссы и ее производных устройства. Дополнительно введенный блок экстраполяции расширяет диапазон представляемых и функциональные возможности устройства, формирует производные мантиссы. Схема устройства для автоматического преобразования .мантиссы и порядка представлена на чертеже,. где 1 - реверсивный счетчик, 2 - управляемый регистр сдвига, 3 - элемент запрета, 4 - сумматор порядка, 5 - блок анализа порядка, 6 - блок анализа разности порядков, 7 - блок формирования приращения порядка, 8 - блок экстраполяции. Устройство для автоматического прео разования мантиссы и порядка преобразует некоторую переменную va.v-M(t,j). ,(3) рдеМСЬ.О- мантисса, представленная в системе счисления с основанием ) (C|,,...)- порядок переменной V(-fcj) на входе устройства, (n-5(t), компоненты входно го порядка, q, - число компонент), по- ступающей на ЕКОД устройства в виде ман-. тиссы ) и одноразрядных приращений порядков vTl(i:.j),...,Mnrt,(t3-l),Ti3 формы () в - -. J . PI /-t- t i. (.-fc niltj) гдетир, tt j) - мантисса и порядок переменной N(.-bj1 на выходе устройства, причем на выход устройства выдаются мантиссы m (.tj) (либо ее экстраполированное з на- чение) и одноразрядное приращение порядKa7n(i; ). Каждое из прирашений порядков ...,), принимает РЯно из значений - 1,0, 1, причем 7 Л (V - H V i i-V где fci (j -0,1..,.) - дискретные моменты времени. Следовательно, приращение порядка ) равно (.jVn-(. Содержимое реверсивного счетчика 1, имеющего S разрядов, представляет собой разность порядков .Ц Ctj), которая получается путем накопления одноразрядных приращений порядкoвЛ П Лtj),...,, vn(-t.) эавных 0,1 1, в соответствии с выражением .j-).-.-«-n CV-nt 3M .,, . Управляемый регистр сдвига 2, общая длина которого равна (2 -1) разрядов, представляет собой сдвиговый регистр, состоящий из S частей ( б - число млад ших разрядов реверсивного счетчика 1, S $: S ) выход 1 -го ( V 1,2, ..., S ) цифрового разряда счетчика соединен с той частью управляемого регистра, число разрядов которой равно . С помощью управляемого регистра 2 сдвига и реверсивного счетчика 1 вьшолняется преобразование мантиссы переменной Vi-tjV Это преобразование включается в сдвиге ман тиссы КЛ HjO в соответствии с разностью порядков I (), так что на выходе управляемого регистра сдвига 2 получается мантисса ma.jV-Nv( имеющая порядок nCijV Это преобразование выполняется в дискретные промежутки t. времени, называемые цикл1ами преобразования, причем tj-t; cottst-Между состояниями реверсивного счетчика 1, од- позначно определяемыми разностью иор:адков UC-bjX и длиной управляемого peгиc1 ра сдвига 2 установлено следующее соответствие:состояние счетчика .i длина управляемого :гистра сдвига 2 La3V-vnai«. , l.t:,V-min p где июч L упр. О - наибольшее значение разности порядков, при котором и мен ше которого преобразование порядков со провождается сдвигом (2) и больше которого из-ва ограниченной длины управляемогорегистра сдвига 2 сдвиг мантиссы ДЛ не производится: (2) 6 - значение разности порядков, удовлетворяющее соотношение .„р р,г- R,mar-..v..pp V- длина управляемого регистра сдвига, соответствуюшая состоянию счетчика ий-)) P,;wiM U jnp70- наименьшее значение разности порядков, при котором и больше которого преобразование порядков сопровождается сдвигом мантиссы (2) и меньше которого сдвиг мантиссы (2) не производится. Элемент 3 запрета представляет собой логическую схему, имеющую два выхода и один вход. На первый вход, являющийся входом всего устройства, поступает ма№тисса1 Уи )| на другой, запрещающий, вход Подается сигнал запрета. Мантисса f(tj) через элемент 3 запрета и соответственно через управляемый регтдатр сдвига 3 проходит в том случае когда сигнал на запрещающем входе элемента 3 равен логическому ,нуто Логит-1еская единтща на запрещающем элементе 3 блокирует прохождеййе информации. Сумматор 4 порядка предназначен для хранения и вычисления порядка П(.)-Вычисление нового значения порядка произвоокжся в соответствии с выражением (. так что новое значение порядка получается как сумма прежнего значения порядка и нового приращения порядка «j n(,-tj). Блок S анализа порядка, представляющй§ собой логические схемы, подключенные к сумматору 4 порядка, вырабатывает в зависимости от содержимого сумматора сигналы ( 1. если n(t; , r, (ПН: . , если na )--wa)i.l, 1, ec-mj nttj lbmivi n (Txa.)imwrO 0, если П( Сг.) -г.п N - пч(1р ®спи n(t..;,.)mitrin, (nC-ti .):} . , если n(4..r...,)minn, первый из которых вь.мает-ся не выход ус-гройства в качестве сигнала 2 положительного переполнения порядка второй и третий используются для (|юрмирования приращения порядка t(-t-iV Максимальное и минимальное VYiinH значения порядка определяется эмкостью памяти сумматора 4 порядка, Шок 6 анализа разности порядков представляющий собой лог-вческие схемы входы которых соединены с выходами разрядов реверсивного счетчика 1, вырабаты вает сигналы 1, если Ut;)maixL (LU)niaT(.b.,np), если l,(-t.))4b 1, если (b(-ijne) Oj если 1, если U(-t.,. (L(43)e) ,0, если I (t.jysb 1, если L,(t)hiinl.v,.p {Ц Л т1пЬ..,, .i Р о, если 1.)( первый из -которых выдается на выход устройства в качестве сигнала 4 о положительном переполнении разности поряд ков, второй и третий используются для формирования прйра Яения порядка чгПХ-Ь,,) четвертый сигнал необходим для блокировки прохождения мантиссы через управ ляемый регистр сдвига 2. Блок 7 формирования приращения порядка, представляющий собой логические схемы, формирует, код приращения порядка в соответствии с формулой Г+1,если 1vTl(-tj)lvl,(ij)(j)rnmn ,если -5 ;mt --iлUaj t n(ц)vvniv ОБ остальныхслучаях , (5) Приращение порядка выдается на выход всего устройства, на сумматор 4 порядка на реверсивный счетчик 1 и блок 8 экст раполяций. Сигналы, необходимые для работы блока 7, поступают: vtvn(-t.jl,-1-4nttj) от блока 8,,j(tj)t - от блока 6 ntt.j.) г n,n4t.j.vi:i-inn- бласа 5, БЛОК 8 экстраполяции на основе хранимых в нем мантисс предыдущих значений переменной V (ij) и ее разностей m(-t.j.(t.),...,,tt-, (Ъ„.)--v - wl-fc,,,-.,1, J-л Т)--1,2,.-..,п; bj - индекс, указывает на то, что Информация ОТНОСИ1СЯ к предыдущему циклу преобразования, аналогично индекс указывает, что информация относится к предьщушему циклу по отношению к -Ь J И - порядок формулы экстраполяции и . данной мантиссы vril-bjO выполняет операдии: Vni(-t,j)- mUjVwiU.j- Vt-tp- wtt V ni U.j), YnUiV- J-Va3V ;l(t3,,: V S vrtti ), y-o л w(. где Ti(-tjV-4) экстраполтфованного значения переменной V tt j) В зависимости от условий применения устройства на вьнсод блока,экстраполяции (соот ветственно и на выход устройства) может вьшаваться либоП1(-Ь), либо in(t,j,. либо вся информация, хранимая-в блоке экстраполяциИэ либо часть ее. Результаты вычислений блока 8 экстраполяции, кроме m (tj), запоминается. Порядок формулы экстраполяции в зависимости от требований может быть равен Ор 1, 2,..,. При П О экстраполяции как таковая от сутствует. После определения в данном цикле преобразования приращения порядке П(-Ц) все вновь полученные мантиссы т (tj) , vvn (t), о.., m ) нормализуются на один разряд в соответствии с выражениями: Ли) ,..)- X-0,1,---.Vi-1 Блок 8 экстраполяции .вырабатывает также сигнал -f 1V П Ct,jX 1 sr Л (bf) необходимые для формирования приращения порядка nCfcj); в соответствии с логическими выражениями: 1 ,если/vti Ct. |w( -« i . J- -1 (t. а;,...) -t-I OCi-y , ( Ь/ в остальных случаях: (7) 1,если jn, (i)| R л bm(,..AJg«- MCt.i ). -p ma. о в остальных случаях где V,K . соответственно дизъюнкция и конвъюнжция лог1гаеских высказываний, fвеличина5 соизмеримая с относитехгьной погрешностью представления переменной V(-b), т.е.. Е«КЛ Расширение диапазона изменения переменных достигается за счет введения дополнительного блока экстраполяции. Введение блока 8 экстраполяции позволяет следить за поведением самой переменной N(ij). Гак, -Hvn(-tj) выдаваемый бло ком 8 экстрапоп;ации, благодаря учету аредйстории переменной V(.-tj) позволяет переменной и тем самым обеспечить ее представление в виде мантиссы vn (tj)и о норазрядного приращения порядка vvn ) Отсутствие блока .8 экстрчпоп5щии может привести к следующему положению: если w() 4imll.)-( „к) ( М,. число разрядов мантиссы Vn (t j) или fAltA m(,-t, при 11-2,(t.v-n,{t vma мu-p:, ..,j., т(1:. --hi U)xi wCtp ivvi(V--6d-r) и при Tl 6 имеет место неравенство yti(VR l) указывающее на возможность появления переполнения мантиосы, как экстраполированного значения ni(t,, так и неэкстраполированного в последующем цикле. Введение блока 8 экстраполяции исключает подобно положение, т.е. расширяет допустимый ди пазон применения переменной Nlt-jl,так ка формирование приращения порядка П i.) осуществляется таким образом (см. (,7), так (R:lR:V.)1Работает устройство для автоматичес кого преобразования мантиссы и порядка следующим образом, В каждом цикле преобразования на Еход устройства переменная V (-fcj ) поступает в виде мантиссы WvCi:-}) и одноразрядных приращений поряд ков v П-( (t-j) , ..., V Пц(,-Ъ.))Приращение () , ..-tj) поступают на реверсивный счетчик 1, в котором форм ируется новое значение разности порядков Ul.tj)- Управляемый регистр сдвига 2 в соответствии с новым состоянием счетчика 1 настраивается на определенную длин Мантисса WvCt-j) переменной VCt.j-) в зависимости от сигнала U(t3 упр. либо проходит, либо нет через элемент 3 запрета и соответственно через управляемый регистр сдвига 2 с задержкой, определяемой длиной управляемого регист ра сдвига 2. В сумматоре 4 порядка получается новое значение порядка rivrj) преобразованной переменной NCijT В зависимости от предыдущего порядка, хранящегося в сумматоре 4 порядка блок 5 анализа порядка вырабатывает сигналы ntt. max П, П Ct.): WiiH П,Т1 ЫУ П. Блок 6 анализа разности порядков, вырабатывает сигналы (j iB, Ht Л Е, UltjXvnW L,JПp,V,). , В блок 7 формирования приращения поряд ка vTl Н-} поступают сигналы из блока 5 TH.t.j.)imivi n,n(t.j-i)vviwn77 Блок 7 в зависимости от сигналов на его входах tUy)&,i.Uo,).), na.,)hm-iM h,n(,V.-i П Формирует код одноразрядного приращения Л (tpKOBoro порядка Л (tp переменной )- Это приращение порядка постукает на выход, на счетчик 1, на блок 8 экстраполяции и сумматор 4 порядка, В счетчш е 1 разность порядков Ii.t. корректируется в соответствии.с ignttp- На вход блока 8 экстраполяции проходит мантисса Ш ttj), отвечающая порядку n(i;) предыдущего цикла преобразования. В блоке 8 экстраполяции выполняют операции (6)J и вырабатываются сигналы +1 х7 П (:t), 1 Ч П (ij ) и по приращению порядка П (-tj ) производится нормализация новых мантисс. Мантисса nftj) (или hi()преобразованной переменной с выхода блока S акстраполяции : поступает на вькод устройства. Если Ч- с выхода блока 6 и Ч2 с выхода блока 5 отсутствует, т,е.1(1)1пакЦ wni-tj-ilshiann, то начинается новый цикл преобразования. В качестве примера приводится сжтимальный вариант технических характеристик предлагаемого устройства при его использовании и цифровых интегрирующих структурах: - представление переменных - в виде мантисс и одноразрядных пр фащений порядковг-основание системы счисления , -реверсивный счетчик 1| ,%-5, 5 6, q-2 (для двухвходовых интеграторов и множительных устройств) | управляемый регистр сдвига 2: общая длина . -блок 8 экстраполяции: 2 j -сумматор порядка; пахП: 32,П11пП:32. Введение блока 8 экстраполяции расширяет допустимый диапазон изменения переменной (.tj) и ее производных (или разностей). В прототипе не допустимо изменение переменной V(ij) таким образом, чтобы имело место (tj-i)- VM (i;4) 0,111, ....Д, tt-j) ОД1 ... при производных значени5зх порядка, что собственно и является ограничением изменения переменной VCi), так -как т (. 2 ни при каком единичном П(,) не дает tv«(-t; V2 Vl« В предлагаемом устройстве порядок n(fcj) формируется таким образом, что практигчески исключается указанный вариант значений UlCi j-i vwiti , vnt-fcjjl, так KaKVTit- :) формируется «

только по текущим, но н по предыдущим и экстраполированным значением переменной Nli-jl

Формула изобретения

Устройство для автоматического преобразования мантиссы и порядка, содержащее реверсивный счетчик, управляемый ре- гистр сдвига, элемент запрета, сумматор порядка, блок анализа порядка, блок анализа разности порядков, блок формирования приращения порядка, причем входы слагаемых порядка и выход приращения no рядка устройства подключены к соответствующим входам реверсивного счетчика, выходы которого подключены ко входу блока анализа разности порядков и к управляющему входу управляемого регистра сдвига, первой и второй выходы блока анали за разности порядков подключены соответственно ко входу запрета элемента запрета и первому входу блока формирования приращения порядка, третий выход блока анализа разности порядков является выходом переполнения разности порядков уст ройства, вход элемента запрета является входом мантиссы устройства, а выход подключен ко входу управляемого регистра сдвига, вход сумматора порядка подключен

к выходу приращения порядка устройства а выход сумматора порядка - ко входу блока анализа порядка, первый выход которого является выходом переполнения порядка устройства, а второй выход - ко второкггу входу блока формирования приращения порядка, выход которого является выходом приращения порядка устройства, отлича ющееся тем, что, с целью расширения диапазона представляемых чисел и расширения функциональных возможностей устройства за счет формирования производных мантиссы, оно содержит блок экстраполяции, первый вход которого подключен к выходу управляемого регистра сдвига, второй вход - к выходу приращения порядка устройства, первый выход блока экстрапол5щии подклл чен к третьему входу блока формирования приращ ения порядка, а второй выход является выходом мантиссы и ее производных устройства.

Источники информации, принятые во внимание при экспертизе

1.Патент Японии № 48-33338, кл, 3 Об F 7/395, 1973.

2.Патент Японии № 48-39488, кл. G 06 F 7/39, 1973.

3.Авторское свидетельство СССР № 510727, кл. Gt 06 F 1/02, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор с плавающей запятой | 1975 |

|

SU590774A2 |

| Цифровой интегратор для однородных цифровых интегрирующих структур (оцис) с плавающей запятой | 1973 |

|

SU510727A1 |

| Экстраполятор приращений для однородных цифровых интегрирующих структур /оцис/ с плавающей запятой | 1972 |

|

SU443397A1 |

| Цифровой интегратор | 1975 |

|

SU661572A1 |

| Устройство для выравнивания порядков чисел,представленных в системе остаточных классов | 1973 |

|

SU781812A1 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для преобразования сейсмической информации | 1981 |

|

SU1038904A1 |

| Вычислительное устройство цифровой интегрирующей структуры | 1977 |

|

SU703840A1 |

| Цифровой интегратор | 1975 |

|

SU650084A1 |

Авторы

Даты

1980-05-15—Публикация

1976-05-11—Подача