(54) ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

1

Изобретение относится к импульсной технике и предназначено для деления частоты импульсов.

По основному авт. св. № 733110 известен делитель частоты импульсов, содержащий первый, второй, третий и четвертый разряды, а также первый, второй и третий межразрядные элементы И-НЕ, каждый из разрядов содержит коммутационный триггер и триггер памяти, каждый из которых содержит первый и второй элементы И-НЕ, причем выход первого соединен с входом второго, выход Которого соединен с входом первого элемента И-НЕ того же триггера, и выходы первого и второго элементов И-НЕ триггеров соединенысоответственно с единичными и нулевыми входами того же триггера, единичный выход триггера памяти первого разряда соединен с единичным входом коммутационного триггера того же разряда, единичный выхрд коммутадионного триггера которого соединен с входом первого межразрядного элемента И-НЕ, выход которого соединен с нулевым входом коммутационного триггера второго разряда и единичным и нулевым входами коммутаци,онного триггера третьего разряда, единичный вход триггера памяти первого разряда соединен с нулевым выходом коммутационного триггера первого разряда, единичный выход триггера памяти второго разряда соединен с единичным входом коммутационного триггера того же разряда, единичный выход коммутационного триггера которого соединен с входом второго межразрядного элемента И-НЕ, выход которого соединен с нулевым и единичным входами коммутационного триггера Третьего разряда, нулевой, выход коммутационного триггера третьего разряда соединен с нулевыми входами триггеров памяти первого, второго и третьего разрядов, единичным входом триггера памяти четвертого раз ряда, входом второго межразрядного элемента И-НЕ, нулевыми входами коммутационных триггеров первого и второго разрядов, а также с единичным входом коммутационного триггера четвертого разряда и входом третьего межразрядного элемента И-НЕ, выход которого соединен с единичным входом коммутационного триггера четвертого разряда и нулевым входом коммутационного триггера третьего разряда, нулевой выход

ко1М.мутационного триггера второго разряда соединен с единичным входом триггера памяти второго разряда, нулевыми входами коммутационного триггера и триггера памяти первого разряда и входом первого межразрядного элемента И-НЕ, единичный выход коммутационного триггера третьего разряда соединен с единичными входами триггера памяти третьего разряда и коммутационного триггера четвертого разряда и нулевыми входами коммутационных триггеров и триггеров памяти.первого и второго разрядов, а также с входами первого и второго межразрядных элементов И-НЕ, нулевой выход триггера памяти третьего разряда соединен с входом третьего межразрядного элемента И-НЕ, единичный коммутационного триггера четверто0 разряда соединен с нулевыми входами коммутационных триггеров и триггеров памяти первого и третьего разрядов, нулевыми входами коммутационного триггера второго разряда и триггера памяти четвертого разрада и входом третьего межразрядного элемента И-НЕ, нулевой выход триггера памяти четвертого разряда соединен с нулевым выходом коммутационного триггера того же разряда, а тактовый вход соединен с нулевыми входами коммутационных триггеров первого, второго и третьего разрядов и единичными входами коммутационных триггеров третьего и четвертого разрядов 1).

Недостаток этого делителя частоты импульсов -- относительно неболы11ой коэффициент деления, что ограничивает функциональные возможности делителя.

Цель изобретения-увеличение коэффициента деления.

Поставленная цель достигается тем, что в делителе частоты импульсов, содержащем первый, второй, третий и четвертый разряды, а также первый, .второй и третий межразрядные элементы И-НЕ, каждый из разрядов содержит коммутационный триггер и триггер памяти, кдждый из которых содержит первый и второй элементы И-НЕ, причем выход первого соединен с входом второго, выход которого соединен с входом первого элемента ИНЕ того же триггера, и выходы первого и второго элементов И-НЕ триггеров соединены соответственно с единичным и нулевым выходами этого триггера, а их входы - с единичными и нулевым-н входами того же триггера, единичный выход триггера памяти первого разряда соединен с единичным входом коммутационного триггера того же разряда, единичный выход коммутационного триггера которого соединен с входом первого межразрядного элемента И-НЕ, выход которого соединен с нулевым входом коммутационного триггера второго разряда и единичным и нулевым входами коммутационного триггера третьего разряда, единичный

ВХОД триггера памяти второго разряда соединен с нулевым выходом коммутационного триггера первого разряда, единичный выход триггера памяти второго разряда соединен с единичным входом коммутационного триггера того же разряда, единичный выход коммутационного триггера которого соединен с входом второго межразрядного элемента И-НЕ, выход которого соединен с нулевым и единичным входами коммутационного триггера третьего разряда, нулевой выход коммутационного триггера третьего разряда соединен с нулевыми входами триггеров памяти первого, второго и третьего разрядов, единичным входом триггера памяти четвертого разряда, входом второго межразрядного элемента И-НЕ, нулевыми входами коммутационных триггеров первого и второго разрядов, а также с единичным входом коммутационного триггера четвертого разряда и входом третьего межразрядного элемента И-НЕ, выход которого соединен с единичным входом коммутационного триггера четве ртого разряда и нулевым входом коммутационного триггера третьего разряда, ну- . левой выход коммутационного триггера второго разряда соединен с единичным

входом триггера памяти второго разряда, нулевыми входами коммутационного триггера и триггера памяти первого разряда и входом первого межразрядного элемента И-НЕ, единичный выход коммутационного триггера третьего разряда соединен с

0 единичными входами триггера памяти третьего разряда и коммутационного триггера четвертого разряда и нулевыми входами коммутационныхтриггеров и триггеров памяти первого и второго разрядов, а также с входами первого и второго межразрядных

элементов И-НЕ, нулевой выход триггера памяти третьего разряда соединен с входом третьего межразрядного элемента. И-НЕ, единичный выход коммутационного триггера четвертого разряда соединен с нулевыми

0 в}дэдами коммутационных триггеров и триггеров памяти-первого и третьего разрядов, нулевыми входами коммутационного триггера второго разряда и триггера памяти четвертого разряда и входом третьего межразрядного элемента И-НЕ, нулевой выход триг.5 гера памяти четвертого разряда соединен с нулевым входом ко.ммутационного триггера того же разряда, тактовый вход соединен с нулевыми входами коммутационных триггеров первого, второго и третьего разрядов и единичными входами ком.мутационных триггеров третьего и четвертого разрядог:. выход первого межразрядного логического элемента И-НЕ соединен с единичны.м выходом коммутационного риггера четвертого разряда, едичниный выход которого соединен с нулевым входом триггера памяти второго разряда и с дополннтельны.м входом первого межразрядного логического элемента И-НЕ.

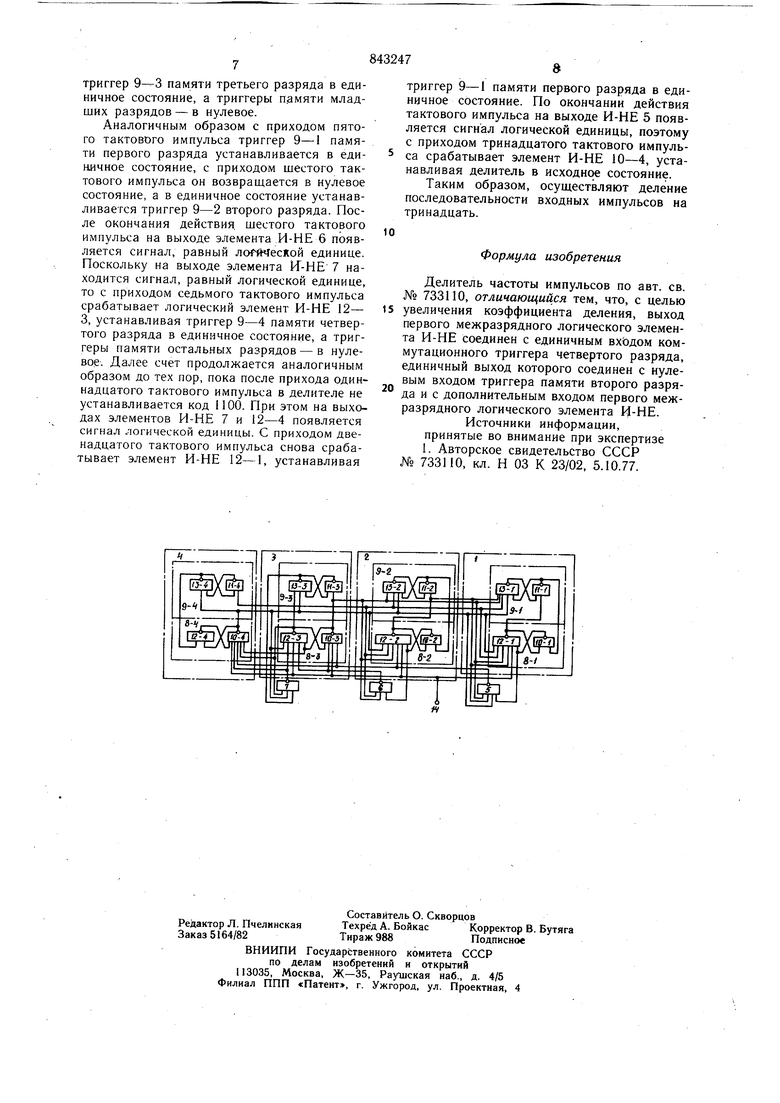

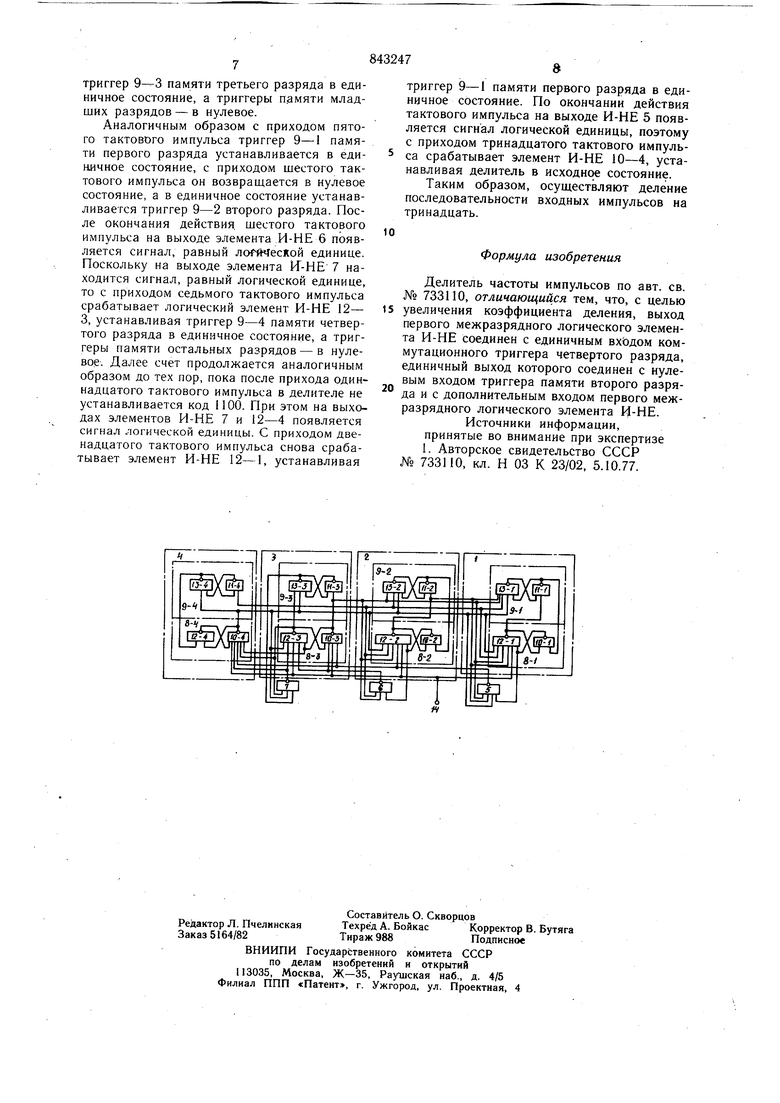

На чертеже представлена схема устройства.

Делитель частоты импульсов содержит первый 1, второй 2, третий 3 и четвертый 4 разряды, а также первый 5, второй 6 и третий 7 межразрядные элементы И-НЕ, каждый из разрядов i содержит коммутационный триггер 8-i и триггер 9-i памяти, каждый из которых содержит первый 10-1 1 11-i и второй 12-i и 13-i элементы ИНЕ, причем выход первого соединен с входом второго, выход которого соединен с входом первого элемента И-НЕ того же триггера, и выходы первого и второго элементов И-НЕ триггеров соединены соответственно с единичным и нулевым выходами этого триггера, а их входы - с единичными и нулевыми входами того же триггера, единичный выход триггера 9-1 памяти первого разряда соединен с единичным входом коммутационного триггера 8-I того же разряда, единичный выход коммутационного триггера которого соединен с входом первого межразрядного элемента И-НЕ 5, выХод которого соединен с нулевым входом коммутационного триггера 8-2 второго разряда и единичным и нулевым входами коммутационного триггера 8-3 третьего разряда, единичный вход триггера 9-1 памяти первого разряда соединен с нулевым выходом коммутационного триггера 8-1 первого разряда, единичный выход триггера 9-2 памяти второго разряда соединен с единичным входом коммутационного триггера 8-2 того же разряда, единичный выход коммутационного триггера 8-2 соединен с входом второго межразрядного элемента И-НЕ 6, выход которого соединен с нулевым и единичным входами коммутационного триггера 8-3 третьего разряда, нулевой выход коммутационного триггера 8-3 третьего разряда соединен с нулевыми входами триггеров 9-1, 9-2 и 9-3 памяти соответственно первого, второго и третьего разрядов, единичным входом триггера 9-4 памяти четвертого разряда, входом второго межразрядного элемента И-НЕ 6, нулевыми входами коммутационных триггеров 8-1 и 8-2 соответственно первого и второго разрядов, а также с единичным входом коммутационного триггера 8-4 четвертого разряда и входом третьего межразрядного элемента И-НЕ 7, выход которого соединен с единичным входом коммутационного триггера четвертого разряда и нулевь1М входом коммутационного триггера 8-3 третьего разряда, нулевой выход коммутационного триггера 8-2 второго разряда соединен с единичным входом триггера 9-2 памяти второго разряда, нулевыми входами коммутационного триггера 8-1 и триггера 9-1 памяти первого разряда и входом первого межразрядного элемента И-НЕ 5, единичный выход коммутационного триггера 8-3 третьего разряда соединен с единичными входами триггера 9-

3 памяти третьего разряда и коммутационного триггера 8-4 четвертого разряда и нулевыми входами коммутационных триггеров 8-1 и 8-2 и триггеров 9-1 и 9-2 памяти первого и второго разрядов, а также 5 с входами первого 5 и второго 6 межразрядных элементов И-НЕ, нулевой выход триггера 9-3 памяти третьего разряда соединен с входом третьего межразрядного элемента И-НЕ 7, единичный выход коммутацион.,. ного триггера 8-4 четвертого разряда соединен с нулевыми входами коммутационных триггеров 8-1 и 8-3 и триггеров 9-1 и 9-3 памяти первого и третьего разрядов, нулевыми входами коммутационного триггера 8-2 второго разряда и триггера 9-4

15 памяти четвертого разряда и входом третьего межразрядного элемента., И-НЕ 7, нулевой выход триггера 9-4 памяти четвертого разряда соединен с нулевым входом коммутационного триггера 8-4 того же разряда, выход первого межразрадного логического элемента И-НЕ 5 соединен с единичным входом коммутационного триггера 8-4 четвертого разряда, единичный выход которого соединен с нулевым входом триггера 9-2 памяти второго разряда и с дополнительным

5 входом первого межразрядного логического элемента И-НЕ 5, а тактовый вход 14 соединен с нулевыми входами коммутационных триггеров 8-1, 8-2 и 8-3 соответственно первого, второго и третьего разрядов и единичными входами коммутационных триггеров 8-3 и 8-4 соответственно третьего и четвертого разрядов.

Делитель частоты импульсов работает следующим образом.

В исходном состоянии все триггеры памяти находятся в нулевом состоянии, а тактов1з1Й импульс, поступающий на вход 14, отсутствует, т.е. равен логическому нулю. В этом случае на выходах элементов И-НЕ 5, 6 и 7 - логический нуль,поэтому с приходом первого тактово1о импульса срабатывает только логический элемент И-НЕ 12-1, устанавливая триггер 9 - 1 памяти первого разряда в единичное состояние. После окончания действия тактового имнульса на выходе элемента И-НЕ 5 появляется сигнал логической единицы-. С приходом следующего

S тактового импульса срабатывает элемент ИНЕ 12-2, устанавливая триггер 9-2 памяти второго разряда в единичное состояние, а триггер 9-1 памяти первого разряда - в нулевое. С приходом третьего так -шого импульса снова срабатывает элемент И-НЕ 12-I. По окончании действия тактового импульса на выходе элемента И-НЕ 5 появляется сигнал логической единицы, а по- .скольку и триггер 9-2 памяти второго разряда находится в единичном состоянии, то

5 на выходе элемента И-НЕ 6 появляется логическая единица. Следовательно, с приходом четвертого тактового импульса срабатывает элемент И-НЕ 10-3, устанавливая

триггер 9-3 памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов - в нулевое.

Аналогичным образом с приходом пятого тактового импульса триггер 9-1 памяти первого разряда устанавливается в единичное состояние, с приходом шестого тактового импульса он возвращается в нулевое состояние, а в единичное состояние устанавливается триггер 9-2 второго разряда. После окончания действия, шестого тактового импульса на выходе элемента И-НЕ 6 появляется сигнал, равный лоММеской единице. Поскольку на выходе элемента If-HE 7 находится сигнал, равный логической единице, то с приходом седьмого тактового импульса срабатывает логический элемент И-НЕ 12- 3, устанавливая триггер 9-4 памяти четвертого разряда в единичное состояние, а триггеры памяти остальных разрядов - в нулевое. Далее счет продолжается аналогичным образом до тех пор, пока после прихода одиннадцатого тактового импульса в делителе не устанавливается код 1100. При этом на выходах элементов И-НЕ 7 и 12-4 появляется сигнал логической единицы. С приходом двенадцатого тактового импульса снова срабатывает элемент И-НЕ 12-1, устанавливая

триггер 9-1 памяти первого разряда в единичное состояние. По окончании действия тактового импульса на выходе И-НЕ 5 появляется сигнал логической единицы, поэтому с приходом тринадцатого тактового импульса срабатывает элемент И-НЕ 10-4, устанавливая делитель в исходное состояние.

Таким образом, осуществляют деление последовательности входных импульсов на тринадцать.

Формула изобретения

Делитель частоты импульсов по авт. св. № 733110, отличающийся тем, что, с целью увеличения коэффициента деления, выход первого межразрядного логического элемента И-НЕ соединен с единичным вхЬдом коммутационного триггера четвертого разряда, единичный выход которого соединен с нулевым входом триггера памяти второго разряда и с дополнительным входом первого межразрядного логического элемента И-НЕ.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 733110, кл. Н 03 К 23/02, 5.10.77.

Авторы

Даты

1981-06-30—Публикация

1979-01-31—Подача