1

Изобретение относится к импульсной технике.

Известен делитель частоты, содержащий четыре разряда, каждый разряд которого состоит из триггера памяти, коммутационного триггера и элемента И-НЕ, причем в первых трех разрядах единичный выход триггера памяти соединен с единичным входом коммутационного триггера, нулевой выход которого соединен с единичным входом триггера памяти данного разряда, с нулевыми входами всех триггеров всех предьщущих разрядов и со входом элемента И-НЕ предьщушего разряда, нулевой выход триггера памяти четвертого разряда соединен с нулевыми и входами коммзггационных триггеров втппого и четвертого разрезов, выход элемента И-НЕ первого разряда соединен с обоими входами коммутационного триггера второго разряда и с единичным входом коммутационного триггера четвертого разряда, выход элемента И-НЕ второго разряда соединен с нулеым входом коммутационного триггера третьего разряда, выход элемента И-НЕ четвертого разряда соединен с единичными входами триггера памяти и коммутационного триггера разряца, а также с нулевыми входами всех триггеров первого и второго разрядов, единичный выход комк1утационного триггера четвертого разряда соединен с нзлевыми входами триггеров памяти первого и четвертого разрядов, с нулевыми входами коммутационных триггеров первого и второго разрядов и со входом элемента И-НЕ первого разряда 1 .

Данный делитель не обеспечивает достаточ10ной надежности деления частоты импульсов на двенадцать.

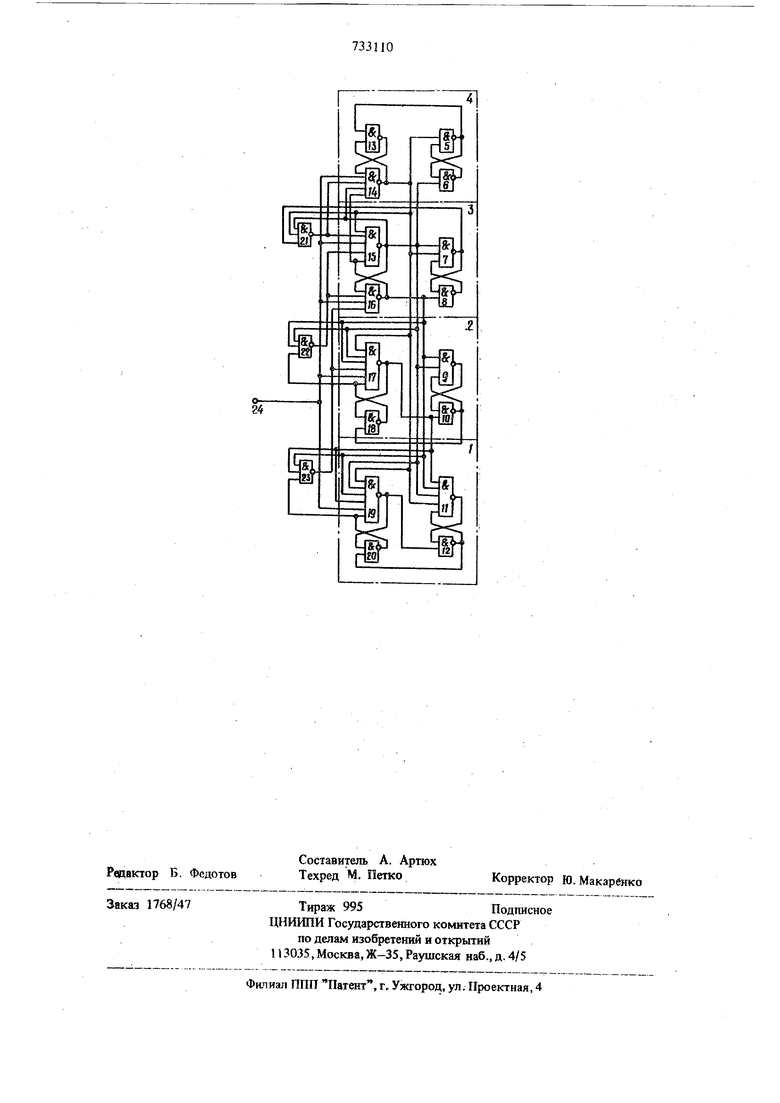

Наиболее близок по технической сущности к предлагаемому делитель частоты, содержащий четыре разряда, каждый из кото15рых содержит триггер памяти, коммутационный триггер и элемент И-НЕ, причем в первых двух разрядах единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход кото20рого соединен со входом элемента И-НЕ, а нулевой выход соединен с единичным входом триггера памяти, едш)кчнь1Й выход коммутационного триггера третьего разряда и нулевой 37 выход коммутационного триггера второго разряда соединены с нулевыми входами коммутационных триггеров, триггеров памяти и со входами элементов И-НЕ всех предьщущих разрядов, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом триггера памяти этого разряда, с нулевыми входами триггеров памяти и коммутационных триггеров всех предыдущих разрядов, а также со входом элемента И-НЕ второго разряда; нулевой выход триггера памяти четвертого разряда соединен с нулевым входом коммутационного триггера этого же разряда, единичный вь1ход которого соединен с нулевыми входами триггеров памяти первого третьего и четвертого разрядов, с нулевыми входами коммутационных грштеров всех предыдущих разрядов и со входом элемента И-НЕ третьего разряда, выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда соединен с обоими входами коммутационного триггера третьего разряда, а выход элемента И-НЕ третьего разряда соединен с единичным входом коммутационного триггера четвертого разряда 2. Этот делитель недостаточно надежен. Цель изобретения - повышение надежности делителя. Поставленная цель достигается тем, что в делителе частоты, содержащем три межразря ных элемента И-НЕ, четыре разряда, каждый из которых состоит из триггера памяти и коммутационного триггера, выполненных на элементах , причем в первых двух разря дах единичный выход триггера памяти соедине с единичным входом коммутационного триггера, единичный выход которого соединен со входом первого межрязрядного элемента И-Н а нулевой выход соединен с единичным входом триггера памяти, единичный выход коммутационного триггера третьего разряда и нулевой выход коммутационного триггера второ го разряда соединеиы с нулевыми входами коммутацио1шых триггеров, триггеров памяти и со входами межразрядных элементов И-НЕ всех предыдущих разрядов, нулевой выход коммутационного триггера третьего разряда соединен с единичным входом триггера памят этого разряда, с нулевыми входами триггеров памяти и коммутационных триггеров всех пре дьщущих разрядов, а также со входом второг межразрядного элемента И-НЕ; нулевой выход триггера памяти четвертого разряда соединен с нулевым входом коммутационного триггера этого же разряда, единичный выход которого соединен с нулевыми входами триггеров памяти первого, третьего и четвертого азрядов, с нулевыми входами коммутационых триггеров всех предьщущих разрядов и о входом третьего межразрядного элемента И-НЕ; выход первого межразрядного элемента И-НЕ соединен с нулевым входом коммутационного триггера второго разряда, выход второго межразрядного элемента И-НЕ соединен с обоими входами коммутационного триггера третьего разряда, а выход третьего межразрядного элемента И-НЕ - с единичным входом коммутационного триггера четвертого разряда, выход первого межразрядного элемента И-НЕ соединен с единичным входом коммутационного триггера третьего разряда, нулевой выход триггера памяти третьего разряда - со входом третьего межразрядного элемента И-НЕ, выход которого соединен с нулевым входом коммутационного триггера третьего разряда, единищгый выход этого триггера соединен с единичным входом коммутационного триггера четвертого разряда, а нулевой выход - с единичными входами триггера памяти и коммутационного триггера четвертого разряда. Структурная электрическая схема описьтаемого делителя приведена на чертеже. Описываемый делитель содержит четыре разряда 1-4, в состав которых входят коммутационные триггеры на элементах И-НЕ 5-12 и триггеры памяти на элементах И-НЕ 13-20, межразрядные элементы И-НЕ 21-23. Входной сигнал подается на шину 24. Принцип работы делителя заключается в следующем. В исходном состоянии все триггеры памяти находятся в нулевом состоянии, а тактового импульса, поступающего по нхине 24, нет, он равен логическому нулю. В этом случае на выходах элементов И-НЕ 21, 22, 23, 6, 8, 10, 12 - логический нуль, на выходах остальных элементов И-НЕ - логическая единица, поэтому с приходом первого тактового импульса срабатывает только элемент И-НЕ 19, устанавливая триггер памяти первого разряда 1 в единичное состояние. После окончания действия тактового импульса на выходе элемента И-НЕ 23 появляется логическая единица. С приходом следующего тактового импульса срабатьшает элемент И-НБ 17, устанавливая триггер памяти второго разряда 2 в единичное состояние, а триггер памяти первого разряда 1 - в нулевое состояние С приходом третьего тактового импульса срабатывает снова элемент И-НЕ 19, поскольку на выходах элементов И-НЕ 13, 21-23 логические нули. По окончании действия тактового импульса на выходе элемента И-НЕ 23 появляется логическая единица, а поскольку и триггер памяти второго разряда 2 находится в единичном состоянии, на выходе элемента И-НЕ 22 также логическая единица. Следовательно, с приходом четвертого тактового импульса срабатьшает элемент 16, устанавливая три гер памяти третьего разряда 3 в единичное состояние, а триггеры памяти младших разрядов 1, 2 - в нулевое. Наличие связи с вы хода элемента И-НЕ 16 на выходы элементо И-НЕ 14, 17, 19, 22, 23 препятствует неправильной работе делителя. Аналогичным образом, с приходом пятого тактового импульса триггер памяти первого разряда 1 устанавливается в единичное состоя ние, с приходом шестого тактового импульса он возвращается в нулевое состояние, а в единичное состояние устанавливается триггер второго разряда 2. После окончания действия шестого тактового импульса на выходе элемента И-НЕ 22 появляется сигнал, равный логической единице. Поскольку на выходе элемента И-НЕ 21 - также сигнал, равный логической единице, с приходом седьмого тактового импульса срабатывает элемент И-Н 15, устанавливая триггер памяти четвертого разряда 4 в единичное состояние, а триггеры памяти остальных разрядов - в нулевое состо ние. Далее счет продолжается аналогичным об разом до тех пор, пока после прихода одиннадцатого тактового импульса в делителе не установится код 1100. При этом на выходах элементов И-НЕ 21 и 13 появляется логическая единица. С приводом двенадцатого тактового импульса элемент И-НЕ 4 устанавливает делитель в исходное состояние. Формула изобретения Делитель частоты импульсов на двенадцать, содержащий три межразрядных элемента И-НЕ четыре разряда, каждый из которых состоит из триггера памяти и коммутационного триггера, выполненных на элементах И-НЕ, причем в первых двух разрядах единичный выход триггера памяти соединен с единичным входом коммутационного триггера, единичный выход которого соединен со входом первого межразрядного элемента И-НЕ, а нулевой выход соединен с единичным входом триггера памяти, единичный выход коммутационного триг1106гера третьего разряда и нулевой выход коммутационного триггера второго разряда соединены с нулевыми входами коммутационных триггеров, триггеров памяти и со входами межразрядных элементов И-НЕ всех предыдущих разрядов, нулевой выход коммутационного триггера третьего разряр.а соединен с единичным входом триггера памяти этого разряда, с нулевыми входами триггергав памяти и коммутационных триггеров всех предьвдущих разрядов, а та1сже со входом второго межразрядного элемента И-НЕ, нулевой выход триггера памяти четвертого разряда соединен с нулевым входом коммутационного триггера этого же разряда, единичный выход которого соединен с нулевыми входами триггеров памяти первого, третьего и- четвертого разрядов, с нулевыми входами коммутацио1шых триггеров всех предьщущих разрядов и со входом третьего меж{Разрядного элемента И-НЕ, выход первого межразрядного элемента И-НЕ соединен с нулевым входом коммутационного триггера второго разряда, выход второго межразрядного элемента И-НЕ соединен с обоими входами коммутационного триггера третьего разряда, а выход третьего межразрядного элемента И-НЕ соединен с единичным входом коммутационного триггера четвертого разряда, о тличающийся тем, что, с целью повышения его надежности, выход первого межразрядного элемента И-НЕ соединен с единичным входом коммутационного триггера третьего разряда, нулевой выход триггера памяти третьего разряда соединен со входом третьего межразрядного элемента И-НЕ, выход которого соединен с нулевым входом коммутационного триггера третьего разряда, единичный выход этого триггера соединен с единичным входом коммутационного триггера четвертого разряда, а нулевой выход - с единичными входами триггера памяти и коммутационного триггера четвертого разряда. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 506131, кл. Н 03 К 23/02, 14.02.74. 2. Авторское свидетельство СССР по заявке N 2424199/18-21, кл. Н 03 К 23/02, 03.12.76.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты на 5,5 | 1978 |

|

SU771880A1 |

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты импульсов на 10 | 1978 |

|

SU746943A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты следования импульсов | 1980 |

|

SU928657A2 |

| Делитель частоты следования импульсов | 1980 |

|

SU886248A2 |

Авторы

Даты

1980-05-05—Публикация

1977-10-05—Подача