Изобретение относится к автоматике и вычислительной технике. Делитель может быть использован в устройствах измерения временных интервалов, а также для деления последовательности входных импульсов на 5,5, Известны делители частоты, выполненные на триггерах с раздельными входами и элементах И-НЕ 1J и 2 . Первый из них содержит в каждом разряде триггер памяти и два коммутационных триггера. Основным недостатком этого устройства является большое количество оборудования, что ведет к увеличению габаритов, потребляемой мощности устрой ства. Кроме того, это устройство не позволяет осуществить деление входной последовательности импульсов на 5,5. Второй делитель частоты содержит четыре разряда, каждый из которых содержит триггер памяти, коммутационный триггер и элемент И-НЕ, причем в первых трех разрядах единичный выход триггера памяти соединен с единичным входом ком 1утационного триггера, единичный выход которого соединен с входом элемента И-НЕ, а нулевой выход соединен с единичным входом триггера памяти данного разряда, с нулевыми входами коммутационных триггеров и триггеров памяти всех -предыдущих разрядов и с входом элемента И-НЕ предыдущего разряда, в четвертом разряде нулевой выход триггера памяти соединен с единичным входом коммутационного триггера, нулевой выход которого соединен с нулевыми входами триггеров памяти третьего и четвертого разрядов и с нулевыми входами коммутационных триггеров второго и третьего разрядов, выход элемента И-НЕ первого разряда соединен с обоими входами коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда соединен с нулевым входом коммутационног9 триггера третьего разряда, выход элемента И-НЕ третьего разряда соединен с входом элемента И-НЕ четвертого разряда, выход которого соединен с входом элемента И-НЕ третьего разряда и с нулевыми входами всех триггеров. Недостатком этого устройства является низкая надежность, поскольку оно содержит большое количество логических элементов. Целью изобретения является повышение надежности работы устройства.

С этой целью в делитель частоты на 5,5 содержащий четыре разряда, каждый из которых состоит из коммутационного триггера, триггера памяти и элемента И-НЕ, причем в каждом из трех первых разрядов единичный выход триггера памяти соединен с единичньпи входом коммутационного триггера,единичный выход которого подключен к входу элемента И-НЕ/ а нулевой выход к единичному входу триггера памяти и к единичному входу коммутационного триггера своего разряда и к нулевому входу триггера памяти и входу элемента И-НЕ предыдущего разряда, в четвертом разряде нулевой выход триггера памяти соединен с единичным входом . коммутационного триггера, нулевой выход которого подключен к нулевым входам триггеров памяти третьего и четвертого разрядов и к нулевым входам коммутсщионных триггерюв второго и третьего разрядов, выход элемента И-НЕ первого разряда Соединен с входами коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда - с нулевым входом коммутационного триггера третьего разряда, выход элемента И-НЕ третьего разряда - с входом элемента И-НЕ четвертого разряда, выход которого подключен к входу элемента И-НЕ третьег разряда и к нулевым входам коммутационных триггеров и триггеров памяти всех разрядов, а нулевые входы коммутационных триггеров первого, второго и третьего разрядов и входы коммутационного триггера четвертого разряда соединены с входной шиной, введены дополнительные элементы И-НЕ Причем выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера четвертого разряда и с входом первого дополнительного элемента И-НЕ, выход элемента И-НЕ второго разряда - с входом элемента И-НЕ четвертого разряда, выход которого подключен к нулевому входу коммутационного триггера и к единичному входу триггера памяти четвертого разряда и к входу второго дополнительного элемента И-НЕ, другой Вход которого подключен к выходу первого дополнительного элемента И-НЕ, входы которого соединены с единичныг: ми выходами триггеров пг1мяти третьего и четвертого разрядов, нулевой выход коммутационного триггера третьго разряда соединен с нулевыми выходами коммутационного триггера и триг,гера памяти первого разряда, а нулевой выход коммутационного триггера четвертого разряда - с входами элементов И-НЕ первого и третьего разрядов и с единичными входами триггеров памяти первого и второго разрядо

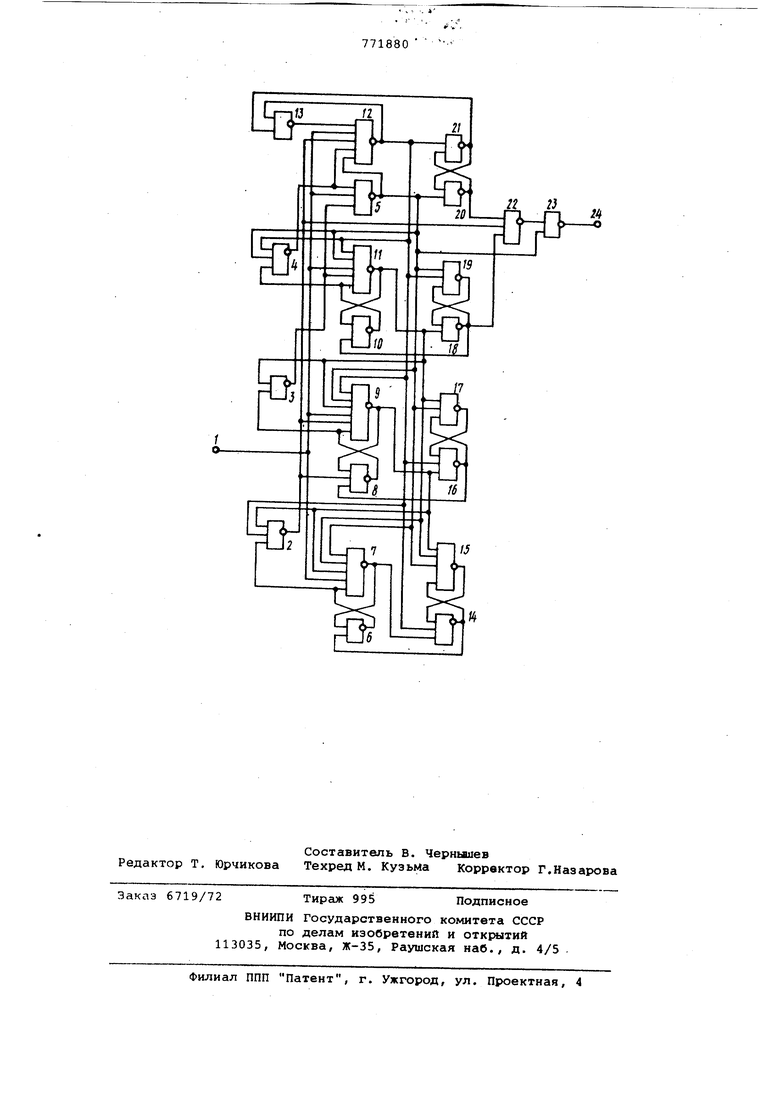

На чертеже представлена структурная электрическая схема делителя частоты на 5 ,5.

Делитель частоты на 5,5 содержит входную шину 1 тактового сигнала, элементы И-НЕ 2-5 соответственно первого - четвертого разрядов, элементы И-НЕ 6-13, попарно образующие комму тационные триггеры первого - четвертого разрядов, элементы И-НЕ 14-21, попарно образующие триггеры памяти этих разрядов, дополнительные элементы И-НЕ 22, 23.

Устройство работает следующим образом.

Под действием тактовых импульсов в делителе происходит двоичный пересчет поступающих импульсов, при этом осуществляется следующая последовательность смены состояний триггеров памяти делителя

0ООН

10100

20101

3ОНО

40111

51000

61001

71010

81011

91100

101101

11ООН

В исходном состоянии триггеры памяти первого и второго разрядов находятся в единичном состоянии, триггеры памяти остальных разрядов - в нулевом состоянии, а тактовый сигнал, поступающий на шину 1, отсутствует, равен логическому нулю. В этом случае на выходах элементов 2, 3, 5, 7, 9, 10, 11, 12, 14, 16, 19, 21,22 имеется логическая единица, на выходах остальных элементов - логический нуль.

С приходом первого тактового импульса срабатывает элемент И-НЕ 11, устанавливая триггер памяти третьего разряда в единичное состояние, а триггеры памяти младших разрядов в нулево Нсшичие связи с выхода элемента И-НЕ 11 на вход элементов 3, 7, 9, 10 препятствует появлению на выходах йтих элементов сигнала, равного логическому нулю, в момент действия тактового импульса.По окончании тактового импульса на выходах элементов 2 и 3 сигналы равны логическому нулю,поэтому с приходом второго тактового импульса срабатывает только элемент ИНЕ 7,устанавливая триггер пе1мяти первого в единицу.По окончании действия тактового импульса на выход элемента И-НЕ 8 появляется логическая единица.

С приходом третьего тактового импульса срабатывает элемент И-НЕ 9, устанавливая тригге памяти второго разряда в единицу, а триггер памяти первого разряда в ноль. Чтобы не сработал элемент И-НЕ 7 в момент действия тактового сигнала после того, как триггер памяти первого разряда /становится в ноль, а также для эбеспечения устойчивой работы элемен та И-НЕ 9 выход этого элемента соеди нен с входом элементов 2, 7, 8. С приходом четвертого тактовьго импульса срабатывает только элемент И-НЕ 7, поскольку на выходах элементов 2 и 3 имеются логические нули. По окончании действия четвертого тактового импульса на выходах элементов 2 и 3 появляются сигналы, равные логической единице, поэтому с приходом пятого тактового импульса срабатывает элемент И-НЕ 5, на его выходе появляется сигнал, равный логическому нулю, который через элемент И-НЕ 23 поступает на выходную шину 24 делителя и который устанавливает триггер пгиляти четвертого разряда в единичное состояние, а триггеры памяти всех младших раэрядов в нулевое состояние Далее аналогично в делителе осуществляется обычный двоичный пересчет до тех пор, пока с приходом десятого тактового импульса в нем не установит ся код 1101. По окончании десятого тактового импульса на выходе элемента И-НЕ 2 появляется сигнал, равный логической единице, что ведет к появлению на выходе элемента И-НЕ 22 сигнала, равного логическому нулю, который через элемент И-НЕ 23 поступает на выходную шину 24. С приходом один надцатого тактового импульса срабатывает элемент И-НЕ 12, устанавливая .триггеры памяти первого и второго раз рядов в единичное, а триггеры памяти третьего и четвертого разрядов в иу левое состояния, возвращая таким обравом делитель в исходное положение. Формула изобретения Делитель частоты на 5,5, содержащий четыре разряда, каждый из которых состоит из коммутационного триггера, триггера памяти и элемента И-НЕ причем в каждом из трех первых разрядов единичный выход триггера памяти соединен с единичным входом коммутациониого триггера, единичный выход которого подключен к входу элемента И-НЕ, а нулевой выход - к единичному входу триггера памяти и к единичному входу коммутационного триггера своего разряда и к нулевому входу тригге ра памяти и входу элемента И-НЕ предьщущего разряда, в четвертом разряде нулевой выход триггера памяти соединен с единичным входом-коммутационного триггера, нулевой выход которого подключен к нулевым входам триггеров памяти третьего и четвертого разрядов и к нулевым входс1м коммутационных триггеров второго и третьего разрядов, выход элемента И-НЕ первого разряда соединен с входами коммутационного триггера второго разряда, выход элемента И-НЕ второго разряда - с нулевым входом коммутационного триггера третьего разряда, выход элемента И-НЕ третьего разряда - с входом элемента И-НЕ четвертого разряда, выход которого подключен к входу элемента И-НЕ третьего разряда и к нулевым входам коммутационных триггеров и триггеров памяти всех разрядов , а нулевые входы коко утещнонных триггеров первого, второго и третьего разрядов и входы коммутационного триггера четвертого разряда соединены с входной шиной, отличающийся тем, что, с целью повышения надежности работы делителя, в него введены дополнительные элементы И-НЕ, причем выход элемента И-НЕ первого разряда соединен с нулевым входом коммутационного триггера четвертого разряда и с входом первого дополнительного элемента И-НЕ, выход элемента И-НЕ второго разряда - с входом элемента И-НЕ четвертого разряда, выход которого подключен к нулевому входу коммутационного триггера и к единичному входу триггера памяти четвертого разряда и к входу второго дополнительного элемента И-НЕ, другой вход которого подключен к выходу первого дополнительного элемента ИНЕ, входы которого соединены с единичными выходами триггеров памяти третьего и четвертого разрядов, нуле вой выход коммутационного триггера третьего разряда соединен с нулевыми выходгичш коммутационного триггера и триггера памяти первого разряда, а нулевой выход коммутационного триггера четвертого разряда - с входами элементов И-НЕ первого и третьего азрядов и с единичными входами триггеров памяти первого и второго разряов. Источники информации, ринятые во внимание при экспертизе 1.Авторское свидетельство СССР 444330, кл. Н 03 К 23/00, 1971. 2.Заявка I 2493135/18-21, кл. Н 03 К 23/02, 1977, по которой ринято решение о вьщаче авторского видетельства.

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на 44 | 1979 |

|

SU801256A1 |

| Делитель частоты следования импульсов | 1979 |

|

SU841124A1 |

| Делитель частоты импульсов на двенадцать | 1977 |

|

SU733110A1 |

| Делитель частоты следования импуль-COB HA 15 | 1979 |

|

SU818022A1 |

| Управляемый делитель частоты импульсов | 1977 |

|

SU736381A1 |

| Делитель частоты импульсов | 1979 |

|

SU843247A2 |

| Делитель частоты на четыре, пять | 1976 |

|

SU744996A1 |

| Делитель частоты следования импульсов на 5,5 | 1978 |

|

SU746945A1 |

| Делитель частоты на двенадцать | 1977 |

|

SU698131A1 |

| Двоичный счетчик | 1976 |

|

SU653747A2 |

Авторы

Даты

1980-10-15—Публикация

1978-10-05—Подача